Fターム[5J032AC16]の内容

Fターム[5J032AC16]に分類される特許

1 - 20 / 51

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

電子回路

【課題】 リセットに起因するディジタル回路の初期化時の誤動作の発生を減らす。

【解決手段】 電子回路において、ノイズ除去回路13は、パワーオンリセット信号などのリセット信号のノイズ除去を行い、ディジタル回路11は、ノイズ除去回路13によるノイズ除去後の信号でリセットされる。そして、早期有効化回路16は、そのリセット信号によるリセット状態が解除されるまでの期間、ディジタル回路11の出力信号を所定の値に固定する。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】ノイズや縮退故障等による意図しないリセット信号の解除を防止することが可能なリセット信号生成回路及びそれを備えた半導体集積回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路は、基準リセット信号RESETZを第1ノードに伝達するための信号線ROUT11と、基準リセット信号RESETZの反転信号を第2ノードに伝達するための信号線ROUTZ12と、第2ノードに伝達された信号の反転信号を出力するINV回路104と、第1ノードに伝達された信号の論理値と、INV回路104の出力信号の論理値と、が一致しない場合、基準リセット信号RESETZに関わらずリセット信号IN_RESZをアクティブにするAND回路105と、を備える。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

信号処理装置

【課題】従来よりもノイズに妨害されることなく入力信号から値を読み取る。

【解決手段】信号処理装置Aは、外部からデジタル信号dsを受信する入力端子1と、異なる複数のサンプリング周期を合わせてデジタル信号dsの値を読み取る入力信号読み取り部5とを具備する。

(もっと読む)

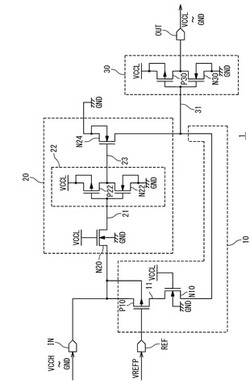

半導体装置

【課題】外部クロック信号CL、チップセレクト信号CE等の制御信号のノイズを適切に除去する。

【解決手段】半導体装置内部において生成される内部クロック信号ICLの立ち上がり及び立ち下がりのタイミングに同期して入力信号INの値を複数の異なるタイミングで保持する第1保持回路20及び第2保持回路22を備え、保持された値に応じて入力信号INのノイズを除去するノイズ除去回路を設ける。

(もっと読む)

センサ用サージ検出回路

【課題】チップ外のセンサから入力されるサージ電圧によるチップ内部の特性劣化を判定して、警告信号を出力するセンサ用サージ検出回路を提供する。

【解決手段】センサ用サージ検出回路は、入力回路11及び比較用入力回路22を有し、当該入力回路11及び比較用入力回路22が入力端子Tに接続される。入力回路11及び比較用入力回路22の出力信号は、レベル差検出回路23に入力される。レベル差検出回路23は、入力回路11と比較用入力回路22との出力信号のレベル差を検出し、その検出値を出力信号として制御部24に出力する。制御部24は、レベル差検出回路23からの出力信号に基づいて警告信号Aを出力する。

(もっと読む)

受信回路、受信方法及び受信回路を備える通信システム

【課題】従来の受信回路では、耐ノイズ性が低い問題があった。

【解決手段】本発明の受信回路の一態様は、送信回路Txとは異なる電源系において動作する受信回路Rxであって、送信回路Rxが絶縁素子ISOを介して出力する送信信号に基づき生成される受信信号Aの信号レベルの変化に応じて受信データDrx1の論理レベルを切り替える状態保持回路10と、受信データDrx1の論理レベルが切り替わる第1のタイミングから予め設定された第1の期間が経過するまでの期間において、状態保持回路10に受信データDrx1の論理レベルの保持を指示するホールド信号Dを生成する状態保持制御回路20と、を有する。

(もっと読む)

半導体回路及び半導体回路装置

【課題】 外部から瞬間的なパルスが入力されてもレジスタ等を復旧することが可能な半

導体回路及び半導体回路装置を提供する。

【解決手段】 外部と入出力情報を受け渡す端子部21aと、前記端子部21aの入力電

圧と、第1の参照電圧とを比較し、前記端子部21aの入力電圧が前記第1の参照電圧よ

り高い場合に、第1の信号を送信する第1のI/Oディテクタ部21bと、前記第1の信

号を受信した場合に、リセット信号を送信するリセット部24と、I/Oディテクタ部2

1bからの信号をラッチするラッチ部を具備することを特徴とする半導体回路。

(もっと読む)

電気回路

【課題】基板面積を拡大することなく高周波ノイズの伝播を抑制することができる、電気回路を提供すること。

【解決手段】電気回路1は、信号線2と、オープンコレクタを構成する出力端子3、出力線4、及びプルアップ抵抗5とを備え、出力線4は、信号線2に対して略平行に配設された平行区間と、当該平行区間から出力端子3に至る区間であって信号線2に対して略非平行に配設された非平行区間とを有し、プルアップ抵抗5の出力線4に対する接続点4aを、非平行区間に設けた。

(もっと読む)

半導体装置

【課題】従来技術において、制御回路に発生する電源ノイズを出力バッファに影響させないようにするには、出力バッファと制御回路の電源ラインを別々に設ける方法があった。しかし、この方法には、電源・グランドピン数の増加、給電ラインインダクタンスの増加といった問題があった。

【解決手段】本発明では、上記課題である(1)電源・グランドピン数増加と(2)給電ラインインダクタンスの増加を生じることなく、制御回路で問題となるノイズが出力バッファに回り込まないような技術を提供する。具体的な手法は、(A)制御回路用のオンチップバイパスキャパシタンスを設け、AC的に制御回路と出力バッファの給電経路を切り分ける方法、と(B)給電経路の電気パラメータノイズの振動モードが過減衰になるような設計(抵抗の挿入)をする方法がある。

(もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路

【課題】複数の電源の供給を受けて動作する信号処理回路においていずれの電源が供給されない場合にも回路の破壊を回避する信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路を提供する。

【解決手段】複数の電源の供給を受け、複数の電源により動作する通信端末装置200、データ変換部160,170,180への信号の供給を制御する信号供給制御部130,140,150は、複数の電源の少なくとも1つが供給されていない場合に、供給されていない電源とは異なる電源に起因する信号の通信端末装置200、データ変換部160,170,180への供給を制限する。

(もっと読む)

フリップフロップ、半導体集積回路、半導体デバイスおよびブレードサーバ

【課題】

回路オーバヘッドが小さく、かつ、ソフトエラーへの耐性が高い、高ソフトエラー耐性のフリップフロップおよび、それを用いた半導体集積回路を提供する

【解決手段】

ソフトエラーに対する耐性の異なる複数のラッチ回路と、前記複数のラッチ回路にクロックを供給するクロック分配部と、を備えたフリップフロップであって、前記複数のラッチ回路は、第一のラッチ回路と、前記第一のラッチ回路よりもソフトエラーに対する耐性の低い第二のラッチ回路の少なくとも2つのラッチ回路であることを特徴とするフリップフロップ。

(もっと読む)

入力回路および半導体集積回路

【課題】電磁波による誤動作を低減することのできる入力回路および半導体集積回路の提供を図る。

【解決手段】入力端子2に供給される入力信号を受け取る入力回路10aであって、一端が前記入力端子に接続された容量42と、前記入力信号を、当該入力信号と同じ正論理の信号に変換し、前記容量の他端に供給して駆動する容量駆動回路51,52,41と、を有するように構成する。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

ESD保護回路

【課題】電源投入時に急峻なスルーレートを持つ電圧波形が電源のノードに与えられた場合であっても、誤動作しないESD保護回路を提供する。

【解決手段】電源とグランドとの間の電圧差を検出する第1のトリガ回路と、第1のトリガ回路の出力信号が第1の閾値電圧に到達した時点で保持する第1のラッチ回路と、第1のラッチ回路の出力信号に応じて、電源とグランドとの間を導通させるか否かを制御する導通制御回路と、第1のトリガ回路の出力信号とグランドとの間の電圧差が第2の閾値電圧に到達したか否かを検出する第2のトリガ回路と、第2のトリガ回路の出力信号が第2の閾値電圧に到達した時点で保持する第2のラッチ回路と、第2のラッチ回路の出力信号に応じて、第1のラッチ回路の出力信号のレベルを制御する電圧制御回路とを備える。第1の閾値電圧は、通常動作時の電源電圧とグランドとの間の電圧に設定され、第2の閾値電圧は、通常動作時の電源電圧よりも大きい電圧に設定されている。

(もっと読む)

冗長化されたアナログ信号入力装置

【課題】異常信号を高速かつバンプレスに切り替えることができ、かつ入力信号がステップ状に変化し、また外乱が重畳しても切り替えが発生することがない冗長化されたアナログ信号入力装置を提供する。

【解決手段】入力信号の変化量が所定の値α以上になると異常であると判定し、異常な信号が1つ以上あり、異常でない信号があるときに、入力信号を切り替えるようにした。レベルでなく変化量で異常かどうかを判断するので、信号が異常になると即座に異常であると判定できる。そのため、高速かつバンプレスに信号を切り替えることができる。また、全ての信号の変化量が所定の値α以上になると切り替えないようにしたので、入力信号の元になっているプロセス量がステップ状に変化し、また外乱が重畳したときには、切り替えが発生しない。さらに、入力信号の変化量が所定の値αを越えると、一定期間切り替えをマスクするようにした。

(もっと読む)

半導体集積回路

【課題】複数のノイズパルスが連続して印加される場合においてもノイズを除去する能力を高めたノイズ除去回路を含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、入力信号を遅延する直列接続された複数の遅延回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理積を求めることによってセット信号を生成する第1の論理回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理和を求めることによってリセット信号を生成する第2の論理回路と、第1の論理回路によって生成されるセット信号によってセットされ、第2の論理回路によって生成されるリセット信号によってリセットされることにより、正論理の入力信号からパルス状のノイズが除去された出力信号を生成するRSラッチ回路とを具備する。

(もっと読む)

マイグレーション防止回路

【課題】電子機器や電気機器の印刷配線板におけるマイグレーションを防止する回路を提供する。

【解決手段】設定値保持用のスイッチ20,30と該スイッチ20,30の各端子に接続したアレイ抵抗器40との直列回路が直流電源に接続され、前記スイッチ20,30とアレイ抵抗器40との接続点がマイコン10の入力部に接続され、前記直流電源の前記直列回路への供給の有無を切り替えるトランジスタ50を備え、前記マイコンは前記スイッチ20,30が保持する設定値を読み出す際にのみ前記直流電源から前記直列回路への電源供給が行われるように前記トランジスタ50を制御する。

(もっと読む)

1 - 20 / 51

[ Back to top ]