Fターム[5J039DA04]の内容

パルスの操作 (9,993) | 比較要素 (410) | 電圧比較 (400) | BiTrによるもの (23) | 入力信号をトランジスタのベース又はエミッタに加え該トランジスタのエミッタ又はベースに接地電位とは異なる基準電圧を加えるもの (23) | 差動接続(エミッタ結合)された一対(2つ以上)のトランジスタを用いるもの (19)

Fターム[5J039DA04]の下位に属するFターム

負荷トランジスタが電流ミラー回路を構成するもの (5)

負荷TrのBとCがクロス接続

正帰還を持つもの (1)

Fターム[5J039DA04]に分類される特許

1 - 13 / 13

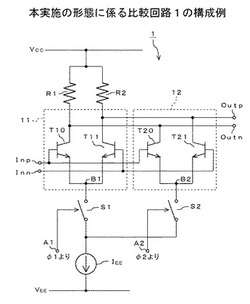

比較回路

【課題】比較回路の自己発熱を抑制して、自己発熱対策に起因する当該比較回路の動作速

度の低下を防止できるようにする。

【解決手段】差動増幅部11,12にスイッチS1,S2をそれぞれ接続させる。スイッ

チS1をONにして差動増幅部11を動作させるときには、スイッチS2をOFFにして

差動増幅部12を停止させ、スイッチS2をONにして差動増幅部12を動作させるとき

には、スイッチS1をOFFにして差動増幅部11を停止させる。この結果、スイッチS

1,S2によって差動増幅部11,12が交互に動作するので、差動増幅部11,12の

動作による自己発熱を抑制することができ、自己発熱対策に起因する比較回路1の動作速

度の低下を防止できる。

(もっと読む)

コンパレータ回路

【課題】ヒステリシス特性を持たせるための抵抗を短絡/開放するスイッチのオン抵抗変動による差動利得を削減する。

【解決手段】第1段の差動回路は、電源とアースの間に存する、直列接続されたR5およびTR7と、直列接続されたR6およびTR8と、その共通エミッタ接続点に接続された定電流源Ir9で構成される。第2段のエミッタフォロワ回路は、電源とアースの間に存する、直列接続されたTR10,R12および定電流源Ir16と、直列接続されたTR11,R18および定電流源Ir17で構成されて差動出力信号を出力する。SW13,SW14はR12の両端にそれぞれの一端が接続され、他端は次段回路の入力側に接続され、差動出力信号に基づいて排他的にオン/オフする。

(もっと読む)

コンパレータ回路および電子機器

【課題】 応答の遅れおよび誤動作が発生することなく暗電流を低減することができるコンパレータ回路および電子機器を提供する。

【解決手段】 入力レベル監視回路A30が、入力電圧が予め定める範囲内の電圧であると判定すると、トランジスタ304がオフになるので、インバータ312の出力がLOWレベルとなり、スイッチ回路313〜316はオフとなる。入力レベル監視回路A30が、入力電圧が予め定める範囲内の電圧でないと判定すると、トランジスタ304がオンになるので、インバータ312の出力がHIGHレベルとなり、スイッチ回路313〜316はオンとなる。コンパレータ回路1への入力信号の待機時状態での入力電圧を予め定める範囲内の電圧としておくことによって、スイッチ回路313〜316をオフにすることができ、待機状態であるときの暗電流を低減することができる

(もっと読む)

負荷電流を温度に依存して調節するための回路構成

【課題】負荷電流を温度に依存して調節するための回路構成を提供すること。

【解決手段】差動増幅器は、負荷電流ILを温度の関数として調節するために第1および第2のトランジスタ(Q1、Q2)を有し、回路構成(2)は、2つのトランジスタ(Q1、Q2)が同じコレクタ−エミッタ電圧UCE1、UCE2にて、および1とは異なるコレクタ静止電流IC1、IC2の一定比率にて動作するように設計され、それにより回路構成(2)は、半導体の物理的特性によって決まる温度電圧によって制御され、負荷電流ILを規定された形で温度の関数として調節する。さらに、このような回路構成(2)を備える自動車用ファン、および関連する方法に関する。

(もっと読む)

リミッタアンプ回路

【課題】良好な同相雑音耐性が得られ、入力信号に対する高速応答が可能なリミッタアンプ回路を提供する。

【解決手段】リミッタアンプ回路は、正相入力信号VIPと逆相入力信号VINとからなる差動形式の入力信号を増幅する差動増幅器2と、正相入力信号VIPの最大値と逆相入力信号VINの最大値との電圧差に応じた電流を、差動増幅器2の入力段に設けられた差動回路の1対の負荷抵抗24,25から引き抜くオフセット補償回路(AOC回路3)とを有する。

(もっと読む)

コンパレータ

【課題】入力電圧を出力する回路の電流量の変化を抑制し、回路規模の小さいコンパレータを提供する。

【解決手段】コンパレータは、入力電圧及び基準電圧が印加され、入力電圧と、基準電圧と異なる参照電圧とを比較するコンパレータであって、制御電極に入力電圧が印加される第1トランジスタと、第1トランジスタと直列に接続され、入力電圧が参照電圧と同レベルの場合に基準電圧と同レベルとなる、入力電圧に応じた比較電圧を生成する比較電圧生成回路と、制御電極に比較電圧が印加される第2トランジスタ及び制御電極に基準電圧が印加される第3トランジスタにより構成され、比較電圧及び基準電圧の大小関係に応じて動作する差動回路と、差動回路の動作に応じて、入力電圧及び参照電圧の比較結果を出力する出力回路と、を備える。

(もっと読む)

比較回路

【課題】 入力信号の変化速度に起因するオフセット電圧の発生を防止することが可能な比較回路を実現する。

【解決手段】 差動入出力の比較回路において、制御信号に基づき印加された差動の入力信号の極性を反転させて出力する第1の極性反転回路と、この第1の極性反転回路の差動の出力がそれぞれ印加される差動比較器と、制御信号に基づき差動比較器の差動出力の極性を反転させて差動の出力信号として出力する第2の極性反転回路と、第1及び第2の極性反転回路に差動比較器の入力部を構成するトランジスタの熱時定数よりも短い周期でランダムに極性を反転させる制御信号を供給する演算制御手段とを設ける。

(もっと読む)

電圧差比較回路

【課題】高速動作が可能で単純な構成の電圧差比較回路を低コストに提供する。

【解決手段】同一構成の各変換器11,12は、2つの入力信号の電圧差を電流値に変換し、その電流値を出力電流として出力する。変換器11は入力信号IN1,IN2の電圧差(IN1−IN2)を電流値に変換する。変換器12は基準電圧VREF1,VREF2の電圧差(VREF1−VREF2)を電流値に変換する。電流比較器13は、変換器11の出力電流が変換器12の出力電流よりも大きい場合(すなわち、電圧差(IN1−IN2)が電圧差(VREF1−VREF2)よりも高い場合)には出力信号OUTをハイレベルにし、変換器11の出力電流が変換器12の出力電流よりも小さい場合(すなわち、電圧差(IN1−IN2)が電圧差(VREF1−VREF2)よりも低い場合)には出力信号OUTをローレベルにする。

(もっと読む)

共鳴トンネルダイオードを有するコンパレータ

【解決手段】 コンパレータは、コンパレータのラッチ素子の抵抗(R301、R302)に直列な2つの共鳴トンネルダイオード(RTD、RTD301、RTD302)を用いる。2つのRTDダイオード(RTD301、RTD302)を抵抗(R301、R302)と直列に挿入することによって、第1、第2RTDダイオードの負抵抗が、抵抗およびラッチの実効的なRD時定数を減じて、コンパレータのラッチモードの間、別の設計によって実現される場合よりも高速の再生につながる。 (もっと読む)

比較回路

【課題】比較回路の入力端子に負電圧が印加されたときの出力信号の反転を防止する。

【解決手段】負電圧が印加される第1の入力端子(5)又は第2の入力端子(6)に接続された一方の主端子及び出力スイッチ(7)の制御端子に接続された他方の主端子を有する補償スイッチ(10)の制御端子をグラウンドに接続することにより、補償スイッチ(10)の何れかの主端子に接続された第1の入力端子(5)又は第2の入力端子(6)に負電圧が印加されたときに、補償スイッチ(10)がオンに切り換えられ、出力スイッチ(7)の制御端子がゼロボルト未満の負電位まで低下するので、出力スイッチ(7)をオフ状態に維持でき、出力スイッチ(7)は誤動作を発生しない。

(もっと読む)

コンパレータ

【課題】 回路規模を大幅に増加させることなく微小ヒステリシスを設定し得るコンパレータを提供する。

【解決手段】 コンパレータ20では、出力制御回路25からHiレベルの出力電圧Voutが出力された場合には、定電流供給回路27により、トランジスタQ3またはトランジスタQ4のうちのカレントミラー入力側トランジスタに所定の定電流I5が供給されるので、カレントミラー回路23に入力される差動出力がこの定電流I5のぶんだけ多くなる。これにより、カレント入力から電流を取り出すためのカレントミラー回路を必要とすることなく、微小ヒステリシスを可能にするので、回路規模を大幅に増加させることなく微小ヒステリシス特性を得ることができる。

(もっと読む)

コンパレ一タ回路

【課題】 スイッチングトランジスタにおける入力容量の低減、ゼロクロス周波数特性の向上を図り、高周波数の矩形波をサンプリングするコンパレータ回路(高周波トランジスタ回路)等の特性を改善する。

【解決手段】 プッシュプル回路40を構成するスイッチングトランジスタQ6と、前段のスイッチング回路30を構成する位相反転用トランジスタQ4のみを化合物半導体トランジスタで構成する。他のトランジスタの動作速度に限界があっても、充放電電流の減少やゼロクロス周波数の改善により、従来にない高速かつ高精度な動作(高周波数の矩形波のサンプリング等)が可能となる。

(もっと読む)

入力バイアス電流の相殺回路を有したバイポーラ差動入力段

入力バイアス電流相殺回路を有したバイポーラ差動入力段は、入力ペア(Q1、Q2)およびバイポーラのトラッキングトランジスタ(Q3)を含む。入力段は、入力ペア(Q1、Q2)およびトラッキングトランジスタ(Q3)中のコレクタ電流、ならびに入力ペア(Q1、Q2)およびトラッキングトランジスタ(Q3)のコレクタ・エミッタ電圧が、実質的に互いに等しい。ラテラルPNPトランジスタ(Q7)の第1のコレクタが、実質的に等しいコレクタ電流を得るために必要な、トラッキングトランジスタ(Q3)のベース電流を供給し、第2および第3のコレクタ(Q7)が、バイアス電流の相殺電流として、トラッキングトランジスタ(Q3)のベース電流のコピーを入力ペア(Q1、Q2)のベースに供給し、それによって、入力段の入力バイアス電流が減少される。  (もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]