Fターム[5J039DA12]の内容

パルスの操作 (9,993) | 比較要素 (410) | 電圧比較 (400) | 内部構成が記載されていない比較器(演算増幅器)を用いるもの (157) | 2入力型の比較器を用いるもの (152)

Fターム[5J039DA12]の下位に属するFターム

正帰還を持つもの (13)

Fターム[5J039DA12]に分類される特許

1 - 20 / 139

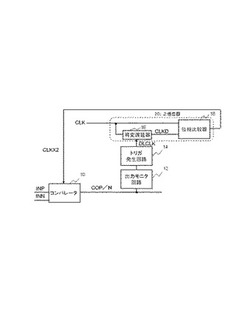

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

比較器、AD変換器、固体撮像装置、およびカメラシステム

【課題】一層のノイズ低減を図ることができることはもとより、低周波ノイズの低減を図ることができる比較器、AD変換器、固体撮像装置、およびカメラシステムを提供する。

【解決手段】比較器500Aは、第1の入力サンプリング容量C511と、第2の入力サンプリング容量C512と、出力ノードdと、一方の入力端子に、第1の入力サンプリング容量を介して、信号レベルが傾きをもって変化するスロープ信号を受け、他方の入力端子に、第2の入力サンプリング容量を介して入力信号を受けて、スロープ信号と入力信号との比較動作を行う差動比較部としてのトランスコンダクタンス(Gm)アンプ511と、Gmアンプの出力部cと出力ノードdとの間に配置され、Gmアンプの出力部の電圧を一定に保持するアイソレータ530とを有する。

(もっと読む)

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

オンダイターミネーション制御装置

【課題】較正正確度が改善されたオンダイターミネーション制御装置を提供する。

【解決手段】オンダイターミネーション抵抗値を外部抵抗値と同一に調整するオンダイターミネーション制御部と、第1パルス信号の活性化時にオンダイターミネーション制御部の出力電圧から比較器のオフセット電圧値を検出してキャパシタに保存し、第2パルス信号の活性化時にオフセット電圧値を相殺した後、出力電圧と既に設定された基準電圧とを比較して出力するオフセット補償部と、第3パルス信号の活性化時にオフセット補償部の出力を一定時間保存するラッチと、ラッチの出力をカウントしてコード信号を増加又は減少させるカウンタとを含み、オフセット補償部は、第2パルス信号の活性化時に保存されたオフセット電圧値を相殺して基準電圧と比較し、ラッチ及びカウンタは、第2パルス信号の活性化区間内において活性化状態に制御される第3パルス信号に応じて活性化制御される。

(もっと読む)

コンパレータ回路

【課題】プルアップ抵抗の抵抗値や接続する外部回路に依存せず、ハイレベル出力電圧を所望の電圧に精度よく設定することが可能なコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続されたプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がプルアップ抵抗RLの他端に電気的に接続され、非反転入力端子13にハイレベル出力電圧となる基準電圧V0が印加される増幅回路10と、を備えたものである。

(もっと読む)

コンパレータ回路

【課題】ローレベル出力電圧を0V、あるいは所望の電圧に精度よく設定でき、温度変化やプルアップ抵抗の抵抗値の変化によるローレベル出力電圧の変動が小さいコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続され、他端が正電源V+2に電気的に接続されるプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がコンパレータ2の出力段トランジスタ8のソース端子またはエミッタ端子に電気的に接続された反転増幅器10と、を備えたものである。

(もっと読む)

二値化回路

【課題】動作速度の低下を抑えつつ、ハイレベル及びローレベルの判定精度を高めることができる二値化回路を提供する。

【解決手段】二値化回路20は、ダイオード31及びコンデンサ32を有するピークホールド回路部30と、ダイオード41及びコンデンサ42を有するボトムホールド回路部40と、コンデンサ32とダイオード31との間のノードN1の電圧、及びコンデンサ42とダイオード41との間のノードN2の電圧の平均電圧VAと入力信号Vinの電圧とを比較して入力信号Vinを二値化する比較回路部70と、上記平均電圧VAに比例する電圧を出力する基準電圧生成回路部60とを備える。ボトムホールド回路部40は、基準電圧生成回路部60から出力された電圧を基準電位VSとして用いる。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

電圧検知回路および半導体装置

【課題】入力電圧範囲が上限基準電圧から下限基準電圧までの範囲であるか否かについては検知できるが、その範囲内において、どの電圧レベルであるかを検知することができない。

【解決手段】電圧検知回路は、上限値と下限値との間を周期的に変化する非方形波信号と、入力電圧とを比較し、前者が後者より大きいか後者が前者より大きいかを示す二値の電圧検知信号を出力するコンパレータ3と、前記電圧検知信号に含まれるパルスの幅を計測することにより前記入力電圧の電圧レベルを検出する検知部5とを備える。

(もっと読む)

抵抗分割回路及び電圧検出回路

【課題】スイッチ素子のオン抵抗の影響を排除することにより、トリミングの誤差が特定の条件において大きくなることを回避することができる抵抗分割回路、さらには精度がよい電圧検出回路を提供する。

【解決手段】直列接続した抵抗値に重み付けをした複数の抵抗素子と、抵抗素子とそれぞれ並列に接続されたスイッチ素子とを備えた抵抗分割回路で、対応する抵抗素子の抵抗値とスイッチ素子がショート状態のときの抵抗値との比を一定となるように構成した。

(もっと読む)

診断回路、発振回路

【課題】リファレンスクロックを要することなく発振信号の周波数範囲を診断できる、回路規模の小さな診断回路等を提供する。

【解決手段】制御信号102に応じて周波数が変化する発振信号166の周波数範囲を診断する診断回路10であって、制御信号102を受け取り、制御信号102に基づく値である比較値と所定の限界値とを比較する比較器を含み、比較器が比較した結果に基づいて診断出力値100を生成する。所定の限界値として上限値と下限値とを定め、比較値と上限値とを比較する上限比較器と、比較値と下限値とを比較する下限比較器とを含み、上限比較器および下限比較器が比較した結果に基づいて、診断出力値100を生成する。

(もっと読む)

コンパレータ、それを利用したスイッチングレギュレータの制御回路、スイッチングレギュレータ、電子機器

【課題】新規な出力論理を有するコンパレータを提供する。

【解決手段】コンパレータ100は、入力電圧VINを基準電圧VREFと比較する。差動増幅回路10は、その制御端子に基準電圧VREFが印加された第1入力トランジスタMi1と、その制御端子に入力電圧VINが印加された第2入力トランジスタMi2を含む。出力段20は、差動増幅回路10の出力信号Vxを受け、それに応じた信号を比較結果を示す出力信号SOUTとして出力する。フィードバック回路30は、出力段20の出力信号SOUTを受け、出力信号SOUTが第1レベルから第2レベルに遷移すると、出力信号SOUTが第2レベルに戻るように、差動増幅回路10または出力段20にフィードバックする。

(もっと読む)

比較装置

【課題】簡易な構成で複数の閾値を動的に選択することを可能にする。

【解決手段】比較装置100が、検知結果に応じて信号を出力するセンサ12、14と、複数の閾値Vrefを選択して出力する閾値選択部20と、センサ12、14が出力する信号と閾値選択部20が出力する閾値Vrefとを比較して、2値化された比較信号COMPを出力するコンパレータ30と、動作モードに応じた閾値Vrefを出力するように閾値選択部20を制御する制御部40と、制御部40の動作モードを切り替える動作モード切替部50とを備える。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

液晶駆動用のソースドライバのオフセットキャンセル出力回路

【課題】液晶駆動用のソースドライバのオフセットキャンセル出力回路を提供する。

【解決手段】基準電圧が非反転入力端に印加されたオペアンプと、反転入力端に各々の一端が接続された入力コンデンサ及び出力コンデンサと、反転入力端とオペアンプの出力端との間に接続された第1の電界効果トランジスタを有し、リセット動作時に入力コンデンサ及び出力コンデンサ各々にオフセット電圧を蓄電させ、通常出力動作時に入力コンデンサの他端に階調電圧を印加しかつ出力コンデンサの他端をオペアンプの出力端に接続するスイッチ素子回路と、を備え、リセット動作時及び通常出力動作時に第1の電界効果トランジスタの基盤に基準電圧に等しい第1の電位を印加し、通常出力動作中の階調電圧の切り替え時に第1の電界効果トランジスタのソース/ドレインから基盤に流れるリーク電流を防止するように基盤に第1の電位とは異なる第2の電位を第1の電位に代えて印加する。

(もっと読む)

車載機器用二値信号処理装置

【課題】車両側から車載機器に入力される二値信号の高レベル/低レベルの電位が未知の場合であっても、前記二値信号の2つの状態を正しく弁別し、高レベル及び低レベルの状態に応じてパルス状に変化する出力側二値信号を生成する。

【解決手段】入力側二値信号SG1の波形のアナログレベルをデジタル情報に変換して入力し、このデジタル情報から第1のレベル(高レベル)と第2のレベル(低レベル)とを検出し、前記第1のレベル及び第2のレベルに基づいて少なくとも1つの閾値を決定し、前記閾値に応じて基準レベル生成部の状態を自動的に調整するマイクロコンピュータ11と、前記基準レベル生成部に配置され前記マイクロコンピュータ11からのデジタル制御入力に従って抵抗値が決定される少なくとも1つのデジタルポテンショメータ16、17とを備える。

(もっと読む)

スケルチ回路

【課題】消費電流を低減しつつ、回路面積の縮小を図ることが可能なスケルチ回路を提供する。

【解決手段】差動入力される差動入力信号と閾値とを比較して、スケルチ信号を出力するスケルチ回路は、差動入力信号が入力され、前記差動入力信号と前記閾値とを比較して得られた第1のデジタル信号を出力する第1のコンパレータ回路を有する。また、デジタル回路で構成され、前記第1のコンパレータ回路の出力を平滑化し前記スケルチ信号として出力するデジタル平滑化回路を有する。また、第1のコンパレータ回路は、第1のクロック信号により動作が制御され、前記差動入力信号と前記閾値とを比較して得られた第1の差動比較信号を出力する第1のクロックト・コンパレータと第1の差動比較信号が入力され、前記第1の差動比較信号の論理を保持して前記第1のデジタル信号として出力する第1のデータ保持回路を有する。

(もっと読む)

ヒステリシスコンパレータ

【課題】ヒステリシスコンパレータの閾値の設定範囲を広げる。

【解決手段】一つの実施形態のヒステリシスコンパレータには、電流源2乃至4、比較増幅部10、基準電圧発生部21、カレントミラー回路23、Nch MOSトランジスタNMT3、Nch MOSトランジスタNMT4、Nch MOSトランジスタNMT6、Nch MOSトランジスタNMT8、Nch MOSトランジスタNMT9、端子Pvd、端子Pv1、端子Pin、端子Pvs、及び端子Poutが設けられる。

(もっと読む)

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

集積回路

【課題】単独の動作モード信号で動作モードを切り替えるコンパレータ回路において、コンペアモードでコンパレータ回路の出力値が確定した後も、入力部から出力部に向けて不要な電流が流れてしまう。

【解決手段】本発明の集積回路では、コンパレータ回路に、入力部および出力部の間の、リーク電流が通る電流パスに含まれるトランジスタを制御する論理回路を追加する。この論理回路は、動作モード信号と、コンパレータ回路の出力信号とを入力し、コンパレータ回路の出力信号が確定した後は電流パスを遮断状態にする。

(もっと読む)

1 - 20 / 139

[ Back to top ]