Fターム[5J039EE07]の内容

Fターム[5J039EE07]の下位に属するFターム

直列接続の出力段を持つもの (50)

並列駆動の出力段を持つもの (38)

Fターム[5J039EE07]に分類される特許

1 - 11 / 11

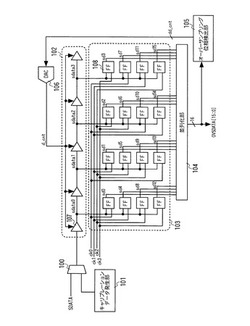

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

クロック設定回路および集積回路

【課題】 端子数を低減して集積回路のコストを低減可能とする。

【解決手段】 キャプチャー回路23は、入力端子14−1〜14−4に対する設定入力値SEL1〜SEL4をタイミングT1およびタイミングT2で読み取り、タイミングT1で読み取った設定入力値SEL1〜SEL4をクロック発生回路11に供給し、タイミングT2で読み取った設定入力値SEL1〜SEL4をクロック発生回路12に供給する。また、設定信号生成回路22は、タイミングT1とタイミングT2との間において設定入力値の取り得る値から設定入力値の取り得る別の値へ値が変化する設定信号SET0to1,SET1to0を生成し出力端子15−1,15−2にそれぞれ出力する。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

半導体設計装置

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システム

【課題】 集積回路の電源から放出されるノイズを効率良く低減することができる集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システムを提供すること。

【解決手段】 トランジスタが作動するときの貫通電流によって発生するIC1の電源ノイズを低減する集積回路電源ノイズ低減方法において、前記IC1のベースクロックに対して一定周期単位で位相を遅らせたディレイクロックを複数生成するクロック分散手順と、前記複数のディレイクロックにより動作する回路ブロックを複数の回路ブロック11,12,13,14に分割する回路ブロック分割手順と、各回路ブロック11,12,13,14により生成された位相のずれたノイズ波形と電源ノイズ波形を干渉させて電源ノイズを低減する電源ノイズ低減手順と、を有する。

(もっと読む)

クロックツリー回路

【課題】 消費電力の少ないクロックツリー回路を提供する。

【解決手段】 クロックツリー回路1を構成するクロックバッファ11〜14へは、専用のクロックバッファ用電源端子101から、一般回路用電源端子102から供給される電源電圧より低い電圧の電源電圧を供給する。ツリー末端のクロックバッファ14、15、16、17には、レベルシフタ31、32、33、34をそれぞれに接続する。

(もっと読む)

クロック分配回路

【課題】電源回路を簡素化し、小規模化することができるクロック分配回路を提供することを目的とする。

【解決手段】本発明に係るクロック分配回路は、入力されたクロックを分配するためのクロック分配回路12であって、クロックが入力される第1段のクロックバッファ122と、第1段のクロックバッファ122と直列に接続され、第1段のクロックバッファ122へのクロックの入力を制御する第1段のクロックマスク121と、第1段のクロックバッファ122に直列に接続され、第1段のクロックマスク121から出力されたクロックが入力される第2段のクロックバッファ124と、第1段のクロックバッファ122と第2段のクロックバッファ124とに直列に接続され、第2段のクロックバッファ124へのクロックの入力を制御する第2段のクロックマスク123とを備えたものである。

(もっと読む)

A/D変換回路

【課題】TAD方式のA/D変換回路において、パルス遅延回路を再起動するまでの待ち時間を短縮して高速な連続動作を可能とすること、更には、高速な連続動作を可能としつつ回路規模を削減すること。

【解決手段】A/D変換を実行する毎に、休止期間を挿入してパルス遅延回路10及び周回数カウンタ13を初期化するため、ラッチ&エンコーダ11及びラッチ回路14が出力する数値データをそのままA/D変換データとして使用することができる。また、パルス遅延回路10の起動,休止を制御する起動制御信号RR及び周回数カウンタ13を初期化するカウンタ初期化信号RCを生成する制御信号生成回路15は、遅延回路16と論理回路17〜19により構成されたエッジ検出回路からなり、サンプリングクロックCKSの周期より短い休止期間を設定できるため、高速な連続動作が可能となる。

(もっと読む)

半導体装置内信号分配経路の消費電力制御方法

【課題】 一つの信号を多数の使用箇所に小さなスキューで分配供給する場合、最初に予想される使用箇所数に十分な数を小さなスキューで分配供給できる信号分配経路を設計し、次にユーザ論理を設計する方法が広く知られている。

この時、予想した使用箇所数より実際の使用箇所数が少ない場合、使用されない分配用回路で無駄に電力が消費されるという問題があった。

【解決手段】

設計する信号分配経路で使用される分配用セルから、分配用回路を削減し消費電力を低減した分配用セルを作成する。ユーザ論理の配置位置を決定し使用箇所数が決定した後に、消費電力を低減した分配用セルに置換する。

(もっと読む)

1 - 11 / 11

[ Back to top ]