Fターム[5J039EE11]の内容

Fターム[5J039EE11]の下位に属するFターム

複数の比較器によるもの (1)

複数の遅延線によるもの (12)

Fターム[5J039EE11]に分類される特許

1 - 20 / 25

集積回路

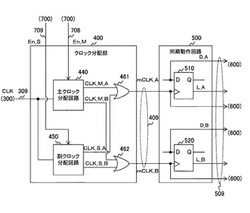

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路は、補間信号の位相を精度良く制御することができないという問題がった。

【解決手段】本発明にかかる多相クロック生成回路は、クロック信号1,2に基づいて、クロック信号1,2に対応する出力クロック信号間の位相を補間する補間信号を生成し、出力する位相補間回路102と、補間信号の位相を調整する第1の制御信号を生成し、位相補間回路102に対して出力する制御回路103aと、を備えた多相クロック生成回路であって、制御回路103aは、補間信号の論理値変化のタイミングを検出するためのタイミング検出回路104と、タイミング検出回路104の検出結果に応じた第1の制御信号を生成する制御信号生成回路105と、を備える。このような回路構成により、補間信号の位相を精度良く自動で制御することができる。

(もっと読む)

クロック供給システム及び画像形成装置

【課題】SSCGの変調度を大きくすることなく、且つ低コストで、複数の電子部品から放射されるノイズを効果的に低減する。

【解決手段】一定周波数の第1クロック信号を生成する第1クロック生成器と、前記第1クロック信号の周波数変調を行うことで周期的に周波数が変動する第2クロック信号を生成する第2クロック生成器と、複数のクロック供給対象回路で使用される前記第2クロック信号の位相が、前記クロック供給対象回路毎に異なるように位相調整を行う位相調整回路とによってクロック供給システムを構成する。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

データ受信装置

【課題】シリアルデータの各データにデータ幅の不均等や位相差があっても、サンプリングミスを防止することのできるデータ受信装置を提供する。

【解決手段】データ受信装置1は、多相クロック生成部11が、入力されたクロック信号CKから相互の位相差がT/7である7個のクロックC1〜C7を生成し、位相調整部21、22、23が、位相制御信号A、B、Cによる設定に応じてクロックC1〜C7の個々のクロックの位相を調整して、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7として出力し、シリアルパラレル変換部31、32、33が、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7により、入力されたシリアルデータA、B、Cをそれぞれサンプリングし、7ビットのパラレルデータA、B、Cに変換する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】半導体メモリ装置においてCMLレベルでスイングするクロックが伝送される経路を多重化することによって、動作モードに関わらず消費する電流量を常に最小に維持することのできる半導体メモリ装置を提供する。

【解決手段】本発明の半導体メモリ装置は、イネーブル信号に応答してCMLソースクロックがクロック伝送ラインを介して伝達された後にCMOSレベルでスイングするよう変換して出力する第1クロック伝達パスと、イネーブル信号に応答してソースクロックをCMOSレベルでスイングするよう変換した後にクロック伝送ラインを介して伝達されて出力する第2クロック伝達パスと、第1クロック伝達パス及び第2クロック伝達パスの出力クロックに応答してデータを出力するデータ出力手段と、を備える。

(もっと読む)

半導体集積回路装置及びクロックスキュー計測方法

【課題】クロックスキューをより正確に計測できる半導体集積回路装置及びクロックスキュー計測方法を提供する。

【解決手段】LSI100内部のクロック信号を入力するクロック入力端子1と、クロックスキューを計測するためのクロックスキュー計測信号を入力する計測信号入力端子2と、クロック信号とクロックスキュー計測信号とが入力される複数のF/F3と、計測信号入力端子2から複数のF/F3にクロックスキュー計測信号を分配する複数の計測信号分配ドライバ7と、を備え、複数のF/F3は、複数のF/F群5に分けられ、F/F群5内の全てのF/F3は、同一の計測信号分配ドライバ7と直接に信号線のみを介して接続され、複数のF/F3の出力信号に基づいて、複数のF/F3間におけるクロックスキューを計測するように構成した。

(もっと読む)

クロック伝搬回路

【課題】クロックスキューをより確実に抑制することが可能なクロック伝搬回路を提供する。

【解決手段】クロック伝搬回路10内のクロック伝搬ドライバ11及び12は、クロック停止制御信号SCSに応じてクロック信号CLKの伝搬を停止する。経時劣化検出回路20は、クロック伝搬ドライバ11及び12の内で動作状態にある一方のクロック伝搬ドライバ11から伝搬されたクロック信号CLKにより動作して自分自身の遅延劣化を検出する。動作状態切替部30は、経時劣化検出回路20による遅延劣化の検出に応じて、クロック伝搬ドライバ11に代えてクロック伝搬ドライバ12を動作状態とし、クロック信号CLKの論理回路ユニット2内の各回路への伝搬を継続する。

(もっと読む)

信号追跡を行う信号生成器

入力信号を追跡するように出力信号の周波数及び位相が調整される。前記出力信号が導き出される発振信号の周波数を制御するように制御信号が調整される。幾つかの側面においては、前記発振信号の前記周波数は、発振器回路に結合されたリアクティブ回路の再構成によって調整される。前記出力信号の位相は、前記発振信号と調整可能スレショルドの比較に基づいて調整することができる。例えば、前記調整可能スレショルドは、トランジスタ回路に関する調整可能バイアス信号を備えることができ、それにより、前記発振信号は、前記トランジスタ回路への入力として提供され、前記トランジスタ回路の前記出力は、前記出力信号を提供する。 (もっと読む)

半導体デバイスのためのクロック周波数調整

異なる平均クロック周波数を要求するデータ処理モジュールをクロック制御するための、及び、モジュール間でデータを転送するための方法及び装置が提供される。これは、共通クロック信号をモジュールに供給するための手段を含む。各々のモジュールにより要求されるクロッキング周波数に基づいて、共通クロック信号から個々のモジュールへのクロック・パルスが削除される。クロック・パルスは、データ転送と一致したときに、データが転送されるモジュールに適用される。 (もっと読む)

並列接続トランジスタ

【課題】配線のための面積増加なしに各トランジスタの入力信号の強度及び位相を均一にできる並列接続トランジスタを提供する。

【解決手段】並列接続トランジスタ50は、信号入力端子60に接続される伝送線路70、72と、伝送線路70及び72に沿って一列に配列されたトランジスタ84−1〜84−8及び88−1〜88−8と、伝送線路70、72に沿って一列に配列され、伝送線路70、72に一端が接続され、トランジスタ84−1〜84−8及び88−1〜88−8の対応する1つのベース端子に他端が接続された複数の容量素子82−1〜82−8及び86−1〜86−8とを含み、容量素子82−1〜82−8及び86−1〜86−8の容量値は、信号入力端子60からの伝送線路の線路長が大きいほど、小さくなっている。

(もっと読む)

LVDS受信装置、LVDS受信方法、LVDSデータ伝送システム、および半導体装置

【課題】スキューを検出すること無く、スキューや製造プロセスのばらつき、外因要素の影響を抑えた最適なストローブ信号を用いることにより、受信エラーを防止する。

【解決手段】シリアルデータおよびクロック信号を入力し、ストローブ信号に同期して上記シリアルデータをパラレルデータに変換するLVDS受信制御装置200であって、上記クロック信号に基づいて、位相が異なる複数のクロック信号を作成するPLL回路203と、製造プロセスのばらつき、および、外部負荷のうち少なくとも一方の情報を検出し、該検出した情報により、上記ストローブ信号を作成するための最適条件を特定する特性検出制御部210と、特性検出制御部210にて特定した最適条件に応じて、PLL回路203にて作成した複数のクロック信号から、上記ストローブ信号を作成するストローブ選択回路202とを備える。

(もっと読む)

クロック分配回路とテスト方法

【課題】メッシュ構造のクロック分配回路にて、各要素のインバータ(もしくはバッファ)の故障を検出可能とする。

【解決手段】最終段及び/又は中段の複数のバッファ出力が短絡されているクロック分配回路において、分岐点から分岐するパス上の同一段の、反転型バッファをなす複数のインバータ(a、b)、(c、d、e、f)に関して、次段のインバータ(c、d、e、f)、又は次の段のフリップフロップ(19)との接続をオン・オフするスイッチ(4、5)、(6、7、8、9)を、前記各インバータに対応して備え、観測用のフリップフロップ回路(16)、(17)を備えている。

(もっと読む)

減少された挿入遅延を持つプログラマブル遅延回路

【課題】クロック分配網内でクロック挿入遅延の平衡をとる。

【解決手段】プログラマブル遅延回路は、複数の遅延ブロック、複数の対応するトライステート・ドライバ、および少なくとも1つのデコーダを含む。トライステート・ドライバは、制御信号のうちの対応する1つに応じて、少なくとも第1のモード、および第2のモードのうちの一方で動作する。トライステート・ドライバの出力信号は第1のモードでは、入力電圧レベルの関数であり、第2のモードでは、高インピーダンス状態である。各トライステート・ドライバの出力は、一緒に結合され、プログラマブル遅延回路の出力を形成する。デコーダは、複数のトライステート・ドライバに接続される。デコーダは、少なくとも第2の信号を受け取るための少なくとも1つの制御入力を含み、第2の信号に応じて、トライステート・ドライバのうちの対応する1つを動作させるための制御信号を生成する。

(もっと読む)

クロックおよび電源グリッドスタンダードセルを用いたASICデザイン

【解決手段】 ASICソフトウエアデザインツールを用いて配列および配線することができる集積または統合された電源およびクロックグリッド。集積されたグリッドは、電源レールとクロックラインを含む、3つのタイプのグリッドユニットを含む。電源レールおよびクロックラインは、種々のグリッドユニットセルにおいて種々の配向を含む。 (もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

半導体集積回路のクロック構成方法およびそのプログラム

【課題】実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くする。

【解決手段】所定数のフリップ・フロップ(FF)を含む領域G1〜G8を2つの群に群分けする。このとき、境界線の横切るデータ接続経路の数が最小となるようにする。ここでは、データ接続経路A1、A2を横切るようにすると、境界線が横切るデータ接続経路数が2で最小となる。さらに、領域G1〜G4、領域G5〜G8を群分けした後に、クロックツリー合成(CTS)を行う。このようにしてクロック構成を行うことにより、実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くすることができる。

(もっと読む)

大規模半導体集積回路装置

【課題】各入力回路の位置に応じた適切な到達遅延時間を有する複数のクロックツリーを備えたことにより、動作周波数等の設計マージンが小さく、歩留まりの高い大規模半導体集積回路装置を提供することを目的とする。

【解決手段】同期回路を動作させるための基本クロックを発生させる原発振器と、CPUやメモリや特定用途用に構成されたロジック等を指す機能ブロックと、原発振器10で生成されるクロックを入力し、機能ブロックを駆動するクロックツリーと、機能ブロック間で情報の授受を行う非同期FIFO等で構成されるブロックである非同期I/Fブロック15と、を備えて構成し、各機能ブロックのLSI上の位置に応じて、クロックツリーの到達遅延時間を適切に設定する。

(もっと読む)

1 - 20 / 25

[ Back to top ]