Fターム[5J039HH09]の内容

パルスの操作 (9,993) | パターン監視(パルス列) (332) | 監視方法 (76)

Fターム[5J039HH09]の下位に属するFターム

監視用クロックを持つもの (41)

入力信号を遅延させるもの (12)

複数のパルス列を監視するもの (15)

Fターム[5J039HH09]に分類される特許

1 - 8 / 8

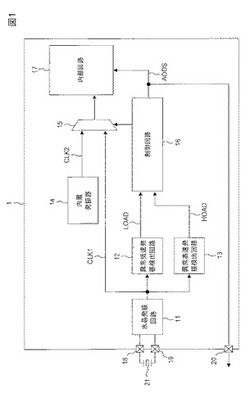

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

データ判定回路、受信器およびデータ判定方法

【課題】 データ判定回路の回路規模を大きくすることなく、孤立パルスを確実に検出する。

【解決手段】 閾値判定部は、2値データのデータ列を表すアナログデータ信号をオーバーサンプルすることにより生成されるデジタルコードを順に受け、負のデジタルコードが連続するときに増加値を示す閾値信号を出力し、正のデジタルコードが連続するときに減少値を示す閾値信号を出力する。孤立パルス判定部は、デジタルコードに閾値信号が示す値を加えて補正デジタルコードを生成し、連続する補正デジタルコードを用いて孤立パルスを検出する。バイナリ判定部は、連続するデジタルコードの符号を用いて2値データの論理を求める。データ選択部は、孤立パルスが検出されるときに、孤立パルスの論理を2値データの論理として出力し、孤立パルスが検出されないときに、バイナリ判定部により求められた2値データの論理を出力する。

(もっと読む)

電子回路、表示装置、及び電子機器、並びに電子回路の駆動方法。

【課題】順序回路の入力信号及び出力信号の状態を制御し、電子回路の動作不良を抑制する。

【解決手段】順序回路及び制御回路を有する電子回路であり、順序回路は、スタート信号として第1の信号、クロック信号として第2の信号、リセット信号として第3の信号が入力され、入力された第1の信号、第2の信号、及び第3の信号の状態に応じて設定された状態の第4の信号を出力信号として出力し、制御回路は、順序回路に入力される第3の信号の状態を制御する。

(もっと読む)

半導体集積回路装置

【課題】ユーザシステムに搭載された状態でクロック信号の異常検出機能の故障診断を可能とする。

【解決手段】第1クロック信号が正常の場合には第1クロック信号に基づいてシステムクロック信号を生成し、上記第1クロック信号が異常の場合には第2クロック信号に基づいてシステムクロック信号を生成するクロック発生部(10)を設ける。そして、演算処理を実行可能なCPU(2)と、上記外部発振器の状態を示す発振状態フラグに基づいて上記CPUに対する割り込み要求信号を形成可能なフラグ設定レジスタ部(9)とを設ける。上記フラグ設定レジスタ部は、疑似発振停止状態イネーブルビット保持部と、上記疑似発振停止状態イネーブルビットがイネーブル状態にされた場合に、上記割り込み要求信号をアサートする制御論理とを含む。上記割り込み要求信号がアサートされることで疑似的な発振停止状態を形成する。

(もっと読む)

電子回路、電子回路を備えた電子装置及び電子装置のパルス検出方法

【課題】回路が簡単で安定性が高い二乗検出回路。

【解決手段】入力端子101と、入力端子101から入力された信号から平衡信号と不平衡信号とを出力する平衡−不平衡変換器102と、ゲート端子に平衡信号が接続され、ソース端子が接地された第1の電界効果型トランジスタ103と、ゲート端子に不平衡信号が接続され、ソース端子が接地された第2の電界効果型トランジスタ104と、第1の電界効果型トランジスタ103のドレイン端子と第2の電界効果型トランジスタ104のドレイン端子とを相互に接続しドレイン電流を出力する出力端子112と、を含む電流出力部120と、電流出力部120の出力線113と接続され、電流出力部120から出力されるドレイン電流を加算した加算電流を出力する電流加算部121と、を含む電子回路1。

(もっと読む)

ステータス情報通信システム

【課題】自己診断装置が正常か異常かを判断する際に、ステータス情報発生用クロック信号が一時的に変化しただけでは、自己診断装置が異常であると判断したくない場合にも柔軟に対応できるステータス情報通信システムを得る。

【解決手段】自己の故障診断を行う自己診断装置に設け、自己の故障診断結果であるステータス情報として、正常時にクロック信号を出力し、異常時に前記クロック信号を停止させるステータス情報発生回路と、ステータス情報発生回路のクロック信号を正弦波に変換して出力するトランスと、トランスの出力する正弦波を整流する整流回路と、予め設定した閾値と整流回路の出力とを比較する比較器と、ステータス情報に基づく信号を受信する診断情報受信装置に設け、比較器の出力が入力され、自己診断装置が正常時か異常時かを認識するステータス情報受信回路とを備え、自己診断装置が正常か異常かを判定するものである。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路の発振出力に基づいて行われる所定の処理時間が一定となるように補正する構成を、より簡単に実現するマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振出力特性に基づき、通信回路により管理される1フレームのデータ送信時間を一定とするための通信レートCMRを決定するデータを記憶しておく。CPUは、温度検出回路によって検出される温度(ステップS2)に応じてEEPROMに記憶されているデータを読み出し(ステップS3)、決定した通信レートCMR(ステップS4)を通信回路に設定する(ステップS5)。

(もっと読む)

緊急動作機能を備えたステアリングコラム切換システム

ステアリングコラム切換システムの位置を検出して、ステアリングコラム切換システムが占める切換位置をビットパターンに変換するための機器と、その検知した位置のビットパターンを切換機能に割り付ける復号化機器と、そのビットパターンの検出又は伝送の際の誤りを検出するための機器とを備えており、その場合に、この復号化機器が、誤りを検知した場合に、ビットパターンと始動する切換機能の間の割付を変更する自動車用ステアリングコラム切換システムを記載する。 (もっと読む)

1 - 8 / 8

[ Back to top ]