Fターム[5J039HH10]の内容

パルスの操作 (9,993) | パターン監視(パルス列) (332) | 監視方法 (76) | 監視用クロックを持つもの (41)

Fターム[5J039HH10]の下位に属するFターム

Fターム[5J039HH10]に分類される特許

1 - 20 / 32

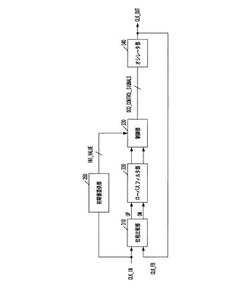

位相固定ループ及びその動作方法

【課題】位相固定ループのロッキングタイムを減らすことができる、特にターゲット値(出力クロックの目標周波数)が変化しても常に短いロッキングタイムを有する位相固定ループ及びその動作方法を提供する。

【解決手段】位相固定ループは、入力クロックCLK_INの位相とフィードバッククロックCLK_FBの位相とを比較する位相比較部310と、位相比較部310の比較結果UP,DNに応じて周波数制御信号DCO_CONTROL_SIGNALSを生成する制御部330と、周波数制御信号DCO_CONTROL_SIGNALSに応答して出力クロックCLK_OUTを生成するオシレータ部340と、入力クロックCLK_INの周波数を検出して、検出結果に応じて初期値INIT_VALUEを制御部330に提供する初期値提供部350とを備える。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

半導体装置及び位相検知回路

【課題】位相検知の誤判定を防止した高精度の位相検知回路を提供する。

【解決手段】電源線VSS1とセンスノードLSAT、LSAB間に、nMOSトランジスタの組(M1、M2、M3)、(M4、M5、M6)を備え、各トランジスタのゲートに内部クロックRCLK、RCLKのインバータINV1による反転信号、外部ロックCK、/CKをそれぞれ入力し、電源線VDD1とセンスノードLSAT、LSAB間に、pMOSトランジスタの組(MP1、MP2、MP3)、(MP4、MP5、MP6)を備え、各トランジスタのゲートにFCLKのインバータINV2による反転信号、内部クロックRCLK、外部ロックCK、/CKをそれぞれ入力し、センスノードLSAT、LSABは差動アンプAMPで増幅されラッチ回路L1でラッチされる。pMOSトランジスタ(MP11、MP12、MP13)はLSAT、LSABをプリチャージ・イコライズする。

(もっと読む)

ノイズキャンセラおよび画像形成装置

【課題】 異なる時間レンジにおける信号レベルおよび信号レベルの変化を同時に出力し、ノイズ周波数が状況に応じて変わる場合にも、ノイズキャンセルを効果的に行うことができるようにする。

【解決手段】 N進カウンタ群1は、N進カウンタ1−1〜1−Mを有し、各N進カウンタ1−iは、クロック信号を印加され、そのクロック信号の周期を増加させて出力する。また、レベル変化検知器群3は、レベル変化検知器3−1〜3−Mを有し、各レベル変化検知器3−iは、N進カウンタ1−iから出力される第1クロック信号Giの1周期ごとに入力信号Lei−1のレベルをサンプリングしサンプリング信号Leiを出力するとともに、第1クロック信号より周期の短い第2クロック信号Gi−1の1周期ごとに入力信号Lei−1のレベルを検出してレベル変化の有無を示すレベル変化状態信号Chiを出力する。

(もっと読む)

マイクロコンピュータ

【課題】外部発振機能で発生したクロックの発振周波数の異常を確認することができるマイクロコンピュータを提供すること。

【解決手段】本発明の一態様に係るマイクロコンピュータは、発振回路101、サンプリング回路103、サンプリングクロック回路106、異常確認回路107を備える。発振回路101は、CPUのクロック周波数の第1クロックを固定振動子により発生させる。サンプリングクロック回路106は、第1クロックより低い周波数の第2クロックを出力する。サンプリング回路103は、第2クロックを用いて第1クロックの周期をカウントし、第1クロックの発振が安定したか否かを判定し、CPUクロック供給許可信号を出力する。異常確認回路107は、第2クロックの周期をカウントすることにより決定される所定の期間内において、第1クロックの発振異常が発生したか否かを判定する。

(もっと読む)

半導体集積回路装置

【課題】従来のクロックゲーティング技術を採用した半導体集積回路装置では、スキャンテストに対応することができなかった。

【解決手段】本発明の半導体集積回路装置は、モード制御信号SMCに基づきスキャンデータSINと入力データDINとのいずれか一方の値を保持する複数のフリップフロップSFFa〜SFFcと、複数のフリップフロップSFFa〜SFFcのデータ入力端子及びデータ出力端子の値を監視してデータ転送状態を感知し、データ転送が行われている期間はクロック制御信号CCSaをイネーブル状態とするデータ転送感知回路32と、クロック制御信号CCSaに応じて複数のフリップフロップSFFa〜SFFcに対するクロック信号の供給を行うクロックゲーティング回路16と、モード制御信号SMCがイネーブル状態の期間にクロック制御信号CCSaをイネーブル状態とする動作モード判別回路と、を有する。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

クロックゲーティング回路

【課題】設計工数の増大を防止するために、簡単な回路構成で故障検出を可能にしたクロックゲーティング回路及びマクロセルを提供すること。

【解決手段】本発明に係るクロックゲーティング回路は、入力したクロック信号CLK12に対応するゲーテッドクロック信号GCLK13の出力をクロックイネーブル信号CEN10に応じて制御するクロックゲーティング回路である。また、CEN10の信号値をクロック信号CLK12に同期してラッチするラッチ5を有する。そして、CLK12を入力し、ラッチ5の出力信号に応じて、GCLK13の出力を制御するAND4を有する。さらに、ラッチ5の出力信号の信号値をクロック信号CLK12に同期してラッチし、ラッチした値を出力するラッチ6を備えることを特徴としている。それにより、簡単な回路構成でスキャン試験を実行することができる。

(もっと読む)

自動クロック切替回路および方法、ならびに電子機器

【課題】入力されたクロックが適切なものであるか常時監視することができ、クロックの切り替えを常時適切に行うことができるようにする。

【解決手段】判定回路10に固定クロックCLK1を常時入力する。判定回路10では、その常時入力される固定クロックCLK1に基づいて対象クロックCLK2の状態を監視し、対象クロックCLK2が入力停止状態にあるか、もしくは対象クロックCLK2の周波数が所定の周波数の範囲外にあるか否かを判断する。固定クロックCLK1を常時入力としているため、常にクロックの判定を行うことが可能であり、固定クロックCLK1から対象クロックCLK2へ、または対象クロックCLK2から固定クロックCLK1への切り替えが常時可能となる。また、対象クロックCLK2の入力停止状態から所望とするクロックの周波数範囲の判定まで、切れ目のない判定が可能となる。

(もっと読む)

半導体集積回路

【課題】 振動子型発振回路の発振停止を確実に検出し、発振停止を検出した際には確実に発振回路を再起動できる半導体集積回路を提供すること。

【解決手段】 半導体集積回路は、振動子によりメインクロック信号を生成する一つ以上のメイン発振回路と、メイン発振回路と独立し常に動作するリング発振器と、リング発振器の出力クロック信号を基準にメインクロック信号を監視してメイン発振回路の動作状態を判断するメインクロック検知回路と、メインクロック検知回路の検知結果に応じて、メイン発振回路を構成する素子の組み合せを変更する素子構成変更回路とを備える。

(もっと読む)

パルス検出装置及びパルス検出方法

【課題】パルス信号を高精度に検出すること。

【解決手段】パルス検出装置1は、所定期間に中間電位を含むパルス信号を検出する。また、パルス検出装置1は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定手段を備えている。さらに、信号固定手段は、パルス信号が入力される入力信号線に接続されたプルダウン抵抗9又はプルアップ抵抗であるのが好ましい。なお、パルス検出方法は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定工程を含んでいる。

(もっと読む)

デューティ比補正回路

【課題】デューティ比補正回路のデューティ比検知速度を固定せずに、必要に応じて調整することによって、速いデューティ比の補正が必要な場合はデューティ比検知速度を増加させ、必要でない場合はデューティ比検知速度を減少させるデューティ比補正回路を提供する。

【解決手段】検知速度制御信号によりデューティ比検知速度が調整され、クロックのデューティ比を検知して補正信号を出力するデューティ比検知部と、前記補正信号に応答して前記クロックのデューティ比を調整するデューティ比補正部とを備える。

(もっと読む)

デューティ補正装置

【課題】同一の符号化方式で符号化され、かつ伝送速度が任意の複数種存在する受信信号のいずれに対してもデューティ比を補正可能にする。

【解決手段】符号化された受信信号の“H”または“L”の継続時間を観測する観測手段と、受信信号の符号シンボル周期に関する長パルス用設定値と短パルス用設定値に基づいて、観測された“H”または“L”の継続時間から波形歪みを検出する波形歪み検出手段と、波形歪みが検出された場合に、波形歪み発生期間の受信信号を反転することにより波形の補正を行う波形補正手段と、受信信号の立上りまたは立下りを検出し、その次の立上りまたは立下り検出までの間隔に基づいて判定した現在の受信信号の符号シンボル周期に基づいて上記長パルス用設定値と短パルス用設定値を設定する符号シンボル周期判定手段を備えた。

(もっと読む)

半導体装置

【課題】 この発明は、テスト兼用端子に高電圧のノイズが入力された場合でも容易にテストモードに入ることのない半導体装置を提供する。

【解決手段】 この発明は、通常動作モードと、テストモードを備えた半導体装置において、前記半導体装置は、振幅が電源電圧以内の通常信号と振幅が前記電源電圧より高い高電圧信号の入力が可能なテスト兼用入力端子Aと、テスト兼用入力端子Aに入力される高電圧信号を検出する高電圧検出回路10と、高電圧検出回路10からの高電圧信号が所定のパターンで変化したことを検出するパターン検出回路20と、検出したテスト兼用入力端子Aから高電圧信号が所定のパターンで印加された場合に、前記通常動作モードから前記テストモードに切り換える切り替え手段30と、備えた。

(もっと読む)

電子回路、情報再生装置

【課題】 セットアップ違反に対するより一般的な検出技術を提供する。

【解決手段】 外部からの入力データを受ける第1のフリップフロップと、前記入力データを受けるラッチと、このラッチの出力と前記第1のフリップフロップの出力との排他的論理和を入力する第2のフリップフロップとを備えた電子回路。また前記第1のフリップフロップの出力を入力とし前記第2のフリップフロップの出力に基づく通知信号を抑制信号入力として用いる電子回路を具備した情報再生装置。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

多重系構成における異常発振検出回路

【課題】鉄道保安装置の安全側制御を行うために多重系構成であることを利用し、クロック発振器の高精度な異常発振検出、及び系間相互の状態監視を可能とした回路を提供する。

【解決手段】CPUボードの多重系構成における異常発振検出回路において、自系のカウンタを他系のクロックで動作させ、同様に他系のカウンタを自系のクロックで動作させることにより、相互のクロックの異常発振検出を可能にすることを特徴とする。

(もっと読む)

クロック異常検知回路

【課題】クロック信号の異常を精度良く検出することができるクロック異常検知回路を提供する。

【解決手段】クロック信号CKを検出してパルスを生成するパルス生成回路11と、電流源18から出力される電流を充電する充電回路13と、パルス生成回路11からのパルスによって、充電回路13に充電された電圧を放電する放電回路12と、充電回路13に充電された電圧を検知し、その電圧に応じた信号を出力する第1の電圧レベル検知回路15と、第1の電圧レベル検知回路15の出力に応じて制御された制御電圧を出力するピークホールド回路17と、充電回路13に充電された電圧を降圧し、降圧電圧を生成する電圧シフト回路14と、電圧シフト回路14により降圧された降圧電圧を検知する第2の電圧レベル検知回路16とを備える。ピークホールド回路17から出力された制御電圧に応じて電流源18は充電回路13に電流を出力する。

(もっと読む)

ディジタル・システムの信頼性を監視するシステム、およびその監視する方法

【課題】ディジタル・システムの信頼性またはエージングを継続的に監視し、ディジタル・システム動作が指定されたしきい値を超えて劣化する場合に警告信号を発行するシステムおよび方法を提供すること。

【解決手段】この技法は、ディジタル・システムに関連してリング・オシレータ・センサを実装することを含み、リング・オシレータ・センサの論理パーセント構成またはデバイス・パーセント構成あるいはその両方は、ディジタル・システム内のパーセント構成を再現する。カウンタ論理が、出力されるカウント信号を発振周波数に変換するためにリング・オシレータ・センサに結合され、制御論理が、リング・オシレータ・センサの発振周波数を周期的に評価し、(i)測定または推定された発振周波数が警告しきい周波数未満である、または(ii)測定された発振周波数の間の差の測定または推定された変化のレートが許容可能な変化のレートしきい値を超えるのうちの少なくとも1つである場合に、信頼性劣化を示す警告信号を生成するためにカウンタ論理に結合される。

(もっと読む)

クロック監視回路及びルビジウム原子発振器

【課題】互いに相手のクロックを監視することができるようにして、簡単な回路構成で確

実にクロック停止を監視することができるクロック監視回路を提供する。

【解決手段】このクロック監視回路60は、異なる発振源から発振された2つのクロック

CLK−A、CLK−Bの何れか1つのクロックが停止したことを検出するクロック監視

回路であって、各発振源から発振された夫々のクロックCLK−A、CLK−Bを計数す

るカウンタA、カウンタBと、各カウンタA、Bが所定の計数値を計数したことを検出す

る検出回路A、検出回路Bと、を備え、夫々のカウンタA、Bをリセットするリセット端

子Rには、当該カウンタを歩進させるクロック以外のクロックを接続するものである。例

えば、カウンタAのリセット端子Rには、CLK−Bを接続し、カウンタBのリセット端

子Rには、CLK−Aを接続する。

(もっと読む)

1 - 20 / 32

[ Back to top ]