Fターム[5J039KK14]の内容

Fターム[5J039KK14]に分類される特許

61 - 80 / 81

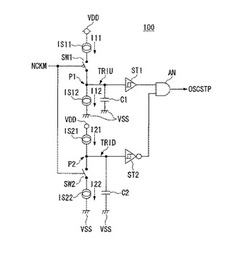

発振検知回路

【課題】トランジスタ特性のバラツキに影響されることなく、発振回路の発振を安定的に検知することが可能な発振検知回路を提供すること。

【解決手段】電源VDDとグランドVSSとの間に電流源IS11,IS12が直列に接続される。電流源IS11と電流源IS12との接続点P1にはコンデンサC1が接続され、この接続点P1に現れる信号を積分する。電流値の大きな電流源IS11と接続点P1との間にはスイッチSW1が設けられる。シュミットトリガーST1は、積分された信号を入力して2値信号を出力する。この2値信号は論理積回路ANに入力され、検知信号OSCSTPが出力される。ここで、発振回路の出力信号NCKMに基づきスイッチSW1が開閉すると、電流I11が断続的にコンデンサC1に供給される。この結果、接続点P1の信号レベルが上昇し、検知信号OSCSTPがハイレベルとなって発振が検知される。

(もっと読む)

コンパレータ回路およびその制御方法

【課題】比較入力信号の変化の傾きが小さな場合であっても、発振などせず安定した波形を出力し、比較入力信号の増減の方向に係わらず一定の閾値で比較入力信号の大小判定を行なうコンパレータ回路を提供する。

【解決手段】コンパレータ回路100は、比較入力信号INおよび参照入力信号REFの電位差に応じて充放電される容量素子4と、その電圧が閾値電圧Vth以上の場合にはハイレベルを出力し、閾値電圧Vth未満の場合にはローレベルを出力するアナログバッファ部5と、アナログバッファ部5の立ち上がりおよび立ち下がりエッジを検出してアップ信号UPおよびダウン信号DOWNを出力するエッジ検出部7と、アップ信号UPに応じて容量部を充電し、ダウン信号DOWNに応じて容量部を放電するチャージポンプ部8とを備えている。

(もっと読む)

状態検出回路及び発振停止検出装置

【課題】 従来の発振停止検出回路は、クロック信号が何ら停止していないにも拘わらず、通常用電源電圧及び予備用電源電圧の切り替えにより、瞬間的に、クロック信号が停止している旨が出力されるという問題があった。

【解決手段】 本発明に係る発振停止検出回路は、インバータ回路と、1段目、2段目のトランジスタと、第1、第2のコンデンサと、抵抗器と、相互に並列接続された第1、第2のトランジスタと、通常用電源電圧の入力及び予備用電源電圧の入力を選択的に受け、第1のトランジスタの入力端に、通常用電源電圧の入力を受けるとき定電圧を出力し、予備用電源電圧の入力を受けるとき予備用電源電圧を出力する定電圧生成回路とを含む。

(もっと読む)

スイッチ制御回路、ΔΣ変調回路、及びΔΣ変調型ADコンバータ

【課題】積分器の積分精度及びΔΣ変調回路の変調精度を向上させ、ΔΣ変調型ADコンバータにおける歪率劣化を抑制する。

【解決手段】第1〜第4スイッチを有するスイッチドキャパシタを用いて構成される積分器の前記第2及び第3スイッチと、前記第1及び第4スイッチとを相補的にオンオフするスイッチ制御回路であって、前記第1及び第4スイッチをオフ、前記第2及び第3スイッチをオンにする際には、前記第4スイッチをオフにする前に、前記第2スイッチをオンにする。

(もっと読む)

電子回路装置のEMI対策方法及び回路

【課題】 放射ノイズ低減とアナログ制御信号精度とのトレードオフ対策。

【解決手段】 システムコントローラーチップに供給する電源電圧にリップルを重畳することにより、動作クロックの周波数拡散を発生させて放射ノイズの低減を図る。システムチップから出力する信号の電圧安定化のために、チップ外部にゲートを設けて安定した電源で駆動する。

【選択図 】図1

(もっと読む)

タイミング感知用回路のための方法及びシステム

【課題】異なる駆動強度を提供しながら、実質的に等しい伝播遅延を有する回路に対するシステム及び方法を開示する。

【解決手段】これらシステム及び方法によって、回路は、随意選択的な強度のフル駆動強度回路において、ある比率の駆動強度を有する。さらに、これら回路は、ベースライン駆動回路に対して、実質的に同一の入力キャパシタンス及びフィードバック電流を有する。このような回路の入力は3つのノードに結合される。その1つは、駆動される論理装置に結合された論理回路であり、2つ目はダミー論理装置であり、3つ目は出力が浮遊状態に置かれている論理回路である。

(もっと読む)

ノイズ低減回路

【課題】 外部に高価なフレームメモリーを設けることなく雑音抑制を行うことができるノイズ低減回路を提供する。

【解決手段】 ノイズ低減回路は、複数の電荷蓄積手段2a〜2nと複数のスイッチ手段1a〜1nとを備えている。ノイズ成分を含む信号に応じた電荷量を複数の電荷蓄積手段2a〜2nに蓄積した後に、複数のスイッチ手段1a〜1nを導通させることによって複数の電荷蓄積手段2a〜2nを互いに並列に接続し、それによって、複数の電荷蓄積手段2a〜2nに蓄積されている電荷量を平均した電荷量と対応する信号を出力する。

(もっと読む)

積分回路とそれを利用するセンサ電圧処理回路

【課題】 積分回路において、出力電圧のうちの緩慢に変化する電圧が基準の電圧から大きく離れてしまうことを防止する。

【解決手段】 入力電圧Vaを電流に変換した電流で充放電するコンデンサ34を有する電荷蓄積回路30と、電荷蓄積回路30の出力電圧Voutから急速な電圧変化を除去して緩慢な電圧変化を抽出する緩慢変化抽出回路40と、緩慢変化抽出回路40で抽出された電圧が上下の限度値に達したのを合図に、前記コンデンサ34に蓄積されている電荷量を基準量に調整する調整回路50を備えていることを特徴とする積分回路80。

(もっと読む)

線形位相誤差検出に関する方法及び装置

【課題】超高速且つ高性能な線形位相誤差検出の方法及び検出回路を提供すること。

【解決手段】入力データ信号のエッジとクロック信号のエッジとの間の位相誤差を検出するために使用される方法及び装置を開示する。本発明は超高周波数において並びに線形位相誤差情報が必要な場合において使用される。本発明は任意の集積回路論理技術の利便性を拡張する。これにより周波数適用範囲が倍増するとともに、所望の線形位相誤差を測定する機能が維持される。クロッキング信号を用いてデータ入力信号のサンプリングを行うためにフリップフロップ回路が使用され、立ち上がりエッジのデータと立ち下がりエッジのデータに対して別個に処理が行われた後、両エッジからの位相誤差情報のアナログ式再合成が集積回路の速度による制限のない方法で行われる。

(もっと読む)

デューティ検出回路

【課題】 より広い周波数帯域で正常に動作することが可能なデューティ検出回路を提供する。

【解決手段】 デューティ検出回路100は、DLL回路よって生成される内部クロック信号であるRCLK信号及びFCLK信号を受け、この内部クロック信号のデューティ比に応じた電圧レベル(DB信号及びVREF信号)を生成する積分回路110と、積分回路110の出力を増幅するアンプ120と、アンプ120の出力をラッチするラッチ回路130と、各部の動作タイミングを制御するコントロール回路140と、積分回路110にBIAS信号を供給するバイアス回路150と、クロック信号の周波数をモニターする周波数モニター回路部160を備えている。周波数モニター回路部160は、電源投入時やリセット時などの初期設定時に使用される回路部分であり、クロック信号の実際の周波数を検出し、これに応じて積分回路110内のキャパシタC1〜C4の充電量又は放電量を調整する。

(もっと読む)

データスライサ

【課題】 データ受信中に同一符号が連続した場合でも、受信信号に応じた適正な閾値電圧を生成することができる直流電位補償回路を備えたデータスライサを提供する。

【解決手段】 出力信号OUTの変化時に直列接続したNMOS31,32に流れる貫通電流によって充電される容量34と、この容量34の電荷を放電させる抵抗35と、容量34の電圧から高周波成分を除去するLPF36とを有する調整回路30を設ける。LPF36の出力信号を調整電圧ADJとして可変時定数型の積分回路10に与え、ベースバンド信号の変化が多いときには時定数を減少させ、該ベースバンド信号の変化が少ないときには該時定数を増加させて、その時定数に従って入力信号INを積分して基準電圧S10を生成する。これにより、比較回路23では、入力信号INに応じて適正に生成された基準電圧に基づいて、出力信号OUTを出力することができる。

(もっと読む)

リモコン信号受信装置

【課題】スタンバイモードに遷移した状態における待機電力を大幅に削減でき、その状態で、リモコンからの入力信号の受信時にも効率よくノイズフィルタリングを行い、ノイズと信号を確実に区別し、リモコンのヘッダ波形を受信した場合のみ、正確にスタンバイモードから復帰できるリモコン信号受信装置を提供する。

【解決手段】リモコンからの入力信号を待機するスタンバイモード時に、リモコンからヘッダ信号が動作状態のアナログノイズフィルタ2に入力されると、このアナログノイズフィルタ2からの出力信号を、セレクタ4を通じてCPU5に入力するとともに、発振制御回路6を動作状態に移行させることにより、動作モードをスタンバイモードから通常モードに切り換えて、CPU5を動作状態に移行させるとともに、リモコンからの入力信号に対するノイズフィルタとしてアナログノイズフィルタ2からデジタルノイズフィルタ3を動作状態に移行する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の動作に起因するクロック信号の乱れを除去する。

【解決手段】 クロック信号CLKは、入力バッファ10で反転されてマスク信号S70と共にNAND20に与えられる。NAND20の信号S20が立ち上がると、積分部30,40の積分回路による遅延時間の後、この積分部40の信号S40が立ち下がる。信号S20は信号S40と共にNAND50に与えられるので、このNAND50の信号S50は、クロック信号CLKの立ち上がり時点から積分回路による遅延時間の間、“L”に固定される。信号S50は積分部60で遅延され、AND70で積分部60の遅延時間が追加されてマスク信号S70が生成される。一方、信号S50は、インバータ80で反転され、内部クロックCKIとしてデータ入力部1、データ処理部2及びデータ出力部3に供給される。

(もっと読む)

対称性時間/電圧変換回路

本発明は、時間/電圧変換回路に関し、前記時間/電圧変換回路は、構造的に互いに同一であり、その各々がそれぞれの論理制御信号UpおよびDwnを受ける入力部、ならびに論理制御信号VupおよびVdwnの継続時間を表す対応する電圧を与える出力部を有する2つの単純な時間/電圧変換器CTT1およびCTT2と、各々が当該単純な変換器CTT1およびCTT2に接続されている正302および負304の入力部ならびに2つの制御信号UpおよびDwnの間の電圧の差を表す信号Vdiffを与える出力部をもつ微分器ブロックBE2とを備える。微分器ブロックBE2からの出力Vdiffは、積分器ブロックBE3に接続されている。  (もっと読む)

(もっと読む)

ディジタルPWM手段

【課題】 簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現すること。

【解決手段】

2値以上を持つ信号を出力する手段であって、そのうちの1つの値が継続する時間と該値の繰り返す周期の比率が、入力信号に応じて変化するディジタルPWM手段であって、該値の繰り返す周期を固定しないで変化させることによって、簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現できる。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

シングルエンド・スイッチキャパシタ回路

【課題】シングルエンドの、非差動のスイッチキャパシタ回路に関して、同相雑音の影響を取り除くこと。

【解決手段】安定した、雑音のない同相電圧(Vcom)信号を発生するために、サンプリングキャパシタCsを用いて容量分配を形成する。形成されると直ちに、前記Vcom信号は、大きな同相容量Ccom間に結合され、Ccomはその値を更に制御するために望ましくは外部にある。その後、電圧Vcomは、データが分離される間に、安定させられうる。この方法で、電圧Vcom信号は回路に供給されない代わりに、必要とされる時に回路自体で雑音なく発生する。その後、発生したVcom信号は、非差動出力電圧Voutを発生するために、積分キャパシタC1に平行する。次に、サンプリングキャパシタCsはそれらを放電するために短絡され、処理が繰り返される。

(もっと読む)

車載用コンパレータ回路

【課題】 電源電圧の変動により誤パルスを出力することがない車載用コンパレータ回路を提供する。

【解決手段】 電源電圧Vcの変動に対して差動増幅器OP1からの出力が鈍化(鈍る)して変動しコンパレータCPの信号入力端子Csに加えられる。一方、コンパレータCPの基準電位入力端子Crに加えられる基準電位Vrefも波形鈍化回路20により鈍化(鈍る)して変動する。このため、コンパレータCPから誤パルスが出力されることが無くなる。

(もっと読む)

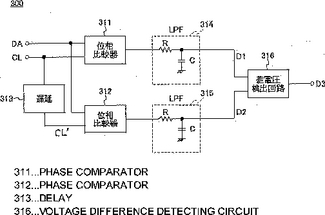

位相比較利得検出回路、誤同期検出回路及びPLL回路

PLLの位相比較利得検出回路において、データ信号DAとクロック信号CLとの間の位相を比較すると共に、データ信号DAとクロック信号CLを所定の遅延量だけ遅延したクロック信号CL’との間の位相を比較し、それぞれの位相比較結果どうしの差と上記所定の遅延量とに基づいて位相比較利得を検出する位相比較利得検出回路。  (もっと読む)

(もっと読む)

スイング低減信号回路のための適応ヒステリシス

差動入力信号を処理するための装置(50)。装置(50)は、差動入力(28)を有する最小ピーク検出器(51)を含む。ピーク検出器(51)は、ピーク検出器の差動入力(28)における平均電圧ピークに比例する第1の電圧を供給する。コンプレッサ(53)が、第2の電圧を供給するために第1の電圧を処理するように設けられている。コンプレッサ(53)の後に、第2の電圧によって調整可能なトリム電流を供給する電圧制御可能な電流源が続いている。トリム電流によってヒステリシス特性が調整可能なヒステリシス具備回路(67.1)は、装置(50)の一部である。  (もっと読む)

(もっと読む)

61 - 80 / 81

[ Back to top ]