Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

121 - 134 / 134

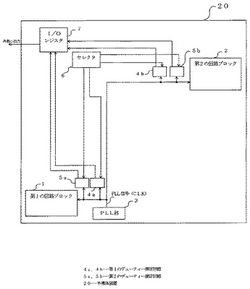

デューティ測定回路及びデューティ測定方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定する。

【解決手段】 半導体装置20には、第1の回路ブロック1、第2の回路ブロック2、PLL部3、第1のデューティ測定回路4a及び4b、第2のデューティ測定回路5a及び5b、セレクタ6、及びI/Oレジスタ7が設けられている。第1の回路ブロック1に隣接して設けられた第1のデューティ測定回路4aは、第1の回路ブロック1に入力されるPLL信号の“High”レベル期間(TH)を測定する。第1の回路ブロック1に隣接して設けられた第2のデューティ測定回路5aは、第1の回路ブロック1に入力されるPLL信号の“Low”レベル期間(TL)を測定する。測定されたPLL信号の“High”レベル期間(TH)及びPLL信号の“Low”レベル期間(TL)から、第1の回路ブロック1に入力されるPLL信号のデューティを高精度に算出できる。

(もっと読む)

パルス生成装置及びパルス生成方法

【課題】メモリ素子を用いて複数個のパルスを生成しうる多重パルス生成装置及びパルス生成方法を提供する。

【解決手段】複数個のパルス信号を生成するためのものであって、複数個の時間間隔信号及び第1選択信号を受信し、第1選択信号に応じて前記複数個の時間間隔信号のうち何れか一つを選択し、選択された時間間隔信号を出力する第1スイッチング部及び複数のパルス状態及び第2選択信号を受信し、第2選択信号によって前記複数のパルス状態のうち何れか一つを選択し、選択された時間間隔信号により決定される第1時間間隔の間に選択されたパルス状態を出力する第2スイッチング部を備えることを特徴とするパルス生成器。

(もっと読む)

リモコン信号受信装置

【課題】スタンバイモードに遷移した状態における待機電力を大幅に削減でき、その状態で、リモコンからの入力信号の受信時にも効率よくノイズフィルタリングを行い、ノイズと信号を確実に区別し、リモコンのヘッダ波形を受信した場合のみ、正確にスタンバイモードから復帰できるリモコン信号受信装置を提供する。

【解決手段】リモコンからの入力信号を待機するスタンバイモード時に、リモコンからヘッダ信号が動作状態のアナログノイズフィルタ2に入力されると、このアナログノイズフィルタ2からの出力信号を、セレクタ4を通じてCPU5に入力するとともに、発振制御回路6を動作状態に移行させることにより、動作モードをスタンバイモードから通常モードに切り換えて、CPU5を動作状態に移行させるとともに、リモコンからの入力信号に対するノイズフィルタとしてアナログノイズフィルタ2からデジタルノイズフィルタ3を動作状態に移行する。

(もっと読む)

クロック発生回路、信号多重化回路及び光送信器、並びに、クロック発生方法

【課題】 トグルフリップフロップ回路(TFF)を用いて分周クロック信号を発生させる場合に、初期状態が定まらないというTFFの本質的な問題に起因して、発生する各分周クロック信号間に位相ずれが生じてしまうのを回避しながら、4チャンネルよりも多くのチャンネル数のデータ信号の多重化を実現できるようにする。

【解決手段】 クロック発生回路であって、位相の異なる一対の分周クロック信号を出力しうる複数のトグルフリップフロップ回路TFF1,TFF2を直列に接続し、トグルフリップフロップ回路TFF2から出力される一対の分周クロック信号の一方又は両方をディレイさせて一対の分周クロック信号とは異なる位相のクロック信号として出力しうるディレイ回路DFF1を、トグルフリップフロップ回路TFF2に接続して構成される。

(もっと読む)

クロック信号出力回路

【課題】 電源電圧が変動する場合でも、逓倍クロック信号の出力精度を極力維持することができるクロック信号出力回路を提供する。

【解決手段】 周期カウンタ4では、基準クロック信号fsの周期をリングオシレータ1より出力される高速クロック信号frでカウントし、周期カウンタ24ではN分周された基準クロック信号fsの周期をN分周した高速クロック信号frでカウントする。そして、有効判定回路25は、周波数逓倍動作を開始した直後はマルチプレクサ26により周期カウンタ4側の周期データD1を選択して逓倍クロック信号fmを迅速に出力し、それ以降、周期カウンタ24によってカウントされた周期データD1’が有効になる時間が経過すると、当該周期データD1’を選択するようにマルチプレクサ26を切替えて周波数逓倍演算処理の対象とする。

(もっと読む)

コンパレータ切替え回路

【課題】 動作モードに応じて2つのコンパレータの動作状態を切替える場合でも、外部に対して不定レベルの信号が出力されることを確実に防止できるコンパレータ切替え回路を提供する。

【解決手段】 動作切替え回路11は、外部より送信される通信データを受信して二値レベル判定を行なうコンパレータ1,2の動作切替えを行なう場合、マイコン4が出力するモード切替え信号を遅延回路12を介して遅延させた信号を生成し、その遅延信号とモード切替え信号とをORゲート13及びANDゲート14で論理合成してハイレベル期間が異なるCOMP1,COMP2制御信号を生成すると、それらの制御信号により何れか1つのコンパレータ1,2が動作状態となっている期間を経て切替えを行う。また、マルチプレクサ3の選択切替えは遅延回路12の出力信号によって行う。

(もっと読む)

同期式ディジタルフィルタ

【課題】 装置の小型化を図り、しかも、クロック信号に同期し、且つ入力信号に重畳されたノイズを除去する。

【解決手段】 入力信号は第1フリップフロップF/F1の入力端D、正入力論理積回路AND1と負入力論理積回路AND2の第1入力端に供給される。第1フリップフロップF/F1の出力信号は、正入力論理積回路AND1と負入力論理積回路AND2の第2入力端に供給される。正入力論理積回路AND1と負入力論理積回路AND2の出力信号は、マルチプレクサMUXの選択信号端S1,S0に入力され、この選択信号でマルチプレクサMUXのデータ入力を切り替えて、マルチプレクサMUXの出力信号を第2フリップフロップF/F2に入力し、第1、第2フリップフロップF/F1,F/F2のクロック信号入力端CLKに供給される基準内部クロック信号発生部OSCからの内部クロック信号により第2フリップフロップF/F2に出力信号を得る。

(もっと読む)

SMD任意逓倍回路

【課題】

入力信号に同期し逓倍数が可変に設定される信号を出力する逓倍回路の提供。

【解決手段】

入力信号の周波数を可変に逓倍した出力信号を出力する逓倍回路であって、入力信号の周期を測定する周期測定用の遅延回路と、周期測定用の遅延回路で測定された周期に基づき、遅延時間が可変に設定され、遅延時間を再現する遅延再現用の遅延回路とを備えた同期遅延回路10と、同期遅延回路から出力される位相が異なる複数の信号を受けて多重化する多重回路20と、設定逓倍値にしたがって、周期測定用の遅延回路の遅延段数、遅延再現用の複数の遅延回路の段数の設定を可変に設定する制御回路30とを備え、多重回路20から入力信号に同期しその周波数を逓倍した出力信号が出力される。

(もっと読む)

ワイドレンジクロック発生器

第1のクロック発生回路と、周波数分割回路と、複数のマルチプレクサとを有する、ワイドレンジ複数位相クロック発生器である。第1のクロック発生回路は、それぞれが、第1の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第1のクロック信号を生成する。周波数分割回路は、第1のクロック発生回路から、複数の第1のクロック信号を受信して、第2の周波数および複数の異なる位相角のうちのそれぞれ1つをそれぞれが有する複数の第2のクロック信号を生成する。マルチプレクサは、それぞれが、第1のクロック信号のうちのそれぞれ1つを受信するように結合された第1の入力と、第2のクロック信号のうちの、第1のクロック信号のうちの前記1つと実質的に同じ位相角を有するそれぞれ1つを受信するように結合された第2の入力とを有する。  (もっと読む)

(もっと読む)

関連付けされていないリンクを介し信号を繰り返す機構

一実施例によるシステムが開示される。本システムは、第1集積回路(IC)と、第1ICに接続される第1インタフェースと、インタフェースに接続される第2ICとを有する。第1ICは、インタフェースに関連付けされていない複数の信号のそれぞれの状態を、当該状態の変化が検出される毎にインタフェースを介し第2ICにインバンドに送信する。 (もっと読む)

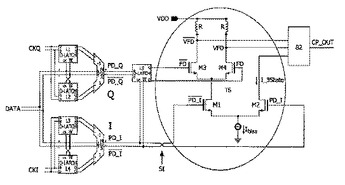

高速の位相周波数検出装置

本発明は、ランダムデータ用のタイミング情報を回復する回復回路用の検出装置およびチャージポンプ回路に関する。検出装置は、基準信号の直交成分を、入力信号に基づいてサンプリングし、第1のバイナリ信号を生成するための、第1のラッチ手段と、基準信号の同相成分を、入力信号に基づいてサンプリングし、第2のバイナリ信号を生成するための、第2のラッチ手段と、第1のバイナリ信号を、第2のバイナリ信号に基づいてサンプリングし、周波数誤差信号を生成するための、第3のラッチ手段と、を備える。よって、簡潔で速い検出回路が、デジタル実施に基づいて達成される。さらに、チャージポンプ回路は、差動入力回路と、差動入力回路のテール電流を、周波数検出装置の周波数ロック状態に応じて制御するための制御手段とを備える。これは、チャージポンプ回路の挙動が、検出装置によって生成される余分なリップルを低減できる、という利点を提供する。  (もっと読む)

(もっと読む)

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

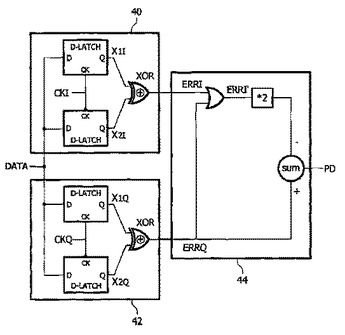

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

論理回路におけるクロック分配のための遅延マッチング

【課題】論理回路におけるクロック分配のための遅延マッチング。

【解決手段】論理回路内部に分配された複数の信号間の伝播遅延差を補正するための技術。遅延マッチング回路は、フロップによって生成された内部のクロックからQへの遅延を模倣する。遅延マッチング回路は、再分配されようとしている、クロック信号のような原初の信号の伝播経路内に置かれる。一般に、遅延マッチング回路は、特定の構成を有する伝播ゲート・マルチプレクサを含むことができる。遅延マッチング回路は、原初の信号の分割された版により経験されたクロックからQへの遅延に実質的に等しい遅延を課する。このようにして、遅延マッチング回路は、原初の信号と分割された信号の立ち上がり端と立ち下がり端とが、実質的に一致することを確実にし、同期した動作を可能にする。これゆえ、遅延マッチング回路は、再分配された信号と分割された信号を同期させることができる。

(もっと読む)

121 - 134 / 134

[ Back to top ]