Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

81 - 100 / 134

IQ信号発生器のためのスワップ機能を実施するためのシステム及び方法

【課題】IQ信号発生器に対してスワップ機能を実施するためのシステム及び方法を提供する。

【解決手段】IQ信号発生器を実施するためのシステム及び方法は、クロック入力信号に応答してI信号を発生するマスターラッチ、及び反転クロック入力信号に応答してQ信号を発生するスレーブラッチを含む。マスターセレクタが、マスターラッチからスレーブラッチへの通信経路を形成するように構成され、スレーブセレクタが、スレーブラッチからマスターラッチへのフィードバック経路を形成するように構成される。上述のI及びQ信号は、いかなる介在電子回路もなしにそれぞれマスター及びスレーブラッチから直接出力される。

(もっと読む)

パルス幅補正装置およびパルス幅補正方法

【課題】二値化のコンパレートレベルを調整することなく、データが誤って取り込まれるのを防止すること。

【解決手段】デューティー比検出回路3は、二値化信号DIのデューティー比の基準値からのずれを検出し、遅延回路5は、二値化信号DIを所定の遅延量だけ順次遅延させた遅延信号DLを生成し、セレクタ6は、デューティー比検出回路3にて検出された二値化信号DIのデューティー比のずれに対応した遅延信号DLnを遅延信号DLから選択し、パルス幅補正回路7は、セレクタ6にて選択された遅延信号DLnを用いることにより、二値化信号DIのパルス幅を補正する。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

半導体装置

【課題】半導体装置において、ユーザボードの違いや製造ばらつきがあっても、電源共振ノイズによる問題を回避することができる技術を提供する。

【解決手段】半導体装置内の電源ノイズを観測する電源ノイズ観測回路1と、電源ノイズ観測回路1の出力に基づいて、生成クロック301の周波数が変化するクロック生成回路2と、生成クロック301が入力される演算回路ブロック3と、を備える。そして、前記電源ノイズ観測回路1によって観測される電源ノイズが低減するように、生成クロック301の周波数が調整される。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

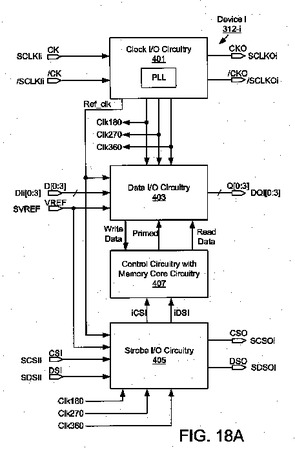

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】入力データとデータストローブクロックのタイミングにより自動的にデータ入力ストローブ信号の発生タイミングをチューニングする半導体記憶装置を提供する。

【解決手段】入力データとデータストローブクロックの入力タイミングによりデータ入力ストローブ信号の発生タイミングをチューニングする内部チューニング手段と、前記データ入力ストローブ信号に応答して、複数のデータをグローバルラインに伝送するデータ入力センスアンプとを含む。

(もっと読む)

ジッタ検出回路及びジッタ検出方法

【課題】PLL回路からの出力に含まれるジッタ成分及びデータパスの電源に含まれる周期的ノイズ成分を低減するクロック信号を生成する。

【解決手段】クロック信号120と変調制御信号127に基づいて生成された信号122とを混合して変調クロック信号123を生成するミキサ110と、遅延制御信号124に基づく遅延ステップで遅延された前記クロック信号若しくは前記変調クロック信号に同期したテストパターン信号と期待値データとが一致するか否かを判定し、判定結果を出力する内蔵自己テスト回路106と、前記判定結果をプロットしてシュムープロットを作成し、一致と不一致の境界線パターンに基づいて前記シュムープロットに含まれるノイズ成分を検出し、前記ノイズ成分と同じ周波数でかつ逆位相の信号を生成するように前記変調制御信号を出力する制御部107と、を備える。

(もっと読む)

プログラム可能な遅延を有するシーケンスが独立のオーバーラップしないディジタル信号発生器

【課題】オーバーラップしないクロック発生回路を提供する。

【解決手段】複数の遅延された基準クロック信号を生成するプログラム可能な遅延基準クロック信号回路と、プログラム可能な遅延基準クロック信号回路と動作可能に接続され、オーバーラップしないクロック信号を発生する複数の遅延クロック信号発生器とを含む。各遅延クロック信号発生器は、クロック信号の立ち上がりの遅延を制御し第1の信号を出力するラッチまたはフリップフロップと、遅延されたクロック信号の立ち下がりエッジの遅延を制御し第2の信号を出力するもう一つのラッチまたはフリップフロップと、第1および第2の信号からクロック信号を発生する論理回路とを含む。ラッチまたはフリップフロップは、複数の遅延された基準クロック信号の1つに応答してクロック信号の立ち上がりエッジの遅延を独立して制御する。

(もっと読む)

タイミング発生回路

【課題】

周期が一定であるかまたは変化し、一周期の間に少なくとも2つのレベルで遷移する処理対象信号の当該レベル遷移のタイミングを細かく設定できる回路技術を提供する。

【解決手段】

(A)第1周期信号、第2周期信号、・・・、第M周期信号をそれぞれ出力する周期信号発生回路11と、(B)第1〜第M周期信号を計数する第1〜第M計数回路からなる計数回路群12と、(C)前記所定タイミングの値を時間軸で配分して、前記所定タイミングの時間軸で配分した値を、第1周期信号の周期個数N1、第2周期信号の周期個数N2、・・・、第M周期信号の周期個数NMで表し、第1周期信号の周期個数N1を前記第1計数回路に、

第2周期信号の周期個数N2を前記第2計数回路に、

・・・

第M周期信号の周期個数NMを前記第M計数回路に、

セットする設定装置13とを備える。

(もっと読む)

電子回路装置

【課題】パルス幅を意図的に変化させるNRZ等の信号の伝送において、パルス幅のバラツキの低減を図り、さらにジッタの低減も図る。

【解決手段】2個のエッジ検出回路11,12と、2個の可変遅延回路13,14と、SRラッチ回路15とを備え、可変遅延回路13,14のそれぞれの入力にエッジ検出回路11,12の出力を接続し、SRラッチ回路のS入力およびR入力それぞれに可変遅延回路13,14の出力を接続する。前記SRラッチ回路15が、可変遅延回路13,14の出力のパルス終端側エッジを検出してセット/リセット動作を行う。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

異常検出回路

【課題】発振回路の停止検出などを行う異常検出回路を半導体集積回路で形成する場合に、抵抗素子や容量素子を半導体集積回路内に作成する必要がない上に、外付け部品として用意する必要がない異常検出回路の提供。

【解決手段】この発明は、発振回路の発振停止を検出するとともに、半導体集積回路内に形成される異常検出回路であって、容量素子C1と抵抗素子R1で構成される積分回路123を含んでいる。容量素子C1は、半導体集積回路の未使用のボンディングパッド24aに寄生する寄生容量を使用するようにした。抵抗素子R1は、MOSトランジスタを使用して、そのオン抵抗を利用するようにした。

(もっと読む)

メータ駆動回路

【課題】 ゲインリダクションメータとゲインメータに同じ構成のメータ駆動回路を使用しても、ゲインリダクションメータにおいて圧縮率の極小値を明確に認識できること。

【解決手段】 メータ駆動回路40は、入力されたエンベロープ信号を反転してエンベロープフォロワ部40bに入力することのできる第1の選択部SWaと、エンベロープフォロワ部40bの出力を反転してゲインリダクションメータに供給することのできる第2の選択部SWbを備えている。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

クロック同期システム及び半導体集積回路

【課題】クロック同期システムにおいて、LSIチップの大規模化・高集積化・高密度化に因る物理現象の複雑化に伴いギガ・ヘルツ級の高い周波数を持つ被分周クロックあるいは分周クロックをLSIチップ全面に渡り長距離配線を分配し且つシグナルインテグリティを確保することが困難である。

【解決手段】基準クロックに基づき逓倍クロックを生成する位相同期回路と、逓倍クロックに基づき分周クロックを生成する分周回路と、基準クロックを分周してフレームパルスを生成するフレームパルス生成回路とを備え、前記分周クロックは前記フレームパルスにより位相同期化がなされることを特徴とする。

(もっと読む)

クロック信号発生器

【課題】集積回路のクロック信号を柔軟に発生するためのクロック信号発生器を実現する。

【解決手段】集積回路のクロック信号を発生するためのクロック信号発生器(1)である。クロック信号発生器は、基準クロック信号に基づいて複数の相互に遅延したクロック位相を発生するようになった遅延同期ループ(3)を備える。遅延同期ループはさらに、第1の制御信号に応答して、複数のクロック位相のうち1つを、遅延同期ループ(3)の出力信号として選択するようになっており、この出力信号は第1のクロック信号である。クロック信号発生器はさらに、出力信号の逆を発生するように配置したインバータ(11)と、クロック反転信号に応答して、出力信号かまたは出力信号の逆かのいずれかを第2のクロック信号として転送するように配置したマルチプレクサユニット(12)とを備える。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路では、出力クロック信号に任意の周波数プロファイルを設定することができなかった。

【解決手段】本発明にかかる多相クロック生成回路1は、基準クロック信号に基づき多相クロック信号を生成する位相ロックループ回路10と、多相クロック信号の周波数プロファイルを保持し、開始信号に基づき周波数プロファイルの出力を開始し、基準クロック信号に基づき任意の周期で周波数プロファイルを更新する周波数プロファイル保持回路20と、周波数プロファイルに基づいて多相クロック信号のうち任意の位相のクロック信号を選択し、選択したクロック信号を位相ロックループ回路10に帰還させるクロック選択回路30とを有することを特徴とするものである。

(もっと読む)

フィルタ回路

【課題】単発ノイズを効果的に除去でき、かつ、比較的簡易な回路構成のフィルタ回路を提供すること。

【解決手段】1クロック前の出力データD_OUT(N−1)と、1クロック前の入力データD_IN(N−1)および2クロック前の入力データD_IN(N−2)の双方との差分絶対値S12,S14が、それぞれ減算器12,14にて算出される。セレクタ18によって、S12<S14のときには1クロック前の入力データD_IN(N−1)が現在の出力データD_OUT(N)となり、S12≧S14のときには2クロック前の入力データD_IN(N−2)が現在の出力データD_OUT(N)となる。

(もっと読む)

81 - 100 / 134

[ Back to top ]