Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

61 - 80 / 134

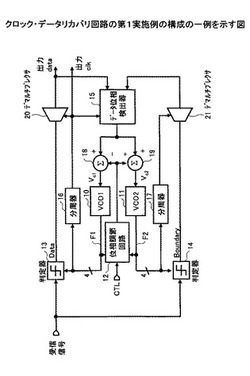

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

受信回路

【課題】消費電力を低減し誤動作の少ない受信回路を提供する。

【解決手段】プリアンブルを含む変調されたディジタル信号を受信する受信装置210と、検波回路220によるベースバンド信号S1と基準信号Vrefを比較するコンパレータ250と、ベースバンド信号S1の積分回路240と、積分回路240からの平均値信号S2に基づく信号S3を生成する下側ヒステリシス電圧生成回路260と、平均値信号S2に基づく信号S4/S5を生成する上側ヒステリシス電圧生成回路270と、コンパレータ250からのディジタル信号Doutに基づき、信号S3または信号S4/S5を選択しこれを基準信号Vrefとする選択回路280と、コンパレータ250からのディジタル信号のパルス数を計数し信号Qを出力するパルス検出カウンタ290と、信号Qに基づく信号S4/S5の電圧レベルを可変する電圧と、信号を処理するディジタル回路とを有する。

(もっと読む)

データ復元回路、データ復元方法、及びデータ受信装置

【課題】安定した動作を容易に実現することができるデータ復元回路を提供する。

【解決手段】データ復元回路は、データ列を表す入力アナログ信号をクロック信号に同期してアナログデジタル変換することにより、前記データ列のデータ間隔より短い間隔でサンプルしたデジタルコードの列を生成するアナログデジタル変換器と、前記デジタルコードが値を取り得る範囲の略中心にある所定のコード値の位置と前記デジタルコードの列を補間して得られる線分とが交差するクロス点の位置を前記デジタルコードの列から算出する位相検出器と、前記クロス点の位置に基づいて前記データ列のデータ中心点の推定位置を求める位相推定器と、前記クロス点の位置と前記データ中心点の推定位置とに基づいて前記デジタルコードの列からデータ判定値の列を抽出するデータ判定部とを含む。

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

受信回路、電子機器、及び受信回路の制御方法

【課題】 直前の数サイクルに依存して波形が劣化する信号に対して正しく受信することができない。

【解決手段】 本発明の受信回路10は、入力信号を基準電圧と比較して比較結果をハイレベル又はローレベルで出力する比較回路12と、比較回路12の出力レベルを次の1サイクル間保持する第1の記憶回路13と、第1の記憶回路13の出力レベルを次の1サイクル間保持する第2の記憶回路14と、第1の記憶回路13と第2の記憶回路14の出力レベルに応じて前記基準電圧のレベルをサイクル毎に制御する電圧制御回路11を有する。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出し、検出信号を欠落が発生している期間出力する検出回路102と、検出信号を受けた時点におけるFM信号の復調後の信号を保持するホールド回路40と、検出信号が出力されていない間はFM信号の復調後の信号を選択して出力し、検出信号が出力されている間はホールド回路40の出力を選択して出力するセレクタ回路42と、を備えるノイズキャンセラ部106を含む。

(もっと読む)

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出する検出回路102と、FM信号の復調後の信号に基づいて閾値を設定する閾値設定回路104と、を備えるFM信号のノイズ検出回路とする。

(もっと読む)

2値化回路と位相差判別装置

【課題】 入力電圧を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と第1出力端子26と第2出力端子28とピークホールド回路30とボトムホールド回路40と閾値演算回路50と第1比較回路60と第2比較回路70と第1選択回路80と第2選択回路90と第3選択回路100と第4選択回路110を備えている。第1選択回路80は2値化信号を出力し、第2選択回路90は遅れ2値化信号を出力する。ピークホールド回路30は遅れ2値化信号に基づいてピーク電圧を減少させ、ボトムホールド回路40は遅れ2値化信号に基づいてボトム電圧を増加させる。そのため、遅れ2値化信号を2値化信号に対して確実に遅延させることが可能となる。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

比較演算増幅回路、AD変換回路、電子機器

【課題】比較演算増幅回路やAD変換回路において、回路規模や消費電力のさらなる低減を図る。

【解決手段】サンプルホールド回路503では、複数のサンプルホールド回路と信号選択回路により、AD変換対象の差動アナログ信号対について、ホールドモード時の出力信号対を時分割で出力するようにする。フォールディング方式を採らないAD変換においては、比較演算増幅回路501は、時分割で供給される複数の出力信号対について、信号選択回路により複数の差動基準信号対を時分割で扱うように切り替えながら、各出力信号対と各差動基準信号対の差を各差動増幅回路で増幅することで複数の増幅出力信号対を時分割で出力するようにする。デジタルデータ取得部6は、時分割で供給される複数の増幅出力信号対の差をそれぞれ2値化することでデジタルデータを取得する。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】遅延固定ループで反映される遅延の程度を測定して読み出し命令に反映することにより、CASレイテンシに対応する最終出力イネーブル信号を生成することができる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置は、遅延固定ループ310と、外部クロック信号に同期化したロック完了情報に応答して基準クロック信号とフィードバッククロック信号との間の遅延の程度を測定し、これを遅延測定値として出力する遅延及び遅延時間測定手段330と、外部クロック信号に同期化した読み出し命令情報を、基準クロック信号とDLLクロック信号との間の遅延の程度に対応する分だけ遅延させ、遅延測定値及びCASレイテンシ情報に対応してDLLクロック信号に同期化させ、最終出力イネーブル信号として生成する出力イネーブル信号生成手段350と、を備える。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

半導体メモリ装置

【課題】メモリ装置のクロック分配網を改善することにより、クロックの特性を向上させること。

【解決手段】本発明に係る半導体メモリ装置は、外部クロックを受信してメモリ装置内に伝達するクロック供給部と、該クロック供給部から伝達されたクロックをメモリ装置内の各部に伝達するクロック伝達部と、該クロック伝達部から伝達されたクロックを用いてデータを出力する複数のデータ出力部とを備え、前記クロック供給部から前記クロック伝達部までにおける前記クロックが、CML(Current Mode Logic)レベルでスイングすることを特徴とする。

(もっと読む)

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

61 - 80 / 134

[ Back to top ]