Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

21 - 40 / 134

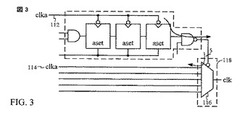

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

半導体集積回路

【課題】 原振クロック信号を通過させる場合の遅延時間と分周クロックを生成する場合の遅延時間を等しくするために、遅延時間の算出や遅延回路の調整を行う必要がない半導体集積回路を提供する。

【解決手段】 外部制御信号SEの論理値に基づいて、クロック信号CLKと外部入力信号SDの何れか一方を選択して内部入力信号S0とし、クロック信号CLKの立ち下がりで内部入力信号S0をラッチして第1内部出力信号S1を生成し、クロック信号CLKの立ち上がりで内部入力信号S0をラッチして第2内部出力信号S2を生成し、クロック信号CLKまたはクロック信号CLKの遅延信号を内部制御信号S3とし、内部制御信号S3の論理値に基づいて、第1内部出力信号S1または第2内部出力信号S2の何れか一方を選択出力し、選択された一方の内部出力信号は、当該選択期間中は信号レベルが変化しない。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

制御回路及びこれを用いたデータ保持装置

【課題】セットの部品点数削減や低消費電力化を実現することが可能な制御回路及びこれを用いたデータ保持装置を提供する。

【解決手段】制御回路10は、トリガ信号TRIGGERに特定の信号パターンが現れたときに制御部11の動作に必要な内部クロック信号LCLKの生成を開始し、少なくとも制御部11において所定の処理が完了するまで内部クロック信号LCLKの生成を継続した後、内部クロック信号LCLKの生成を停止する内部クロック生成部12と、内部クロック信号LCLKを用いて前記所定の処理を実行する制御部11と、を有する。

(もっと読む)

デジタル位相比較器およびこれを備えたデジタルPLL回路

【課題】デジタル位相比較器におけるスタートアップ時のキャリブレーションを不要とする。

【解決手段】基準信号を遅延させて遅延基準信号として出力し、遅延量に相当する時間差を有する遅延量信号を出力する手段と、遅延基準信号と発振器出力信号との時間差をデジタル値に変換し第1のデジタル値として出力する手段と、第1の時間量子化器で発生した時間残差を検出し、時間残差に応じた時間差を有する時間残差信号を出力する手段と、基準信号の状態に応じて時間残差信号を出力するか遅延量信号を出力するかを切り替える手段と、時間残差信号の時間差をデジタル値に変換して第2のデジタル値として出力し、遅延量信号の時間差をデジタル値に変換して第3のデジタル値として出力する手段と、第2のデジタル値および前記第3のデジタル値を用いて第1のデジタル値を補正することで小数位相を算出する手段と、を有する。

(もっと読む)

データ判定回路、受信器およびデータ判定方法

【課題】 データ判定回路の回路規模を大きくすることなく、孤立パルスを確実に検出する。

【解決手段】 閾値判定部は、2値データのデータ列を表すアナログデータ信号をオーバーサンプルすることにより生成されるデジタルコードを順に受け、負のデジタルコードが連続するときに増加値を示す閾値信号を出力し、正のデジタルコードが連続するときに減少値を示す閾値信号を出力する。孤立パルス判定部は、デジタルコードに閾値信号が示す値を加えて補正デジタルコードを生成し、連続する補正デジタルコードを用いて孤立パルスを検出する。バイナリ判定部は、連続するデジタルコードの符号を用いて2値データの論理を求める。データ選択部は、孤立パルスが検出されるときに、孤立パルスの論理を2値データの論理として出力し、孤立パルスが検出されないときに、バイナリ判定部により求められた2値データの論理を出力する。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

デジタル位相比較器及びデジタル位相同期回路

【課題】デジタル位相比較器の時間分解能を向上させつつ回路面積及び消費電力の増大を抑制する。

【解決手段】一実施形態によれば、デジタル位相比較器は、基準信号Refを初段から入力し、各段で遅延を与える遅延器列200を含む。デジタル位相比較器は、基準信号Refに応じてN相入力信号(Nは2以上の整数)のうちの信号CKV0をサンプルするサンプラ100−0と、遅延器列200の初段の出力信号に応じてN相入力信号のうち信号CKV0に比べて2π/Nだけ位相の遅れた信号CKV1をサンプルするサンプラとを含む、サンプラ群100を含む。デジタル位相比較器は、サンプラ群100のサンプル信号に基づいて、基準信号Refと信号CKV0との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路300を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

多相クロック生成回路

【課題】N相から2N相に切り替わったときに位相関係が不適切にならないようにする。

【解決手段】多相クロック生成回路は,基準クロックに同期して0°,90°の位相の中間クロックを生成する第1の分周器と,0°の中間クロックに同期して0°,90°の位相の第1群の出力クロックを生成する第2の分周器と,90°の中間クロックに同期して45°,135°の位相の第2群の出力クロックを生成する第3の分周器と,第1の分周器と第3の分周器との間に設けられ,切替信号に応じて,90°の中間クロックまたは固定値のいずれかを第3の分周器に供給するセレクタとを有する。さらに,切替信号が2N相モードのときに,第1群の出力クロックと第2群の出力クロックの位相関係にエラーがあるか否かを検出するエラー検出回路と,エラー検出回路がエラーを検出したときに基準クロックと非同期のタイミングで2N相モードの切替信号をセレクタに出力する再リセット回路とを有する。

(もっと読む)

ポップ音のしないスイッチ

【課題】スイッチに関し、より具体的には、2つ以上の入力の間でスイッチを切り換える際にポップ音等の好ましくない効果を低減できる方法及び装置を提供する。

【解決手段】スイッチ130は、第1の入力110で第1の信号を受取り、そのスイッチ130の状態により、出力120において出力信号を供給することができるように構成される。スイッチ状態変化は、現在のスイッチ状態とは異なる、要求されたスイッチ状態の指示115が受取られ、その第1の信号がしきい値に達するまで、遅らせることが可能である。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

信号処理装置および試験装置

【課題】制御チップに占める制御回路の面積を低減し、且つ、制御信号を出力する出力部の数を低減しつつ、複数の命令信号の処理時間の増大を抑制する。

【解決手段】複数チャネルの被制御回路を制御する制御信号を生成する信号処理装置であって、それぞれの被制御回路に対する命令信号を共通の入力部で受け取り、受け取った命令信号に応じて制御信号を生成し、それぞれの被制御回路への制御信号を共通の出力部から出力する制御チップと、制御チップが出力するそれぞれの制御信号を、対応する被制御回路に分配する分配回路とを備える信号処理装置を提供する。

(もっと読む)

データ伝送回路及び伝送方法並びにデータ伝送回路を備えるメモリ装置

【課題】データを伝送するデータ伝送回路を提供すること。

【解決手段】データを第1のラインに駆動する第1のドライバと、前記第1のラインに伝達されたデータのパターンを変更するパターン変更部と、該パターン変更部によってパターンが変更されたデータを第2のラインに駆動する第2のドライバと、前記第2のラインに伝達されたデータのパターンを元通りに復元するパターン復元部とを備えることを特徴とする。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

半導体集積回路

【課題】回路規模を増大させることなく、高速テストを実施することが可能な半導体集積回路を提供する。

【解決手段】本発明にかかる半導体集積回路は、複数のメモリセルによって構成されるメモリセル部22と、メモリセルへのデータの書き込み及び読み出しを制御する制御部と、クロックCLKに応じて制御部へ入力されるパルス信号を生成するパルス信号生成部と、を備える。そして、パルス信号生成部は、ワンショットパルス生成回路20を有する。ワンショットパルス生成回路20は、通常動作モード時には、クロックCLKに同期したワンショットパルス信号をパルス信号として生成し、高速動作モード時には、クロックCLK及びパルス信号に同期した連続したワンショットパルス信号をパルス信号として生成する。

(もっと読む)

21 - 40 / 134

[ Back to top ]