Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

41 - 60 / 134

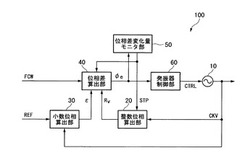

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

クロック発生回路及びその制御方法

【課題】従来技術のクロック発生回路は、クロックの周波数の切り替え時において、電流変動を抑制することができないという問題があった。

【解決手段】本発明にかかるクロック発生回路は、第1の周波数を有するクロック信号を第1の周波数よりも周波数が高い第2の周波数に切り替え可能なクロック発生部と、クロック信号のクロックパルスを所定の間引き率でマスクする間欠クロック生成部と、を有する。そして、間欠クロック生成部は、クロック信号の周波数が第1の周波数から第2の周波数に切り替わる場合に、第2の周波数に切り替わる時点から所定の期間、第2の周波数を有するクロック信号のクロックパルスを所定の間引き率でマスクすることを特徴とする。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

擬似ランダム信号発生装置、通信システム、及び画像形成システム

【課題】放射ノイズを低減する。

【解決手段】N段のDフリップフロップ(DFF)を備え、隣り合う前段のDFFの非反転端子が隣り合う後段のDFFの入力端子に接続され、最終段のDFFの非反転端子及び最終段以外の1つの段のDFFの非反転端子がEXORを介して最初の段のDFFの入力端子に接続され、最終段のDFFの非反転端子から2N−1ビットのビットパターンを繰り返したパターン信号を出力するパターン信号出力回路10、パターン信号が2N−1ビット出力される毎にビットパターン長を示す信号を出力するビットパターン長カウント回路12、ビットパターン長を示す信号に基づきパターン信号出力回路10の非反転端子及び反転端子から複数の端子を複数個ずつ繰り返し選択するための選択信号を出力するM進カウンタ回路14、及び選択信号に応じて該複数の端子から出力された信号を選択し、選択した信号を擬似ランダム信号として出力するタップ出力シフト回路16を含む。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

雑音除去回路及び雑音除去回路を備えた半導体装置

【課題】高い周波数のクロックを用いずに雑音を除去できる雑音除去回路及び雑音除去回路を備えた半導体装置を提供する。

【解決手段】データ入力信号がロウレベル又はハイレベルになると活性化しハイレベル又はロウレベルを維持するとクロック信号に同期して非活性化する第一及び第二のリセット信号を生成する第一及び第二のリセット信号生成回路と、クロック信号の反転信号を計数し第一又は第二のリセット信号によりリセットされる第一及び第二のカウンタ回路と、セレクタ回路とセレクタ回路の選択した信号をクロックに同期して出力する出力フリップフロップ回路とを備え、セレクタ回路がハイレベル又はロウレベルに固定された信号、出力フリップフロップの出力信号のいずれかを第一及び第二のカウンタ回路の出力信号の論理レベルにより選択して出力するデータ出力回路と、を備える。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

パラレル−シリアル変換器及びパラレルデータ出力器

【課題】パラレル−シリアル変換器において、データ信号をラッチするフリップフリップ(FF)に供給されるクロック信号の位相ずれを調整する。

【解決手段】FF1−1〜1−5によるデータ信号D0,D1を選択回路2で選択出力したデータ信号D[0+1]をFF4によりラッチ出力するパラレル−シリアル変換器において、レプリカのデータ信号repIN0,repIN1を選択回路10で選択出力したデータ信号repDをラッチしたFF11によるデータ信号repOUTに基づき位相ずれ検出回路12,13が生成する位相調整指示値信号に従い、分周回路3による分周クロック信号の位相を調整してクロック信号divCLKを発生する任意位相生成回路15を備えると共に、クロック信号ffCLKとrepCLKとを位相比較し、クロック信号repCLKを移相させる位相設定回路16,17を備える。

(もっと読む)

電圧範囲判断回路

【課題】電圧範囲判断回路を提供すること。

【解決手段】電圧範囲判断回路は対象電圧生成部、選択電圧生成部、比較電圧選択部及び出力信号生成部を含む。対象電圧生成部は、入力電圧に基づいて対象電圧を生成する。選択電圧生成部は、基準電圧に基づいて第1〜第2選択電圧を生成する。比較電圧選択部は、出力信号に基づいて、第1〜第2選択電圧の中で1つを選択して比較電圧に出力する。出力信号生成部は、対象電圧と比較電圧を比べて出力信号を生成する。電圧範囲判断回路は外部ノイズが流入する場合も入力電圧の電圧範囲を正確に判断することができる。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

データ取込保持装置

【課題】入力データの取り込みを誤りなくできるデータ取込保持装置を提供する。

【解決手段】パルス発生手段20からのラッチ用パルスPLSのパルス幅区間で入力データを取り込んで保持する第1のデータ取込記憶部を備える保持手段を備える。パルス発生手段20は、第1のデータ取込記憶部と同じあるいは同等の構成の第2のデータ取込記憶部231を備え、クロック信号CLKから、第2のデータ取込記憶部231における入力データの取込時間分のパルス幅区間のパルス信号PLSを生成し、ラッチ用パルスとして、第1のデータ取込記憶部に供給する。

(もっと読む)

システムにおけるフォールトトレラントなスペクトラム拡散クロック信号の提供

【課題】システムにおけるフォールトトレラントなスペクトラム拡散クロック信号を提供する。

【解決手段】フォールトトレラントなスペクトラム拡散クロック信号を供給するために、それぞれスペクトラム拡散制御回路を有する複数の処理モジュールが提供される。冗長なクロック供給源のクロック信号は、前記複数の処理モジュールに対して供給されるファイルオーバー制御ロジックは前記複数の処理モジュールそれぞれにおいて使用するために前記冗長なクロック供給源から前記クロック信号のうちの対応する1つを選択する。周波数拡散が、少なくともいくつかの前記複数の処理モジュールそれぞれにおいて前記対応する選択されたクロック信号に適用される。

(もっと読む)

閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置

【課題】閉ループ・クロック訂正方法および閉ループ・クロック訂正制御システム適応装置を提供する。

【解決手段】閉ループ・クロック訂正システムおよび方法は、少なくとも1つの同位相クロックおよび少なくとも1つの直交位相クロックを含む2つ以上の入力信号を調整するステップと、調整された直交位相クロック信号を、4象限補間出力クロック位相を生成可能なデバイスに印加するステップとを含む。補間出力クロック位相は、遅延されて測定デバイス用のクロックを形成する。2つ以上の調整された入力信号は、測定デバイス上で補間出力クロック位相の範囲にわたって測定される。測定デバイスからのサンプル情報を使用して、同位相クロックおよび直交位相クロック上の誤差が決定される。同位相クロックおよび直交位相クロックは、決定された誤差情報を使用して適応される。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

スキャナー、電気光学パネル、電気光学表示装置及び電子機器

【課題】双方向転送機能を有したスキャナーで信号数を削減するとともに出力電位を安定化させる。

【解決手段】同一導電型のトランジスターで構成された複数の単位回路510からなる双方向転送可能なスキャナーであって、前記スキャナーを構成する前記単位回路510は、外部から与えられる信号を選択的に出力端子に出力する出力トランジスターを有し、前記出力トランジスターのゲート電極は第1の方向スイッチを介して他の単位回路510の出力端子である第1の端子に電気的に接続され、前記出力トランジスターのゲート電極は第2の方向スイッチを介してさらに他の単位回路510の出力端子である第2の端子にも電気的に接続される。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

41 - 60 / 134

[ Back to top ]