Fターム[5J039KK29]の内容

Fターム[5J039KK29]に分類される特許

101 - 120 / 134

直角位相クロックを生成する方法および装置

【課題】 集積回路のある領域のクロックが別の領域のクロックと同相になるように調整する。

【解決手段】 本発明にかかる直角位相クロックを生成する方法および装置は、直角位相クロック発生装置が、受け取った基準クロックの2倍の周波数を有する2倍クロックを提供するクロック発生器を含む。2倍クロックの半分の周波数を有するアライメント信号を提供するように分周器回路が結合される。アライメント信号に従って、リカバリ回路が、2倍クロックから第1のクロックと第2のクロックを回復させる。第1と第2のクロックは、実質的に90°の位相差を有する。

(もっと読む)

複数のメモリのための信号バッファリングおよびリタイミング回路

【課題】複数のメモリ素子のための信号バッファリングおよびリタイミング回路を提供する。

【解決手段】複数のメモリ素子のための信号バッファリングおよびリタイミング(SBR)回路である。PLLをベースとするクロック発生器によって、受け取ったホスト・クロック信号から1組の位相シフト・クロック信号セットが生成される。複数の位相選択器の各々によって、前記1組の位相シフト・クロック信号セットからサブセットの連続クロック信号が個々に選択される。個々のサブセットの連続クロック信号が、異なる組の1つまたは複数のバーニヤに印加され、個々のバーニヤによって、複数の連続クロック信号の中から1つのクロック信号が個々に選択される。SBR回路は、スキューおよび遅延に関連する比較的厳格な信号タイミング要求事項を満足するように設計することができる。

(もっと読む)

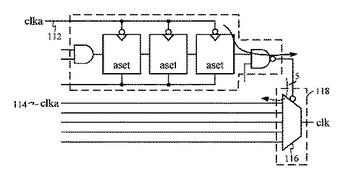

グリッチフリークロック信号マルチプレクサ回路および動作の方法

通信(例えばCDMA)システムにおける送信を処理することを含む(が、それに限定されない)デジタル信号プロセッサの設計及び利用の技術を開示する。クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。クロックマルチプレクサは、第1のクロック入力を受信し、クロック出力を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサは、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサの出力は第2のクロック信号のフェーズレベルに従う。  (もっと読む)

(もっと読む)

クロック切替回路

【課題】位相が異なるクロックを非同期の切替信号に基づき切り替えても出力クロックに、切り替え時の短パルスが発生しないクロック切替回路を提供すること。

【解決手段】クロック切替回路1は、外部クロックCLKT、CLKBが入力されそれぞれPLL回路2、3と、PLL回路3の出力PLBかPLL回路2の出力PLTの反転信号を選択出力するマルチプレクサ14と、CLKB、PLBとは非同期のLock判定信号12aに基づきマルチプレクサ14を切り替え制御するクロック制御回路13とを有する。クロック制御回路13は、Lock判定信号12aが入力されるとPLBの位相を所定値オフセットさせたオフセットクロックPLQBに同期してマルチプレクサ14の出力を切り替えさせる。

(もっと読む)

半導体集積回路

【課題】 簡単な回路構成で電源変動に起因するジッタによる評価を十分に行なうことができる半導体集積回路を提供する。

【解決手段】 ジッタ発生回路10で周期的にもしくは突発的に電源ノイズを発生して、PLL回路1_1から出力されるクロック信号にジッタを付与して、経路切替回路1_3および第2の信号伝送回路1_4を経由して論理回路1_5におけるジッタ増大の定量的な評価を行なう。

(もっと読む)

クロック供給回路

【課題】 ジッタの低減化が図られたクロック供給回路を提供。

【解決手段】 第1の周波数の第1のクロックで動作する第1の回路ブロック10と、第1のクロックを2逓倍して第2の周波数の第2のクロックを生成する逓倍回路30と、第2の周波数と同一の第3のクロックで動作する第2の回路ブロック20と、第2のクロックと第2の回路ブロック20を経由した第4のクロックの2つのクロックの周波数と位相が一致するようその周波数が制御された第5のクロックを生成するPLL回路40と、第5のクロックを遅延させる遅延回路60からの遅延クロックで動作するモニタ回路23と、第2のクロックとモニタ回路23を経由した第6のクロックとの位相の早遅に応じて第2の回路ブロック20の第1の周波数に同期したジッタを打ち消すようあらかじめジッタが印加された第3のクロックを生成して第2の回路ブロック20に供給するジッタキャンセル回路50とを備えた。

(もっと読む)

スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させる方法、回路、及びシステム

【課題】スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させるための方法、回路、及びシステムを提供する。

【解決手段】スプレッドスペクトラムクロック信号を発生させる方法は、同期システムのためのスプレッドスペクトラムクロック信号を提供するために選択される複数の遅延された高周波クロック信号を提供するために高周波クロック信号を遅延させる段階を含む。

(もっと読む)

スペクトル拡散クロッキング

状態マシン回路を使用して、多重入力クロック信号のそれぞれのクロック信号を選択し、そのような入力クロック信号に応答して、合成クロック信号を生成するクロック合成回路へ供給する、多重化回路を制御することができる。

状態マシン回路の構成は、例えば、合成クロック信号が、スペクトル拡散クロック信号、および/または入力クロック信号のそれぞれの名目周波数よりも大きい名目周波数を有するクロック信号、となるようにすることができる。  (もっと読む)

(もっと読む)

パルス位相差符号化回路

【課題】入力される電圧信号のレベルが回路の動作電源電圧より上昇した場合でも、正確な符号化動作を行うことができるパルス位相差符号化回路を提供する。

【解決手段】A/D変換回路11を構成するパルス位相差符号化回路13において、カウンタ2のカウント値をデータラッチ回路4にラッチさせるタイミング信号を生成するため、符号化周期信号PBに所定の遅延時間T12を付与する遅延回路12を、電圧入力端子に与えられる電圧信号Vinのレベルが上昇するのに応じて遅延時間が短縮されるように構成する。具体的には、遅延回路12を、リングディレイライン1を構成するNOTゲートと同じNOTゲートを、リングディレイライン1を構成する直列段数の1/2となる段数で直列接続して構成し、それらのNOTゲートを、A/D変換対象となる入力電圧Vinを電源として動作させる。

(もっと読む)

改良型のフラッシュアナログデジタルコンバータ

【課題】差動抵抗ラダーの駆動源から最大遅延を受ける中央ノードの遅延量を低減するADCを提供する。

【解決手段】差動アナログデジタルコンバータ(ADC)は、第1及び第2の抵抗ラダーレッグ、第1及び第2の増幅器、並びに複数の比較器を備える。各抵抗ラダーレッグは、中間ノードに接続する第1の端部及び電流源に接続する第2の端部を有する二つの抵抗を含む。第1の増幅器は、入力信号の第1の相に基づく電圧を第1の抵抗ラダーレッグの中間ノードに印加する。第2の増幅器は、入力信号の第2の相に基づく電圧を第2の抵抗ラダーレッグの中間ノードに印加する。複数の比較器は各々、第1及び第2の入力を有し、第1の入力は第1の抵抗ラダーレッグの二つの抵抗のうち一方に接続し、第2の入力は第2の抵抗ラダーレッグの二つの抵抗のうち一方に接続する。

(もっと読む)

クロックロス検出およびスイッチオーバー回路

【課題】好適なロックロスを検出しクロック信号のスイッチオーバーを実行する回路を提供すること。

【解決手段】1局面では、実施形態はクロックロスセンスおよびスイッチオーバーの回路と、クロックスイッチオーバーが1次信号のロスと追加のスイッチコマンドシグナリングとに応答する方法を提供する。別の局面では、実施形態は、クロックロスセンス回路と、カウンタおよびリセット信号を用いて1次クロック信号および2次クロック信号を比較する方法とを提供する。1つの局面においては、1次クロック信号のロスを素早く簡単に決定するためにカウンタおよびエッジセンサを使用するクロックロスセンス回路を提供する。また、別の局面では、本発明による実施形態は、クロックロス信号および追加のスイッチコマンド信号の双方に応答するクロックスイッチオーバー回路を提供する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】偶数番目、奇数番目のデータのデューティの変動等に個別に対応し補正可能な、クロックアンドデータリカバリ回路の提供。

【解決手段】互いに位相が90度ごと離間した4相のクロック信号を生成する4相生成回路10と、位相が180度離間した2つのクロックを入力して位相を補間し、前記補間した信号、及び、前記補間した信号と逆相の信号を出力する第1及び第2のインタポレータ301及び302と、前記第1、第2のインタポレータからの4相のクロックを入力し、第1及び第2インタポレータ301及び302から出力される4相のクロック信号はそのままバッファリングして出力し、第1及び第2のインタポレータ301及び302からの4相のクロック信号のうち、位相が相隣る2つのクロック信号を補間してなる4相のクロックを生成する4相8相変換回路80とを備える。

(もっと読む)

ジッタ注入を組み込んだ高速トランシーバテスタ

高速シリアルトランシーバ回路をテストするためのテスタである。このテスタはジッタ生成器を含み、このジッタ生成器は、急速に変化する位相選択用信号を使用し、2つ以上の互いに異なる位相のクロック信号から選択し、位相変調した信号を生成する。この位相選択用信号は低い周波数の成分および高い周波数の成分を含むよう設計する。前記位相変調した信号は位相フィルタへの入力であり、この位相フィルタは所望でない高い周波数の成分をフィルタする。前記位相フィルタのフィルタ処理出力は、データ送信シリアライザへの入力であり、このデータ送信シリアライザは、前記トランシーバ回路への入力のため、ロースピードパラレルワードを高速のジッタ付与テストパターンへシリアライズする。  (もっと読む)

(もっと読む)

周波数逓倍回路

【課題】 ディレイラインによるPLL技術を用いた周波数逓倍回路におけるEMIノイズを抑制する。

【解決手段】 本発明の周波数逓倍回路は、電圧制御遅延回路(Delay)と、N個のDelayにCLKが入力され、CLKを位相遅延させてDELCLKを生成するディレイライン11aと、位相ロック状態において所定の電圧をGNV0に出力する遅延制御回路12aと、N個のDelayにCLKが入力され、当該Delayの各出力から異なる位相遅延量を持つN個の出力クロック信号(OUTn)を生成するディレイライン11bと、GNV0および複数の異なる基準電圧Snに基づいて、ディレイライン11bの位相遅延量を電圧制御する遅延制御回路12bと、OUTnを論理演算し、周波数がCLKの略N/2倍であるCLKOUTを生成する論理回路14を有する。

(もっと読む)

波形グリッチ防止方法

本発明におけるシステム開発目的は、発止させるパルス列の位相をグリッチやスプリアスパルスやデューティサイクルのスプリアス的変化なしで任意に変化させられるようにすることにある。この目的を達成すべく、本ゲート済周期波形発生システムにおいては、可調位相周期波形を発生させる発生器と、この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、を設け、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としている。  (もっと読む)

(もっと読む)

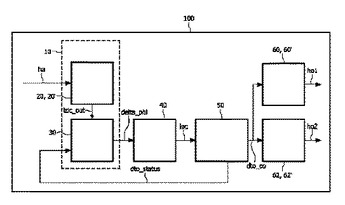

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

半導体集積装置

【課題】内部の機能切替における必要なクロックの切替にかかる煩雑さを解消し、外部から内部の機能切替の命令のみで精密なクロック設定を実現する半導体集積装置を提供する。

【解決手段】外部から入力される内部機能の切替の命令100の内容を判別し、特定の機能ブロック118に対して必要なクロックの周波数を判別するクロック周波数判定回路114と、切り替え前後の周波数の関係により、機能切り替えとクロック切り替えのタイミングを制御し、切り替えの状態を表す機能切替・クロック切替完了フラグ110を外部に出力するクロック切替制御回路113とを備えることにより、クロック切り替えの制御を外部から行う必要がなくなるようにした。

(もっと読む)

カスケードA/D変換器

【課題】 8ビットのデジタル値を得るためには基本構成要素を7段カスケード接続しなければならないためセトリングに時間がかかり、高速化が困難であったという課題を解決する。

【解決手段】 比較器、±4LSBの検出範囲を有するウインドウ・コンパレータ、D/A変換器、減算器からなる基本構成要素を4段カスケード接続する。これらの基本構成要素の出力を4つのウインドウ・コンパレータを有し、これらのウインドウ・コンパレータの出力を前記基本構成要素中のウインドウ・コンパレータの出力で選択する3個のマルチプレクサに入力して、これらマルチプレクサ内のウインドウ・コンパレータの検出範囲をそれぞれ±3LSB、±2LSB、±1LSBに設定する。高速化が可能でかつ構成が簡単になる。

(もっと読む)

コンパレータ回路

【課題】電圧比較部の入力部にオフセット電圧、オフセット電流、バイアス電流、それらのドリフトが存在したとしてもそれらの影響を受けないで入力電圧の大きさを判定する。

【解決手段】入力電圧(Vin)分圧した分圧入力電圧(V1)と基準電圧(Vs)を分圧して分圧基準電圧(V2)をマルチプレクサ(7)に入力する。マルチプレクサの出力側にA/D変換器(8)を設け、その出力を演算回路(9)に入力する。演算回路(9)はマルチプレクサに入力選択信号(SEL)を出力して入力の切り換えを行なわせ、分圧入力電圧と分圧基準電圧とをA/D変換した値をA/D変換器から取り込む。取り込んだ二つの電圧の大小関係をディジタル演算により判定することにより入力電圧と入力換算しきい値電圧との大小関係を出力する。

(もっと読む)

101 - 120 / 134

[ Back to top ]