Fターム[5J042BA14]の内容

Fターム[5J042BA14]に分類される特許

1 - 20 / 35

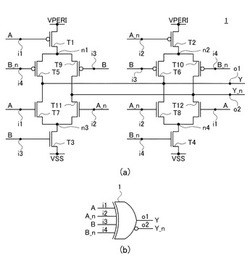

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法

【課題】入力信号の状態が適正であるかを確認することができる、ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法を提供する。

【解決手段】トリミング回路14の読出回路20から出力されるトリミング素子であるヒューズ素子H1の状態に応じた入力信号I1が入力されるラッチ回路22を、ラッチ回路L1と、ラッチ回路L2と、一致確認回路26と、で構成している。ラッチ回路L1は、入力信号I1の論理値をタイミングT1で保持して、保持した論理値に応じた出力信号O1をトリミング回路14の外部に出力する。ラッチ回路L2は、タイミングT1よりも遅いタイミングT2で保持して、保持した論理値に応じた出力信号O2を出力する。一致確認回路26は、排他的論理和回路30により構成されており、出力信号O1と出力信号O2とが一致しているか否かを示す一致判定信号X1を外部の判定回路18に出力する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体集積回路

【課題】より信頼性の高い半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、入力信号DINを記憶保持する複数のフリップフロップF1と、複数のフリップフロップF1からの出力の多数決結果MJを出力する多数決回路7と、複数のフリップフロップF1の出力不一致を検出し、エラー信号を出力するエラー検出回路2と、エラー検出回路2からのエラー信号を監視する監視回路3と、を備え、監視回路3は、エラー検出回路2からのエラー信号をもとに、複数のフリップフロップF1のうち、出力不一致が発生しているフリップフロップF1に対して書き戻しを行うリフレッシュ動作を指示するとともに、リフレッシュ動作により書き戻らなかった場合には外部に通知を行うものである。

(もっと読む)

コンフィグレーション装置、コンフィグレーション方法及びコンフィグレーションプログラム

【課題】論理回路のコンフィグレーションを効率よく行うことが出来るコンフィグレーション装置を提供する。

【解決手段】FPGA部200に含まれる複数のFPGAの各々にテスト用の論理回路を構築するためのテスト用コンフィグレーションデータ111と、複数の正式用デバイスデータ112aとからなる正式用コンフィグレーションデータ112を保持するデータ保持部110と、複数のFPGAに論理回路を構築するコンフィグレーション制御部120と、テスト用デバイスデータにより電子回路が構築された複数のFPGA間の入出力特性を測定し、複数のテスト用デバイスデータから特定のデバイスデータを抽出するコンフィグレーション選択部130とを備え、コンフィグレーション制御部120が、抽出されたテスト用デバイスデータ111aに対応づけられた正式用デバイスデータ112aにより、複数のFPGAに論理回路を構築する。

(もっと読む)

論理回路

【課題】伝播遅延時間の短縮を図り高速化に対応可能とした論理回路の提供。

【解決手段】論理信号をそれぞれ入力とする第1及び第2の入力端子A、Bを有し、ソースがそれぞれに対応する第1及び第2の入力端子A、Bに接続され、ゲートが、第2及び第1の入力端子B、Aに交差接続された第1及び第2のMOSトランジスタNM1、NM2を備え、第1及び第2のMOSトランジスタNM1、NM2のドレインが共通接続され、第1の電源VDDと、第1及び第2のMOSトランジスタNM1、NM2のドレインの共通ノードN1との間に接続され、リセット信号/RESETをゲートに受けリセット時に導通するMOSトランジスタPM1を備え、さらに共通ノードN1を入力端に接続してなるインバータINVを備えている。

(もっと読む)

XOR及びXNORロジックの回路及びレイアウト

XOR回路は、第2の入力ノードによって制御されるパスゲートを備える。そのパスゲートは、制御されたとき、第1の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。伝送ゲートが、第1の入力ノードによって制御される。その伝送ゲートは、制御されたときに、第2の入力ノードに存在するロジック状態のバージョンを出力ノードに通すように接続されている。プルアップロジックが、第1及び第2の入力ノードの両方によって制御される。そのプルアップロジックは、第1及び第2の入力ノードの両方がハイのときに、出力ノードをロウに駆動するように接続されている。XNOR回路は、プルアップロジックが、第1及び第2の入力ノードの両方がハイときに出力ノードをハイに駆動するように接続されたプルダウンロジックに置換されることを除いて、XOR回路と同様に画定される。  (もっと読む)

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

排他的論理和回路および電気光学装置

【課題】前段に接続される回路構成によって論理出力端子から出力される波形の立ち上がり、および、立ち下がりに偏りが生じることを回避した排他的論理和回路を提供する。

【解決手段】第1論理入力端子In-1を、クロックドインバータの入力端および伝送ゲートの入力端子にそれぞれ接続し、第2論理入力端子In-2を、クロックドインバータのクロック入力端に接続し、第2論理入力端子In-2の論理レベルを反転した信号を、伝送ゲートの制御端に供給し、クロックドインバータの出力端および伝送ゲートの出力端子の接続点を論理出力端子Outとする。

(もっと読む)

フォルト検出回路

【課題】フォルト検出回路において、回路規模を低減し、故障や誤動作がどの部分で起こっているのかを明らかにできるようにする。

【解決手段】論理回路20を自己双対関数によって設計し、外部から同じ内容のデータを2回入力する。論理回路20では、転送1回目のデータが反転されずに演算され、この結果が第4フリップフロップ32に保持され、転送2回目のデータが反転されて演算され、この結果が第3フリップフロップ31に保持される。これにより、出力側エラー検出回路34によって、第4フリップフロップ32に保持されたデータと、第3フリップフロップ31に保持されたデータとが比較され、各データが異なるときにはエラーが出力される。

(もっと読む)

半導体集積回路

【課題】フリップフロップのソフトエラー耐性を向上することが可能な半導体集積回路を提供する。

【解決手段】制御回路が、クロック信号生成回路に第1のクロック信号および第2のクロック信号を制御させて、第1のデータ保持端子に保持されたデータの論理と第2のデータ保持端子に保持されたデータの論理とを同じにし、その状態で、スイッチ回路をオンする。その後、スイッチ回路をオンさせた状態のまま、エラー検出回路が、第1のデータ保持端子の論理と第2のデータ保持端子の論理とを検知する。

(もっと読む)

論理回路

【課題】CMOS半導体集積回路において、パリティ検査等の高速化のために排他的論理和の多段接続回路を高速化する。

【解決手段】2入力排他的論理和が2段以上連続する部分の各々の排他的論理和を相補入出力排他的論理和、すなわち2組の相補信号入力と1組の相補信号出力を有するものとして実現し、かつ正と負の前記相補信号出力を生成するために各々1個ずつのAOI22論理ゲートすなわちAND−OR−NOT複合論理ゲートまたはOAI22論理ゲートすなわちOR−AND−NOT複合論理ゲートを用いることで、排他的論理和1段あたりのゲート段数を削減し高速化する。

(もっと読む)

半導体集積回路装置及びアイ開口マージン評価方法

【課題】 高速シリアルデータ受信回路のアイ開口マージン評価として、クロック相を固定せず、クロックデータリカバリー回路の動作を含んだアイ開口マージン評価回路を提供する。また、位相情報にオフセットを与えることでジッタ成分を付加し、受信データエラー加速試験を可能にする。

【解決手段】 シリアルデータを受信するシリアライザ・デシリアライザ回路201(SerDes)と、並走クロック信号を受信する参照シリアライザ・デシリアライザ回路202(Ref_SerDes)とを有し、シリアライザ・デシリアライザ回路201(SerDes)は、参照シリアライザ・デシリアライザ回路202(SerDes)の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。位相制御信号P_CSに、パルス生成回路602からのオフセット調整パルスOffset_Pulseを印加することで、アイ開口マージン評価を行う。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

デュアルレールセレクタ回路

【課題】 故障の有無を容易に認識し、故障時には、これを修復する。

【解決手段】 論理信号A,Bの一方を選択する正論理ゲート回路10の出力と、その反転信号Aバー,Bバーの一方を選択する負論理ゲート回路20の出力とが一致するか否かをXOR回路30で判定する。判定結果Fが1であれば正常、0であれば故障と認識できる。正常時には、選択回路40はインバータ11経由の信号を出力し、選択回路50はインバータ21経由の信号を出力する。判定結果が故障を示したときには、種々の論理パターンを入力として与えたときの出力パターンを解析し、ゲート回路10,20のいずれが故障したかを認識する。ゲート回路10の故障時には、選択回路40がインバータ22経由の信号を選択するように切り換え、ゲート回路20の故障時には、選択回路50がインバータ12経由の信号を選択するように切り換える。

(もっと読む)

半導体装置

【課題】第三者による不正な攻撃によって故障動作を引き起こされた場合でも、故障動作を検出し、回路動作を停止することが可能となるような半導体装置を提供する。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

(もっと読む)

論理機能回路と自己診断回路とからなる統合回路の設計方法

【課題】容易にエラー検出率を算定することができ、モニタするノードの最適化が容易で、ノードカバー率が高い、論理機能回路と自己診断回路とからなる統合回路の設計方法を提供する。

【解決手段】モニタノードテストリストLMに基づいてテスト統合回路KTを構成する第1ステップS1と、故障シミュレーションを実施し、各ノードのトグルについて自己診断回路KCによる検出の可否を判定する第2ステップS2と、トグル検出可否判定結果から、エラー検出率を算出する第3ステップS3と、エラー検出率が規格エラー検出率以上であるか否かを判定する第4ステップS4とを有し、エラー検出率が規格エラー検出率より小さい場合には、モニタノードテストリストLMを変更して、第1ステップS1に戻り、エラー検出率が規格エラー検出率以上である場合には、テスト統合回路KTを採用して、統合回路の設計を終了する。

(もっと読む)

論理関数を実行する電気デバイス

電子デバイスが少なくとも1の論理関数を実行するために示されている。デバイスは、電子取出器に連結された電子放出式の電極配列を具える。電極配列は、光電陰極と、陽極と、光電陰極と陽極の間に規定され、キャビティのわきに配列された1又はそれ以上のゲートとを具える少なくとも1の基本ユニットを具える。1又はそれ以上のゲートは電圧電源ユニットに接続可能であり、1又はそれ以上の論理値のそれぞれに対応する1又はそれ以上の入力電圧信号によって動作する。陽極は、得られる論理関数の指標であるデバイスの電気出力が読み出される浮遊電極として機能する。陽極は、同じデバイスの別の陰極陽極ユニットの光電陰極に電気的に接続される、又は別の電子デバイスの電極に接続される。 (もっと読む)

1 - 20 / 35

[ Back to top ]