Fターム[5J042CA11]の内容

Fターム[5J042CA11]に分類される特許

1 - 18 / 18

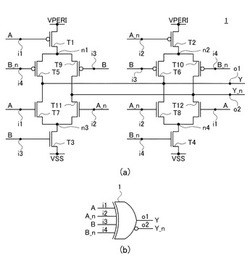

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

論理回路

【課題】CMOS半導体集積回路において、パリティ検査等の高速化のために排他的論理和の多段接続回路を高速化する。

【解決手段】2入力排他的論理和が2段以上連続する部分の各々の排他的論理和を相補入出力排他的論理和、すなわち2組の相補信号入力と1組の相補信号出力を有するものとして実現し、かつ正と負の前記相補信号出力を生成するために各々1個ずつのAOI22論理ゲートすなわちAND−OR−NOT複合論理ゲートまたはOAI22論理ゲートすなわちOR−AND−NOT複合論理ゲートを用いることで、排他的論理和1段あたりのゲート段数を削減し高速化する。

(もっと読む)

フイールドバス用3値信号出力回路

【課題】回路構成が比較的簡単で、回路規模が小さく、消費電流の小さなフイールドバス用3値信号出力回路を実現すること。

【解決手段】直流電流とデジタル信号とが共通の伝送線路で伝送されるフイールドバスに静止レベルとハイレベルとローレベルの3値を出力する3値信号出力回路であって、相補的にオン・オフ制御される2つのスイッチを設け、一方のスイッチを介して静止レベルを出力し、他方のスイッチを介してハイレベルとローレベルを出力することを特徴とするもの。

(もっと読む)

多数決回路

【課題】構成が簡素で高精度な判定性能を有する多数決回路を提供する。

【解決手段】本発明に係る多数決回路は、差動対をなす第一及び第二トランジスタを有する差動アンプと、一方の電極に第一デジタル信号のビット信号が印加されると共に他方の電極が前記第一トランジスタのゲートに共通接続された複数の第一キャパシタと、一方の電極に第二デジタル信号のビット信号が印加されると共に他方の電極が前記第二トランジスタのゲートに共通接続された複数の第二キャパシタとを備える。

(もっと読む)

低電圧差動信号ドライバ、低電圧差動信号を駆動する方法及びシステム

【課題】低い伝送速度で大きな出力電圧振幅をもたらし且つ高い伝送速度で低い出力電圧振幅を単独のドライバでもたらすこと。

【解決手段】低電圧差動信号(LVDS)ドライバは、信号を駆動するよう動作する少なくとも2つのプログラマブルフィンガと、少なくとも2つのプレドライバとを含む。プレドライバの各々は1つのプログラマブルフィンガに関連し且つ該関連するプログラマブルフィンガをイネーブルに又はディセーブルにする。イネーブルにされたプログラマブルフィンガは信号を駆動し且つ当該ドライバの容量負荷に寄与し、ディセーブルにされたプログラマブルフィンガは信号を駆動せず且つ当該ドライバの容量負荷に寄与しない。

(もっと読む)

半導体集積回路

【課題】ゲート回路の待機時に、出力に接続したプルアップトランジスタを流れるゲートリーク電流を低減する半導体集積回路を提供する。

【解決手段】論理部1と、グランドVSSと論理部1との間に接続され、論理部1へ電源電圧を供給するか否かの制御を行う制御信号MTEがゲート電極に入力されるスイッチトランジスタ2と、論理部1の出力端子と電源線VDDとの間に接続され、スイッチトランジスタ2のオン時はオフし、スイッチトランジスタ2のオフ時はオンするプルアップトランジスタ3と、スイッチトランジスタ2のゲート電極とプルアップトランジスタ3のゲート電極との間に接続され、ゲート電極がグランドに接続されているPMOSトランジスタを有するプルアップ制御部4と、を備える。

(もっと読む)

汎用論理モジュール及びそれを有する回路

【課題】プログラマブルかつ最適制御可能な汎用論理モジュール及びそれを有する回路を提供する。

【解決手段】集積回路29は、汎用論理モジュール25と、結合部26と、計算部28とを具える。汎用論理モジュール25は、二つの入出力制御部23と、記憶部24とを有し、設定及び制御情報が入力される。入出力制御部23は、入出力端子21に入力される情報及び入出力端子22に入力される入出力制御情報の組合せ論理演算を行う。記憶部24は、組合せ論理演算の結果を記憶し、その結果の肯定又は否定を出力する。記憶部24は、第1反転増幅器及びそれに交差結合した第2反転増幅器と、強誘電体又は強磁性体の記憶素子とを有する。

(もっと読む)

論理ゲートおよび論理回路

【課題】 サブスレッショルドリーク電流を低減した論理ゲートを提供する。

【解決手段】 ソースに第1の電圧が印加され、ゲートに第1の入力信号が入力され、ドレインから第1の出力信号を出力する第1のトランジスタと、ソースに第1の電圧よりも低い第2の電圧が印加され、ゲートに第2の入力信号が入力され、ドレインから第2の出力信号を出力する第2のトランジスタと、第1のトランジスタおよび第2のトランジスタのドレイン間に接続され、第1のトランジスタと第2のトランジスタを接続または切り離す接続切換部とを有する構成である。

(もっと読む)

インピーダンス調整回路及び集積回路装置

【課題】 チップ内のバラツキに起因するインピーダンスの調整精度の低下を抑制できるインピーダンス調整回路及びこれを搭載した集積回路装置を提供する。

【解決手段】 NMOS用インピーダンス調整回路において、外部の基準抵抗及びNMOSアレイによる分圧電位Vinと参照電位VREFnとを比較する比較回路を設け、NMOSアレイがこの比較結果に基づいて出力バッファ回路のインピーダンスをシミュレートするようにする。比較回路14には差動回路D1乃至D3を設け、2入力のナンドゲートNAND21乃至NAND23及び3入力のナンドゲートNAND24が、差動回路D1乃至D3の出力値の多数決をとって比較回路14から出力するようにする。

(もっと読む)

三値論理関数回路及び多値論理関数回路

【課題】 33^2=19683種類存在する全ての二変数三値論理関数回路を実現するために必要となる基本回路の種類を著しく削減するとともに、スイッチング時間の非対称性も著しく小さくすることができる三値論理関数回路を提供する。

【解決手段】 二変数三値論理演算を行う三値論理関数回路は、第1の入力aを構成する3つの論理値−1,0,1に応じて、一変数三値論理関数回路C1,D1,C2,D2,C3,D3によって3つのトランスファーゲートT1,T2,T3を導通又は遮断し、第2の入力bに接続される3つの一変数三値論理関数回路B1,B2,B3の出力を選択する。

(もっと読む)

入力論理ゲート回路、ラッチ回路、フリップフロップ回路、分周回路、及びそれらを備えた携帯端末

【課題】 高速性を犠牲にせずに最小電源電圧を下げることができ、より低電圧(例えば1V以下)で動作する電流モード型の入力論理ゲート回路、ラッチ回路、フリップフロップ回路、分周回路、及びそれらを備えた携帯端末を提供する。

【解決手段】 2信号入力基本論理ゲート回路20は、ドレインがノードXに接続され、ソースがノードN1に接続され、ゲート及びウエルに入力信号Aを入力する、ゲート及びウエルが互いに接続されたNMOSトランジスタM1と、ドレインがノードYに接続され、ソースがN1に接続され、ゲート及びウエルに入力信号Bを入力する、ゲート及びウエルが互いに接続されたNMOSトランジスタM2と、ノードXと電源端との間に接続された抵抗素子R1と、ノードYと電源端との間に接続された抵抗素子R2と、ノードN1と接地端との間に接続された定電流源CS1とを備えている。

(もっと読む)

インターフェース回路

【課題】 LVDSインターフェース回路及びCMOSインターフェース回路を併用する。

【解決手段】 LVDS信号と、第1のCMOS信号のいずれか一方を選択する第1の選択回路21と、LVDS信号及びこの第2のCMOSのいずれか一方を選択する第2の選択回路22と、この第1の選択回路21の出力信号を夫々のゲートに供給する第1のPチャンネルMOSトランジスタ25P及び第1のNチャンネルMOSトランジスタ25Nと、この第2の選択回路22の出力信号を短絡スイッチ26a付きインバータ回路26を介して夫々、共通の定電流源28、30を有する25Pと25NからなるCMOSのゲート、及び27P27NからなるCMOSの2つCMOSのゲートを介して出力する。

(もっと読む)

共通モードアイドル状態および選択可能なスルーレートを有するTxラインドライバ

選択可能なスルーレートおよび共通モードアイドル状態を有する送信ラインドライバは、ラインドライバ(184)およびプリドライバ(182)の間に結合される選択可能なキャパシタのキャパシタアレイ(186)を含み、選択可能なキャパシタによってスルーレートが選択されてもよい。共通モードアイドル状態は、選択可能なスイッチ(214、215)(記載される実施例におけるMOSFET)を、プリドライバにバイアス電流を与えるミラーデバイス(198)に結合することによって与えられ、スイッチによってバイアス電流が除去されるときに、プリドライバは回路に対する電源電圧に等しい出力信号を生成する。したがって、ラインドライバの差動対(202、204)はともにバイアスをかけられてオンにされ、共通モードアイドル状態を与える。共通モードアイドル状態は論理1に対する出力信号の大きさの半分に等しい。  (もっと読む)

(もっと読む)

スキュー制御を有するクロックジェネレータ

クロック発生をもたらすためのシステムおよび方法が開示される。一実施例によれば、構成可能でインシステムプログラマブルな、柔軟なスキュー制御アーキテクチャを含むクロックジェネレータチップが与えられる。クロックジェネレータチップはさらにプログラム可能な入力回路、プログラム可能な出力回路を与えることができ、JTAGバウンダリスキャンを可能にし得る。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]