Fターム[5J042CA17]の内容

Fターム[5J042CA17]に分類される特許

1 - 20 / 25

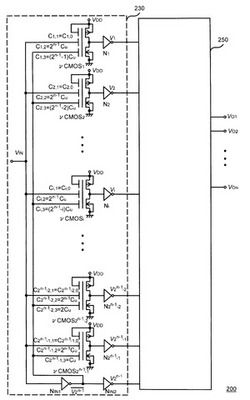

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

電気回路および/または電子回路に関するコンフィギュレーション方法ならびにデバイス

【課題】同じタイプの特性量を有し、この特性量の値が相互に比例するいくつかの機能ブロックを備える電気回路をコンフィギュレーションする。

【解決手段】機能ブロックは、同様のタイプの少なくとも1組の電気素子(102a〜102d、104a〜104d)と、前記電気素子を互いに接続するおよび/もしくは電気回路100の残部に接続するための手段(106a〜106d、108a〜108d、110a〜110d)とにより構築され、テストされる1組の接続コンフィギュレーションのそれぞれに対して、電気回路のパラメータの値を測定するステップと、テストされる結合コンフィギュレーションの中から、測定されたパラメータの値が、少なくとも1対の機能ブロックの特性量の値間の不整合が最小の1つのコンフィギュレーションを選択するステップと、選択されたコンフィギュレーションに従って、接続する手段をポジショニングするステップとを含む。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

遠隔で再構成可能な電力増幅器システムおよび方法

電力増幅器システムを遠隔で監視し、同システムと通信し、そして同システムを再構成するためのシステムおよび方法に関する。デジタル構成要素または電力増幅器システムの他の通信可能な部分との遠隔通信を可能にするための通信リンクが、現場に配置されたPAシステムに設けられる。通信リンクにより、PAの動作パラメータが、インターネット、イーサネット、無線、WiFi、WiMAX、携帯電話、LAN、WAN、Bluetoothなどの任意の適当な有線または無線接続を通じて監視され、ウェブサーバや他のコンピュータメインフレームなどの遠隔端末に送り返され得る。本発明を実施することにより、cMobileオペレータおよび/または他のサービスプロバイダの無線ネットワークのメンテナンスおよびPAの交換に関する顕著な事業費および資本経費を低減することができる。 (もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

半導体装置

【課題】可変論理機能を実現するための記憶回路を論理回路と等価な回路として扱う構成において可変論理に対する機能設定の負担を軽減する。

【解決手段】半導体装置はアクセス制御装置(2)の制御を受ける機能再構成メモリ装置(8)を有し、機能再構成メモリ装置はアクセス制御装置からのアクセス要求を受け、インタフェース制御回路に複数の機能再構成セル(20)と機能再構成セルに一対一対応で設けられ機能再構成セルからの出力を受けて演算を行う可変演算セル(101)が接続される。機能再構成セルの制御回路は第1の動作モードで記憶回路の制御フィールドとデータフィールに初期設定された真理値データのようなデータを、第2の動作モードにおいて制御フィールドのデータに基づいて自律的に制御することによって論理動作を行う。可変演算セルは記憶回路の制御フィールドから出力される制御データなどに基づいて演算動作が可能にされる。

(もっと読む)

半導体集積回路

【課題】機能を柔軟に制御可能なアナログの機能ICを提供する。

【解決手段】アナログブロック10は、所定のアナログ信号処理を実行する。デジタルブロック20は、再構成可能に構成され、所定のデジタル信号処理を実行してアナログブロック10を制御する。FeRAM30は、デジタルブロック20の回路構成のコンフィギュレーションデータを格納する。機能IC100は、FeRAM混載プロセスを用いてひとつの半導体基板上に一体集積化され、アナログブロック10の動作状態が、デジタルブロック20の構成状態に応じて変更可能である。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

並列に給電される多数の同一基本回路を含む集積回路

本発明は、1からNまで変化するそれらの順位jの順番に並列に置かれたN個の同一な基本回路(CE1,CE2,...CEN)の連続を備え、Nは少なくとも50に等しく、2つの導体(CA及びCB)により供給される、2つの基準電位Vref及びV0を全てが受ける必要がある集積回路に関する。第2導体の上流側入力は、並列に置かれた回路の連続の順位1の側に地理的に位置し、第1導体の上流側入力は、並列に置かれた回路の連続の順位Nの側に地理的に位置する。これは回路の連続に全て沿った基本回路に印加される電位差における、導体の非ゼロ抵抗から由来する誤差を減らす。

高い分解能(10ビット以上)を有するアナログ−デジタル(AD)変換器、又はデジタル−アナログ(DA)変換器への適用

(もっと読む)

多値出力回路及びこれを用いた液晶駆動装置

【課題】本発明は、小規模な回路構成でありながら、設定電圧の増加や変更にも柔軟に対応することが可能な多値出力回路を提供することを目的とする。

【解決手段】本発明に係る多値出力回路は、デジタル信号(電圧設定信号SET)からアナログ電圧Va〜Vdを生成するデジタル/アナログ変換部3と;電圧選択信号A1に基づいて、アナログ電圧Va〜Vdのいずれか一を選択的に出力する電圧選択部41〜4nと;電圧選択部41〜4nの出力電圧を液晶パネル7に供給するバッファ51〜5nと;を有して成る構成とされている。

(もっと読む)

信号伝送システム

【課題】 信号配線数を増大させることなく、微細化等に伴う電源電圧の引き下げによる伝送品質への影響を低減できる信号伝送システムを提供する。

【解決手段】 送信回路10が、多値伝送データDCの値別に伝送データ用電流値を規定した信号変換条件に基づいて、送信対象の複数の2値電圧データを伝送データ用電流値の多値伝送データDCに変換し出力する多値伝送データ生成出力回路を備え、伝送データ用電流値の夫々が単位伝送データ用電流値の整数倍で規定され、多値伝送データ生成出力回路が、信号配線に対し単位伝送データ用電流値の電流を供給可能な単位電流駆動回路130を複数備えたデータ出力回路13と、複数の2値電圧データを多値電流データに変換した後の多値電流データの伝送データ用電流値に基づいて、単位電流駆動回路130別に、電流供給を行うか否かを設定するための駆動制御信号を生成する駆動制御信号生成回路と、を備える。

(もっと読む)

無線通信システムの動的再構成のための方法および装置

【解決手段】本発明は、自由にプログラム可能な論理制御部を有し、受信信号と送信信号とを処理する処理回路(10、11)を備える無線通信システムに関する。自由にプログラム可能な論理制御部のプログラミングは、それを送信動作と受信動作とに調整するために変更される。この変更は、バスシステムを介して、自由にプログラム可能な論理制御部における機能ブロックをエクスポートしインポートすることによって行われる。調整は、無線通信システムの機能を中断することなく行われる。  (もっと読む)

(もっと読む)

アナログ多重信号生成回路

【課題】シリアル変換器の個数をチャネル数よりも少なくすることにより、アナログ多重信号生成回路の低価格化等を図る。

【解決手段】符号化器150−1〜150−32は、対応するチャネルの信号を符号化する。論理加算器110は、被符号化信号の同位ビットどうしを加算し、5桁の二進数データと1桁のキャリーとからなる演算結果を生成するとともに、キャリーが‘0’のときは該演算結果をそのまま出力し、キャリーが‘1’のときは演算結果の全桁を‘1’に変える。シリアル変換器120−1〜120−6は、演算結果から対応する位のビット信号を入力して直列に変換する。電力・位相補正器130−1〜130−6は、ビット信号の位相調整と位に応じた電力増幅とを行う。多重器140は、電力・位相補正器130−1〜130−6から入力された被補正信号を互いに加算することによって、アナログ多重化する。

(もっと読む)

無線中継装置、符号化処理回路、およびそのインタフェース方法

【課題】低レベルのアナログ信号に対するデジタル信号の干渉障害を防いだ無線中継装置、符号化処理回路およびそのインタフェース方法を提供する。

【解決手段】フレーム分離部17の出力するデジタル信号のLSBと上位の複数ビットとの排他論理和をEXOReで各ビットの出力をランダムにした第1のデジタル信号をDACdへ向けて出力し低レベル信号でデジタル信号が相加して配線上でアナログ回路部分へ干渉しない様にする。そして、再びEXORfが第1のデジタル信号のLSBと上位の複数ビットとの排他論理和を取って元のデジタル信号にしてDACdへ入力し、アナログ信号に変換する。

(もっと読む)

プログラミング装置およびバッファ回路

【課題】スループットを大きく増大させる、プログラマブルマイクロデバイスをプログラムするプログラマシステムおよび方法を提供する。

【解決手段】プログラマシステムは、複数のマイクロデバイスを同時にプログラムするための複数のソケット(20A−20D)を含む。多数のマイクロデバイスを同時にプログラムするよう設計されるプログラマシステムのためのバッファ回路(32)もまた提供される。プログラマブルマイクロデバイスをプログラミングするための方法がさらに提供され、これはプロセッサ(12)からの標準のバスサイクルを使用してプログラミングする。最後に、単一のリードバック動作を用いて複数個のプログラムされたマイクロデバイスにプログラマによってプログラムされたデータをベリファイするための方法およびデータ比較回路もまた開示される。

(もっと読む)

液晶表示パネルにおけるソースドライバーのレシーバー

【課題】 従来の液晶表示器における制御信号とクロック信号との間の信号スキューを改善するソースドライバーのレシーバーを提供する。

【解決手段】 レシーバーは、2組の差動信号を第一形式から第二形式に変換するコンバーターと、コンバーターに結合され、第二形式に変換された2組の差動信号間の差に基づいて複数の基準信号を生成する比較回路と、比較回路に結合され、複数の基準信号に基づいて複数のデータ信号及び複数の制御信号を生成する復号回路とを含む。

(もっと読む)

超電導回路

【課題】 本発明は、ジッタが小さく精度の高いクロック信号を生成可能な超電導回路によるクロック発生回路を提供することを目的とする。

【解決手段】 超電導回路は、第1のトランスの2次側インダクタに結合され単一磁束量子パルスを生成する第1のパルス発生回路と、第2のトランスの2次側インダクタに結合され単一磁束量子パルスを生成する第2のパルス発生回路と、第1のパルス発生回路からの単一磁束量子パルスと第2のパルス発生回路からの単一磁束量子パルスとを重ね合わせたパルス信号を出力する合流回路を含み、第1及び第2のパルス発生回路の各々は、2次側インダクタを含む超電導ループと、超電導ループ内に設けられ単一磁束量子パルスを生成する第1のジョセフソン接合と、超電導ループ内に設けられ2次側インダクタを流れる電流に対する閾値が第1のジョセフソン接合とは異なる第2のジョセフソン接合を含む。

(もっと読む)

容量結合を利用したCMOSの時系列型AD変換回路及びDA変換回路

【課題】容量結合回路を利用して少ない素子数で論理回路,AD変換回路等を提供する。

【解決手段】アナログ入力が与えられる入力端子と、2値の出力が与えられるN(Nは複数)ビットの出力端子とを有するアナログ・デジタル変換回路において、一方の電極が入力端子に接続される入力容量と、入力容量の他方の電極が入力される第一のインバータと、該第一のインバータに接続される第二のインバータとを有する単位回路が、N個並列に設けられ、その単位回路の第二のインバータの出力がそれぞれの出力端子に与えられ、更に、各単位回路に対応する出力の反転出力が、それぞれ下位ビットに対応する単位回路の前記第一のインバータの入力に帰還容量を介して帰還され、最上位ビットからM(Mは整数)番目の単位回路の反転出力に対応する前記帰還容量の容量値は、帰還される単位回路の入力容量の1/2M 倍であることを特徴とするアナログ・デジタル変換回路。

(もっと読む)

プログラム可能回路網を含むデジタル信号プロセッサ

本発明は、複数のメモリユニット、複数のアクセラレータユニット、及びプロセッサコアを含むプログラム可能デジタル信号プロセッサに関する。デジタル信号プロセッサには、更に、メモリユニットと、アクセラレータユニットと、プロセッサコアとの間に選択的に接続性を提供するように構成し得るプログラム可能回路網が含まれる。各アクセラレータユニットは、1つ以上の専用機能を実施するように構成し得る。プロセッサコアには、データ経路フロー制御に関連する命令を実行するように構成し得る実行ユニットを含み得る。プログラム可能回路網は、特定の命令の実行に応じて、選択的に接続性を提供するように構成し得る。  (もっと読む)

(もっと読む)

プログラム可能論理装置及びその論理回路構成方法

【課題】プログラマブル論理装置おいて、相互接続配線の交差部のスイッチング素子に、オン・オフの制御信号を送信する制御配線の数を大幅に削減する手段を提供する。

【解決手段】入出力リードを備えた複数個の論理素子、該論理素子間を相互に接続する相互接続線、前記入出力リードを前記相互接続線に第1制御信号によって接続させる第1接続手段と、前記相互接続線を互いに第2制御信号によって接続させるプログラム可能な第2接続手段とを備えたプログラム可能論理装置において、前記第1制御信号及び/又は第2制御信号がアナログ多値信号であることを特徴とするプログラム可能論理装置。また、前記第1接続手段及び/又は前記第2接続手段が、アナログ多値信号を1組のディジタル信号に変換するA/D変換手段を含む上記の装置。

(もっと読む)

1 - 20 / 25

[ Back to top ]