Fターム[5J043AA11]の内容

Fターム[5J043AA11]に分類される特許

1 - 13 / 13

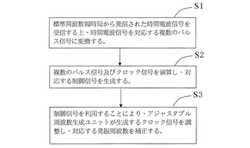

発振周波数補正方法及び発振周波数補正装置

【課題】電子製品の発振周波数を正確に補正するために用いる発振周波数補正方法を提供する。

【解決手段】発振周波数補正方法は、発振周波数に対応するクロック信号を生成するアジャスタブル周波数生成ユニットを有する電子製品の発振周波数を補正するために用いる。発振周波数補正方法は、標準周波数報時局から発信された時間電波信号を受信する上、前記時間電波信号を対応する複数のパルス信号に変換するステップS1と、前記複数のパルス信号及び前記クロック信号を演算し、対応する制御信号を生成するステップS2と、前記制御信号を利用することにより、前記アジャスタブル周波数生成ユニットが生成する前記クロック信号を調整し、対応する前記発振周波数を補正するステップS3と、を含む。

(もっと読む)

パス調整方法及び設計支援装置

【課題】設計期間の短縮化を図ること。

【解決手段】設計支援装置は、クロックツリー合成処理(ステップ23)にて生成したクロックツリーに含まれるクロックパスについて、電圧・温度の遅延感度をそれぞれ算出し、2つのクロックパスの遅延感度の差を0に近づけるように、クロックパスの遅延感度を調整する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

同期化結晶発振器ベースのクロックを採用するシステム

【課題】改良された同期クロックシステムを提供する。

【解決手段】同期クロック信号を必要とする複数のシステムノードを有する電子システム用の同期クロックシステム。クロックシステムは、第1の同期バスと第1の同期バスから絶縁された第2の同期バスと、交互にバスに接続された少なくとも1対、そして好ましくは複数対のSXOモジュールを含む。システムノードの各々は、第1のバスに沿った任意の場所において適宜選択されたあらゆる接続点のうちの異なる1つで接続される。SXOモジュールが接続されるバスに沿った点は、およそ等間隔で隔てられる。システムノードは信号調整回路を用いてバスに接続され、信号調整回路は、補正回路、増幅器、周波数逓倍器、論理変換器、およびファンバッファを含んでいてもよい。

(もっと読む)

クロック同期回路

【課題】スイッチング電源において、回路の複雑化、端子の増加を抑制して、内部クロックまたは外部クロックに同期した信号を出力させることができるクロック同期回路を提供する。

【解決手段】(a)ヒステリシスインバータ(INV1)33、抵抗(R1)34および外付けコンデンサ(COSC)31で内部クロックを生成する発振器を構成し、その出力信号(VOSC)35の発振周波数は外付けコンデンサ(COSC)31の値で任意に調整する。(b)上記の外付けコンデンサ(COSC)31を入力端子32から外し、上記のヒステリシスインバータ(INV1)33の入力に外部クロック(CK)36を印加することで外部クロック(CK)36に同期した信号(VOSC)35を得る。

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

同期回路

【課題】広い範囲で遅延調整を可能にしてACタイミングを確保し易くする。

【解決手段】フリップフロップ回路FF1と組合せ論理回路LOGIC1との間にフリップフロップ回路FF1aを挿入し、セレクタMUX1によりいずれか一方のフリップフロップ回路の出力データ信号を選択可能にする。フリップフロップ回路FF1に入力するクロック信号をフリップフロップ回路FF1aに入力するクロック信号よりも遅らせる。

(もっと読む)

発振回路

【課題】従来技術よりも正確な位相差を得ることができる発振回路を提供する。

【解決手段】複数のオペアンプ20−1〜20−4をループ状に直列に接続して構成されるリング発振回路202を含み、複数のオペアンプ20−1〜20−4における複数の出力信号を加算合成して第1の出力信号Vout1として出力すると共に、複数のオペアンプ20−1〜20−4における残りの総ての出力信号を加算合成して第2の出力信号Vout2として出力することによって上記課題を解決することができる。

(もっと読む)

クロック信号を生成する電気回路および方法

サンプリング装置(31)のためのクロックサンプリング信号(CLK)を生成するための電気回路(30)は、複数のクロック信号(21〜24、51〜54、61〜64)を生成するためのクロックジェネレータ(1、40、50、60)と、デジタル信号(DS)の特徴的な信号部分(LE)と複数のクロック信号(21、22、23、24、51〜56、61〜64)を相関させる相関装置(L)と、および相関装置(L)による相関に基づいて、クロック信号(21、22、23、24、51〜55、61〜64)のうちの1つを、クロックサンプリング装置のためのクロックサンプリング信号(CLK)として、選択する選択装置(MX)を備える。クロック信号(21〜24、51〜54、61〜64)は、同じサイクル周期(T)を有し、互いに位相シフトする。サンプリング装置(31)は、その後、クロックサンプリング信号(CLK)によってデジタル信号(DS)をサンプリングする。  (もっと読む)

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

高速回路のデータエッジ−クロックエッジ位相検出器

データ信号と基準クロック信号との間のスキューを検出してデータ信号と基準クロック信号とを同期させる新規の方法およびシステムが提示される。多相クロック発生器を使用して、共通の周波数を有する、複数の位相分離されたクロック信号を作成する。次に、複数のクロック信号を利用して、複数のクロック信号の一意のシーケンスにそれぞれ対応するタイミングビンを作成する。デジタルシステムの特徴に基づいて、タイミングビンは有効タイミングビンおよび無効タイミングビンに分けられる。インタフェースで受け取ったデータ信号が、有効タイミングビン中に遷移するか、それとも無効タイミングビン中に遷移するかを判断することにより処理される。データ信号が無効タイミングビン中に遷移する場合、エラー信号を生成することができ、テストデータ信号を生成し、有効タイミングビン中に遷移するように後続のデータ信号を位相偏移させることにより、リンクを再トレーニングすることができる。 (もっと読む)

半導体装置

【課題】 タイミングマージンの改善を図った同期化回路を備えた半導体装置を提供する。

【解決手段】 第1導電型の第1と第2MOSの共通ソースと第1電位との間に第1導電型第3MOSを設け、第2電位と上記第1と第2MOSのドレインと間に第2導電型の第4と第5MOSを設け、上記第4と第5MOSに並列形態にゲートとドレインが交差接続された第2導電型の第6と第7MOSを設ける。上記第1MOSのゲートに入力信号を供給し、上記第2MOSのゲートを上記第1MOSのドレインに接続し、上記第3MOSのゲートにクロックを供給し、上記第4と第5MOSのゲートに上記クロックと同相クロックを供給して、上記第1と第2MOSのドレインから第1、第2信号を出力してRSフリップフロップ回路に伝える。

(もっと読む)

半導体論理回路におけるクロック分配回路およびその方法

【課題】クロック同期回路を使用した半導体論理回路において、より効果的に消費電力を減少して動作するクロック分配回路およびその方法を提供。

【解決手段】クロック分配回路10は、クロックイネーブル信号102に応じてクロック生成回路20ならびに22でゲーテッドクロック信号108ならびに110を生成し、クロック同期回路12および14、ならびに16および18に供給することにより、クロック信号のトグルで消費していた電力を減少することができる。

(もっと読む)

1 - 13 / 13

[ Back to top ]