Fターム[5J043DD08]の内容

Fターム[5J043DD08]に分類される特許

1 - 20 / 26

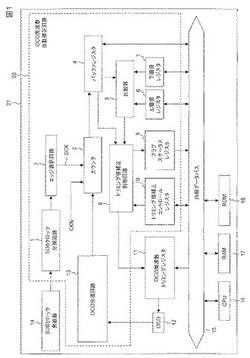

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

ディジタル発振器

【課題】ルックアップテーブル方式のようなメモリを使用せずに、正弦波、余弦波、角度情報が同時に得られるようにしたディジタル発振器を提供する。

【解決手段】初期値Aが設定されクロックで動作する第1の積分器5A、外部入力するアップ/ダウン信号でωの極性が切り替わる第1のω係数器6B、前記クロックで動作する第2の積分器5B、および前記アップ/ダウン信号でωの極性が前記第1のω係数器6Bのωの極性と反対に切り替わる第2のω係数器6Aを順次リング接続して2相発振器を構成する。また、前記アップ/ダウン信号に応じて前記クロックをアップ/ダウンカウントするアップ/ダウンカウンタからなる角度取得ユニット3を設ける。前記第1の積分器5AからAcosωtを、前記第2の積分器5BからAsinωtを、前記角度取得ユニット3から角度情報ωtを、それぞれ同時に生成する。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

パルス生成装置

【課題】パルス信号の周期及びデューティ比を、相互に影響を与えることなく独自に設定可能にしたパルス生成装置を提供すること。

【解決手段】本発明にかかるパルス生成装置は、パルス周期を設定する信号を入力し、パルス周期を制御する周期制御信号を出力する周期設定手段11を備える。また、パルスのデューティ比を設定するデューティ比設定信号を入力するとともに、周期設定手段において設定されるパルス周期を含む信号を入力し、当該パルス周期とデューティ比設定信号に基づいて、パルスのデューティ比を制御するデューティ比制御信号を生成するデューティ比設定手段12を備える。さらに、周期制御信号とデューティ比制御信号に基づいて、設定された周期及びデューティ比を有するパルス信号を生成するPWM出力発生手段13を備えることを特徴とする。それにより、パルス周期に影響されることなくパルスのデューティ比を決定することが可能である。

(もっと読む)

信号生成装置およびD級増幅装置

【課題】パルス幅変調に起因した電磁干渉を抑制する。

【解決手段】周期制御部30は、各単位期間Uの時間長TUを可変に制御する。パルス幅変調部20は、保持部22と計数部24と波形生成部26とで構成される。保持部22は、順次に供給される複数のデータXDを単位期間U毎にデータXEとして保持する。計数部24は、各単位期間U内で計数値Cを変化させる。波形生成部26は、保持部22が保持するデータXEの数値と計数値Cとの大小が反転する時点を縁部とするパルスPを単位期間U毎に配置したパルス幅変調信号Sを生成する。

(もっと読む)

クロック生成回路

【課題】電源電圧の変動等による出力クロックへの影響を低減する。

【解決手段】基準クロックを生成する自走発振器10と、この基準クロックに同期してカウントするカウンタを有し、外部より入力される入力クロックの周期毎のカウンタのカウント値を保持して並列出力するクロックカウンタ40と、クロックカウンタ40の出力値に応じたクロック周波数のシリアル信号を基準クロックに同期させて出力するクロック分周器70を備え、クロックカウンタ40とクロック分周器70との間に、クロックカウンタ40の出力値の瞬時的な変動を抑制するフィルタ60を備える。

(もっと読む)

発振装置、その調整方法及びメモリ装置

【課題】簡単に発振信号の周期のばらつきを防止することができる発振装置、その調整方法及びメモリ装置を提供することを課題とする。

【解決手段】イネーブル信号に応じて発振信号を生成する発振器(105)と、前記発振信号の発振数をカウントし、第1の信号で指定された発振数でリセットするかしないかの選択を行うことができるカウンタ(106)と、前記カウントされた発振数及びリファレンス数を比較する比較器(107)とを有することを特徴とする発振装置が提供される。

(もっと読む)

温度センサー及びこれを用いる半導体メモリ装置

【課題】温度センサー及びこれを用いる半導体メモリ装置を提供する。

【解決手段】温度特性を持つ基準電圧によってイネーブル区間幅が調節される第1パルス信号を生成するパルス信号生成部と、前記第1パルス信号のイネーブル区間の間に所定周期の第2パルス信号を生成するオシレータと、前記第2パルス信号に応答してカウンティング動作を行って少なくとも一つの温度信号を生成するカウンタと、を備える。

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

クロック出力制御回路、装置、クロック出力制御方法

【課題】クロック供給開始までの時間を短縮すること。

【解決手段】OCXO102の発振器のクロック出力の安定度を確保するために、電源101を入れてから一定時間経過するまで発振器の生成クロックの出力を停止するクロック出力制御回路であって、取得した外部の基準クロックに基づいて発振器の生成クロックの周波数安定度が所定値以内であるか判定し、保証時間経過以前であっても、所定値以内である時点で、生成クロックの出力を許可する。

(もっと読む)

クロック生成装置

【課題】クロック生成装置において、リングオシレータが高温になるのを抑える。

【解決手段】クロック生成装置10は、リングオシレータ13の出力信号を割り算器19が算出した分周比で分周する第一分周器21と、第一分周器の出力信号をニ分周する第二分周器23と、リングオシレータの出力信号のパルス数を所定時間計測するカウンタ15,25と、割り算器と、比較器29とを備える。割り算器は、第一分周器からの出力信号が、所定周波数のクロック信号となるよう第一分周器に設定する分周比を演算する。一方、比較器は、カウンタのカウント値と閾値とを比較し、カウント値が閾値以上である場合、第二分周器に入力するイネーブル信号をオフにして、第二分周器の分周機能をオフし、カウント値が閾値未満である場合には、イネーブル信号をオンにして、第二分周器の分周機能をオンにする。これにより、リングオシレータが高温の時、クロック周波数を半減させる。

(もっと読む)

接触感知センサー及びその動作方法

本発明は、接触感知センサー及びその動作方法を公開する。この装置は、制御コードに応答してパルス幅が補正されるパルス信号を発生するパルス信号発生部と、接触パッドに接触物体が非接触されれば、パルス信号を伝達し、接触パッドに接触物体が接触されれば、パルス信号を伝達しないパルス信号伝達部と、パルス信号伝達部を介して伝達されるパルス信号を検出するパルス信号検出部と、パルス信号が検出されれば、非接触状態であることを通知し、制御コードを調整してパルス信号のパルス幅を補正する制御部とを備えることを特徴とする。したがって、接触物体の接触感知動作が一層正確になるようにすると共に、動作環境が変化して接触感知センサーが誤動作することを事前に防止し、接触感知センサーの動作信頼性を増大させる。  (もっと読む)

(もっと読む)

パルス信号生成装置

【課題】マルチプレクサやD型フリップフロップ回路等による伝送遅延を回避しつつ、パルス幅が所定幅を下回らないようにすることができるパルス信号生成装置を提供する。

【解決手段】所定のクロック信号が伝達され、該クロックに応じてパルスレベルと非パルスレベルを切り替えることによりパルス信号を生成するパルス信号生成部を備えたパルス信号生成装置において、前記パルス信号がパルスレベルとなっている間であって、該信号のパルス幅が所定幅に達するまでは、前記伝達を遮断して前記切り替えが生じないようにしたパルス信号生成装置とする。

(もっと読む)

半導体装置

【課題】第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置に関し、チップサイズの小型化が可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置であって、第1のクロックを生成する第1のクロック生成部と、第2のクロックを生成する第2のクロック生成部と、第1のクロック又は前記第2のクロックのいずれかを選択し、出力する選択部と、クロック選択部で選択されたクロックから第1の制御クロックを生成し、第1の制御部に供給するとともに、クロック選択部で選択されたクロックから第2の制御クロックを生成し、第2の制御部に供給する制御クロック生成部とを有することを特徴とする。

(もっと読む)

1 - 20 / 26

[ Back to top ]