Fターム[5J055DX04]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | バイポーラトランジスタ (323) | nPn (87)

Fターム[5J055DX04]に分類される特許

81 - 87 / 87

インタフェース回路

【課題】 P1形およびP2形のうちの所望の形式で使用することができ、応答速度が速いインタフェース回路を提供する。

【解決手段】 インタフェース回路をP1形で使用する場合は端子T4とT6を接続し、P2形で使用する場合は端子T5とT6,T7とT8をそれぞれ接続する。車両感知信号/Dが活性化レベルの「L」レベルになると、P1形の場合はフォトトランジスタ6が導通せず、出力端子T2,T3間が非導通状態になり、P2形の場合はフォトトランジスタ6が導通し、出力端子T2,T3間が導通状態になる。従来のフォトMOSトランジスタの代わりにフォトトランジスタ6を使用したので、応答速度が速くなる。

(もっと読む)

差動型論理回路

【課題】 信号の減衰を招くことなく且つ信号の差動性を保ったまま、電源の低電圧化が図られた差動型論理回路を提供する。

【解決手段】 MOSトランジスタ11_11,11_12からなる第1の差動増幅器11_10と、MOSトランジスタ11_21,11_22からなる第2の差動増幅器11_20のうちのいずれか一方の差動増幅器を選択する選択信号に応じて中心電位が相互にシフトした2つの相補信号である差動電圧信号A,Abおよび差動電圧信号B,Bbを生成して、差動増幅器11_10および差動増幅器11_20に入力する。

(もっと読む)

PWMモータ駆動回路

【課題】高速で小型、低損失で信頼性の高いPWMモータ駆動回路を実現する。

【解決手段】ソースを電源+VDDと接続したPチャンネルMOSFETトランジスタTru+ とソースをGNDと接続したNチャンネルMOSFETトランジスタTru- のドレインを接続し、モータコイルの出力とする。また、前記PチャンネルMOSトランジスタTru+ のソースとゲート間にバイアス抵抗R4を接続し、その抵抗R4と並列にソースとゲートを前記PチャンネルMOSトランジスタTru+ のオフ時に短絡するトランジスタQ2を設けるとともに、前記ゲートとコレクタを接続し、ベースを電源+VDDに接続した入力用のNPNトランジスタQ1のエミッタをマイコン2のポートP1に接続する。一方、前記NチャンネルMOSトランジスタTru- のゲートをマイコン2のポートP2と接続して両ポートP1、P2から駆動信号を入力する。この回路を用いることで簡便で高速動作ができて小型化が図れ、低損失で信頼性の高いPWMモータ駆動回路を実現する。

(もっと読む)

シリコンゲルマニウム・ヘテロ結合バイポーラトランジスタを使用した高速クロスポイントスイッチ及び方法

【解決手段】高速クロスポイントスイッチは、好適にはシリコン基板上に設けられ、バイポーラトランジスタスイッチング素子を使用する。バイポーラトランジスタはSiGeバイポーラ接合トランジスタである。交差する導電性入力及び出力マイクロストリップは、好適にはそれらの交点で細く形成されて結合線間のシャントキャパシタンスを減少する。また、入力バッファは、増幅段を形成するために、スイッチングトランジスタとカスコード状に接続されることが好ましい。信号及びその逆信号は、平衡線路対の中央での電磁場強度を減少するために平衡マイクロストリップに搬送されることにより、2個の交差平衡対間の隔離を改良する。  (もっと読む)

(もっと読む)

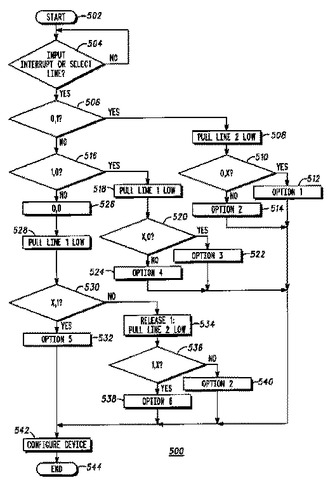

携帯機器のための割り込み駆動の拡張型オプション選択インタフェース

携帯電子機器(102)には周辺コンポーネント(104)が取り付けられ、この周辺コンポーネント(104)はオプション選択回路を使用して周辺コンポーネントのオプションクラスを示す。オプション選択回路は、携帯電子機器に割り込みを生成し、次いで種々のオプション論理ラインの論理レベルの変更により、オプションクラスを決定する。オプション選択ラインのうちの一つの論理状態の反転が検知されると、携帯電子機器はオプション選択回路のプレゼンスを知り、従って周辺コンポーネントのオプションクラスを決定する。  (もっと読む)

(もっと読む)

無線周波数用双極単投スイッチ

【解決手段】本発明の双極単投(DPST)スイッチは、第1入力ポートに対応する第1回路部と、第2入力ポートに対応する第2回路部と、及び出力ポートを有するスイッチ回路とを具備する。ここで、第1及び第2の回路部の各々は、分離チャンネルの一部を提供する少なくとも1個の第1トランジスタと、送信チャンネルの一部を提供する少なくとも1個の第2トランジスタと、送信チャンネル又は分離チャンネルのいずれかを選択する制御バイアスを提供する少なくとも1個の第3トランジスタとを有する。 (もっと読む)

整流器

【課題】 簡易な構成で、低損失で交流を整流することができる整流器を提供することである。

【解決手段】 p型半導体からなるベースBとサブエミッタSは、互いに接しないようにして、n型半導体からなるコレクタCに接合されている。n型半導体からなるエミッタEは、ベースBに接合されている。ベースB−エミッタE間には抵抗器Rが接続され、サブエミッタSにはバイアス用電源VBの正極が接続され、エミッタEには負極が接続される。コレクタCとエミッタEが実質的に同電位となったとき、ベースB−サブエミッタS間が導通して抵抗器Rに電圧降下が生じるが、コレクタC−エミッタE間は導通しない。コレクタCを基準としたエミッタEの電圧が更に低下すると、コレクタC−エミッタE間が導通する。

(もっと読む)

81 - 87 / 87

[ Back to top ]