Fターム[5J055EX04]の内容

Fターム[5J055EX04]に分類される特許

1 - 16 / 16

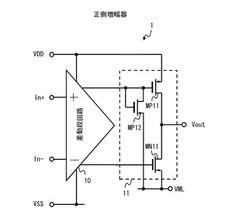

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

スイッチモジュールおよびそれを用いた試験装置

【課題】半導体スイッチの低周波数領域での歪み特性を改善する。

【解決手段】制御ポートP3には、制御電圧VCが入力される。伝送路10は、入力ポートP1と出力ポートP2の間を接続する。シャントスイッチ20は、伝送路10と接地端子の間に設けられる。シャントスイッチ20は、そのドレイン、ソースの一方が伝送路10と接続され、そのドレイン、ソースの他方が接地端子に接続されるFET22を備える。第1抵抗R1は、FET22のゲートと制御ポートP3の間に設けられる。第2抵抗R2は、FET22のゲートと伝送路10の間に設けられる。

(もっと読む)

ゲートドライブ回路

【課題】ターンオン時のスイッチング特性が変動せず、電力損失を発生せずにスイッチング素子を安定してターンオンさせることができるゲートドライブ回路。

【解決手段】ドレインとソースとゲートとを有し且つワイドバンドギャップ半導体かなるスイッチグ素子Q1のゲートに制御回路からの制御信号を印加することによりスイッチング素子をオンオフ駆動させるゲートドライブ回路であって、制御回路とスイッチング素子のゲートとの間に接続され、第1のコンデンサC1と第1の抵抗R1とからなる並列回路と、スイッチング素子のゲートとソースとの間に接続され、制御信号のオフ信号に対して遅延させてゲートとソースとの間を短絡する短絡手段S4とを備える。

(もっと読む)

高周波スイッチ回路、及び複合高周波スイッチ回路

【課題】 ゲート−ボディ間の電圧がMOSFETの耐圧以下とすることが可能な高い信頼性を有する高周波スイッチ回路を実現する。

【解決手段】 MOSFETと、前記MOSFETのゲート及びボディの電位を制御可能な制御回路を備えた高周波スイッチ回路であって、

前記制御回路はタイミング制御回路を備え、

前記タイミング制御回路は、前記高周波信号経路が接続状態から非接続状態に切り替わる時は、前記MOSFETのゲートの電位を切り替えた後にボディの電位を切り替えることが可能であり、かつ、非接続状態から接続状態に切り替わる時は、前記MOSFETのボディの電位を切り替えた後にゲートの電位を切り替えることが可能であることを特徴とする。

(もっと読む)

電力変換装置

【課題】本発明の課題は、電力変換装置における温度検出素子の時間変化率を検出し、温度上昇の事前予測によりフェールセーフをかけることで、発熱半導体素子の発熱抑制とモジュールケースの冷却構造最適化を実現することである。

【解決手段】上記課題を解決するために、前記半導体素子のモジュールケースまたは素子自体の温度の時間変化率を検出する検出手段と、素子のゲート抵抗値を可変にする抵抗可変回路とを設け、前記検出温度の時間変化率が所定の設定値以上になったと判断されたときは、ゲート抵抗値を前記抵抗可変回路により低減することを特徴とする電力変換装置を提供する。

(もっと読む)

ゲート駆動回路

【課題】 簡便な回路構成で、高速に動作するゲート駆動回路を提供することである。

【解決手段】 パワー半導体素子のゲート端子に正電圧を印加するためのNPNトランジスタと、パワー半導体素子のゲート端子に負電圧を印加するためのPNPトランジスタと、NPNトランジスタと、PNPトランジスタとに直列に接続された遮断用抵抗器と、遮断用抵抗器に、正極がパワー半導体素子のゲート端子側となるように並列に接続された遮断用抵抗器切換え半導体スイッチとを備えたゲート駆動回路である。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮する回路を提供する。

【解決手段】スイッチング回路10の入力端子21と出力端子22との間、入力端子21と共通端子23との間及び出力端子22と共通端子23との間の少なくとも一つに接続される容量抑制素子部50を備え、容量抑制素子部50は、容量抑制素子部が接続される半導体スイッチ素子20の端子間の寄生容量を、パルス状信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、容量抑制素子部が接続されていない場合より低減する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

電子制御装置

【課題】電流検出用の抵抗を使用せず、簡易回路で負荷ショートの保護が可能な電子制御装置を得る。

【解決手段】パルス発生源3と第2のスイッチング素子21との間に接続されたコンデンサ23を有するトリガ回路と、負荷4と第1のスイッチング素子11との交点と第2のスイッチング素子21のベース端子との間にダイオード25を介して接続されるラッチ回路を有する制御回路を備え、パルス発生源が駆動信号を出力時は、トリガ回路を介し所定時間第2のスイッチング素子21をオンし、第1のスイッチング素子11もオンさせ、前記交点の電圧で、ラッチ回路を介し第2のスイッチング素子21のオン状態を継続させる。駆動信号の停止時は、第1、第2のスイッチング素子は共にオフとし、負荷ショートが発生した時は、パルス発生源3の駆動信号が出力されている場合でも、交点の電圧で、ラッチ回路を介して第2のスイッチング素子21をオフし、第1のスイッチング素子11もオフする。

(もっと読む)

保護回路

【課題】シンプルな構成で保護対象となる回路を電源電圧の変動から確実に保護することができる保護回路を提供する。

【解決手段】エミッタに電源ライン1が接続され、コレクタに前記電源ライン1の電圧を電源電圧として動作する回路を含む需要回路2が接続されるPNPトランジスタTrと、前記電源ライン1の電圧が基準電圧よりも小さいときはロウレベルの電圧を前記PNPトランジスタTrのベースに印加し、前記電源ライン1の電圧が基準電圧よりも大きいときはハイレベルの電圧を前記PNPトランジスタTrのベースに印加する比較器3とを含む保護回路を構成する。

(もっと読む)

電源ショート保護回路

【課題】端子の電源ショート時にも電圧駆動素子およびシャント抵抗を保護する。

【解決手段】一端が端子T1に接続され、他端がシャント抵抗Rsを介して接地された電圧駆動素子10と、シャント抵抗Rsの電圧を検出する検出回路20と、検出回路20からの電圧検出信号で電圧駆動素子10をON/OFF制御する駆動回路30とを備える電源ショート保護回路において、電圧駆動素子10と並列にシャント抵抗Rsに比べて大きな抵抗値の抵抗素子R1を接続することにより、電圧駆動素子10のOFF時にもシャント抵抗Rsに電流を流して電圧を検出回路20で検出し、端子T1が電源ショートしているときには電圧駆動素子10をONさせないように駆動回路30を制御する。

(もっと読む)

電圧駆動型半導体スイッチング素子の駆動方法

【課題】 過電圧を抑制しながら、小型化、低コスト化を達成することができる電圧駆動型半導体スイッチング素子の駆動方法を提供する。

【解決手段】 オン状態またはオフ状態のIGBT3のゲート3gに、それぞれ所定のオフ用電圧値Voffまたはオン用電圧値Vonをゲート回路7から入力することによってオン、オフ制御を行うようにしたIGBT3の駆動方法で、一方の状態から他方の状態へ切り替える時、ゲート回路7からゲート3gに、先ず、オン用電圧値Vonまたはオフ用電圧値Voffの一方の電圧値からオン用電圧値Vonとオフ用電圧値Voffの間の所定中間電圧値まで所定の時間をかけて漸次変化するよう電圧値を入力し、その後、他方の電圧値を入力することによりオン、オフ制御を行う。

(もっと読む)

過電流検出装置

【課題】オン抵抗Ronが小さい場合でも、比較器CMP101のオフセット電圧Voffの影響を低減して高精度な過電流検出が可能な過電流検出装置を提供する。

【解決手段】

スイッチング用のFET(T1)のソースに接続された銅箔パターン4の所定点P2と、該FET(T1)のドレインP1との間の電圧(V1−V2)を過電流判定電圧として、比較器CMP1の入力端子に供給し、基準電圧V3と比較する。この際、銅箔パターン4が有する抵抗Rpによる電圧降下分が存在するので、電圧(V1−V2)はFET(T1)の端子間電圧VDSよりも大きくなり、結果として、比較器CMP1が有するオフセット電圧Voffによる影響を低減することができる。

(もっと読む)

可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器

【課題】パッケージサイズの縮小化を妨げることがなく、しかも低電圧・低消費電力系の素子と一体的に形成することが可能な程度に低電圧・低消費電力の可動素子、ならびにその可動素子を内蔵する半導体デバイス、モジュールおよび電子機器を提供する。

【解決手段】半導体基板10上に、信号を伝送するための信号線路11と、信号線路を機械的に継断するための継断部12と、継断部12を切り替えるための切替部13と、継断部12の切り替え後の状態を保持するための保持部14とを備える。継断部12および保持部14は互いに対向配置された一組の固定子12A,14Aおよび可動子12B,14Bを、切替部13は保持部14の可動子14Bと対向配置された可動子13Bをそれぞれ有する。切替部13の可動子13Bおよび保持部14の可動子14Bの少なくとも一方が、弾性部15を介して継断部12の可動子12Bと接続されている。

(もっと読む)

1 - 16 / 16

[ Back to top ]