Fターム[5J055EZ21]の内容

Fターム[5J055EZ21]に分類される特許

1 - 20 / 20

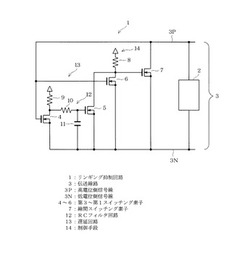

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮し、オーバドライブによらず速度の向上と電力効率の向上を図り得るスイッチング回路を提供する。

【解決手段】半導体スイッチ素子20a、20dがON(OFF)のとき残りの半導体スイッチ素子がOFF(ON)となるように、各半導体スイッチ素子の入力端子にパルス状信号が印加される。スイッチング回路は、半導体スイッチ素子20bの出力端子と半導体スイッチ素子20dの入力端子の間に接続されるキャパシタンス素子60と、半導体スイッチ素子20bの入力端子と半導体スイッチ素子の出力端子20dの間に接続されるキャパシタンス素子61とを備える。キャパシタンス素子60,61は、半導体スイッチ素子20b、20dの各々の入力端子と出力端子間の寄生容量を、半導体スイッチ素子20b、20dに供給されるパルス状信号のクロック周波数のN倍の周波数において低減する容量を有する。

(もっと読む)

スイッチング回路

【課題】半導体スイッチの寄生容量の充放電時間を短縮する回路を提供する。

【解決手段】スイッチング回路10の入力端子21と出力端子22との間、入力端子21と共通端子23との間及び出力端子22と共通端子23との間の少なくとも一つに接続される容量抑制素子部50を備え、容量抑制素子部50は、容量抑制素子部が接続される半導体スイッチ素子20の端子間の寄生容量を、パルス状信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、容量抑制素子部が接続されていない場合より低減する。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】半導体装置側において自動的にキャリブレーション動作を行う。

【解決手段】出力バッファ71のインピーダンスを調整するキャリブレーション回路100と、オートリフレッシュコマンドARが所定回数発行されたことに応答してキャリブレーション回路100を活性化させるキャリブレーション起動回路200とを備える。本発明によれば、コントローラ側からキャリブレーションコマンドを発行することなく、半導体装置側にて自動的にキャリブレーション動作を行うことが可能となる。しかも、オートリフレッシュコマンドARが所定回数発行されたことに応答してキャリブレーション動作を行っていることから、定期的なキャリブレーション動作が確保されるとともに、キャリブレーション動作中にコントローラからリード動作やライト動作を要求されることもない。

(もっと読む)

アンテナスイッチ回路及び通信端末

【課題】許容電力と挿入損出との特性を両立させるとともに、アンテナスイッチ回路の小型化を可能とし、且つスイッチング状態の更なる安定化を図ることができるようにする。

【解決手段】本発明によるアンテナスイッチ回路は、送信ポートとアンテナポートとの間に直列に接続された直列トランジスタ回路と、前記送信ポートと前記アンテナポートとの間に並列に接続された並列トランジスタ回路と、前記送信ポートと前記並列トランジスタ回路との間に設けられ、インピーダンス変換を行うことによって、前記送信ポートから入力された送信信号の電圧振幅を所定の変換比率で縮小するインピーダンス変換回路とを備え、前記インピーダンス変換回路は、前記並列トランジスタ回路に出力される端子間電圧が当該並列トランジスタ回路の閾値以下となるように前記所定の変換比率が設定されていることを特徴とする。

(もっと読む)

サンプリング回路

【課題】サンプリング回路の省電力化を図ること。

【解決手段】アンダーサンプリング方式のサンプリングミキサ回路30において、サンプリングパルス信号である制御信号S1,S2に従って、非サンプリング期間の間、増幅部321の入力端子と接続端子との間が接続されることで増幅部321の増幅動作のON/OFFが制御される。増幅部321の前段の整合回路31は、増幅部321の入力端子と出力端子との間が接続されていないとき、すなわち増幅動作が行われているサンプリング期間では入力インピーダンスを整合させ、増幅部321の入力端子と出力端子との間が接続されているとき、すなわち増幅動作が行われない非サンプリング期間では入力インピーダンスを不整合させる回路素子が選択されている。また、動作制御部323は、制御信号S3,S4に従って、非サンプリング期間の間、増幅部321のトランジスタTr1,Tr2の増幅動作を停止させる。

(もっと読む)

信号伝搬回路および信号処理装置

【課題】電気信号の検出を高感度にする。

【解決手段】基板11cをそなえるとともに、基板11cに、出力端に接続される終端抵抗とインピーダンスが実質的に整合し、入力端からの信号を伝搬する信号伝搬路11aと、信号伝搬路11aの途中箇所において信号伝搬路11aに非接触に形成された線路11b−1,11b−2と、をそなえる。

(もっと読む)

出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路並びに伝送方法

【課題】消費電力、回路面積を増やすことなく、プリエンファシス量の分解能を向上することが可能な出力バッファ回路、差動出力バッファ回路、調整回路及び調整機能付き出力バッファ回路、並びに伝送方法を提供する。

【解決手段】遅延回路23と、反転回路22と、出力バッファ3〜7とを備え、伝送線路2に論理信号を送信し、伝送線路2の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路10であって、出力バッファ3はオン抵抗に可変抵抗部分12を有し、可変抵抗値の変更によりプリエンファシス量が変更される。出力バッファ3は、前段にセクレタ20を有し、オン抵抗に可変抵抗部分12を有しており、反転回路22は、セレクタ論理により出力バッファ6に入力する信号を選択可能で、データ信号を反転し、そして、セレクタ論理のセレクト信号により、タップのプリエンファシス量を調整する。

(もっと読む)

電源制御装置

【課題】グランド断線時に該グランドを適切な電位に接続することができる電源制御装置を提供する。

【解決手段】スイッチ素子11及びスイッチ制御部12を有する制御回路10と、一方の端子20aがスイッチ素子11を介して直流電源4に接続され且つ他方の端子20bが接地電位部5bに接続された負荷20と、を有する電源制御装置1であって、スイッチ制御部12が、接地電位部5aに接続され且つ接地電位に向かうグランド電流Iを出力するグランド端子12aを有し、制御回路10が、グランド端子12aと接地電位部5aとの接続が切り離されたときに、グランド電流Iを負荷20を介して接地電位部5bに流すための負荷側バイパス手段15aを備えたバイパス部15を有し、負荷20が、グランド電流Iが流れたときに、グランド端子12aの電位がスイッチ制御部12が安定動作する電位となるインピーダンスを有する。

(もっと読む)

出力バッファ回路、信号伝送インタフェース回路および装置

【課題】プリエンファシス機能を有する出力バッファ回路の、調整可能なプリエンファシス量を調整して、実使用状態の擬似的な伝送損失を実現して、LSI単体または短い配線を接続した状態で、受信回路の性能テストを実施する出力バッファ回路を提供する。

【解決手段】伝送線路に論理信号を送信する出力バッファ回路であって、送信プリエンファシス出力回路3と、送信プリエンファシス量決定回路4を有する。送信プリエンファシス出力回路3は、送信プリエンファシス量決定回路4の出力信号によりプリエンファシス量を制御している。送信プリエンファシス量決定回路4は、擬似損失制御信号により、プリエンファシス量とプリエンファシスタップ数を調整し、送信信号のプリエンファシス量が、低い周波数の信号成分より高い周波数の信号成分ほど信号振幅が小さくなるように制御し、受信波形に信号劣化を与えて擬似的に伝送損失を実現する。

(もっと読む)

分配器

【課題】出力ポートに接続された後段回路のインピーダンスが変動した場合でも、定在波比、及び、通過特性の周波数特性の悪化を低減することができる分配器を提供する。

【解決手段】 1つの入力ポートPinと、後段回路21、22が接続される2つの出力ポートPout1、Pout2とを有し、前記入力ポートPinから入力された信号を前記2つの出力ポートPout1、Pout2に分配して出力する分配器1であって、前記入力ポートPinから分岐した2つの出力端であるノードN1、N2を有し、入力ポートPinからみたインピーダンスを、前記後段回路21、22の第1インピーダンスに整合する分配回路10を備え、前記2つのノードN1、N2のそれぞれに、互いに等しい電気長Lc及び所定の特性インピーダンスZcを有する移相器13、14を設け、前記移相器13、14の出力端のそれぞれを前記出力ポートPout1、Pout2に接続する構成とした。

(もっと読む)

半導体集積回路

【課題】出力バッファの出力インピーダンスとスルーレートを同時に自動調整すること。

【解決手段】本発明に係る半導体集積回路は、出力データが出力される出力端子に接続された複数の出力トランジスタ(MP1〜MP3,MN1〜MN3)と、インピーダンス制御回路(100)と、スルーレート制御回路(10,20)とを備える。インピーダンス制御回路(100)は、複数の出力トランジスタのうち出力データの出力時にONされる出力トランジスタを指定する指定信号(PA〜PC,NA〜NC)を生成する。スルーレート制御回路(10、20)は、それらONされる出力トランジスタのそれぞれを駆動する駆動信号(P1〜P3,N1〜N3)を指定信号に基づいて生成し、且つ、それら駆動信号(P1〜P3,N1〜N3)のそれぞれの遅延時間を指定信号(PA〜PC,NA〜NC)に応じて可変に設定する。

(もっと読む)

マトリクススイッチ

【課題】任意の出力端子がオープン状態であっても、その出力端子に導通された各入出力端子のインピーダンス整合が取れるマトリクススイッチを提供する。

【解決手段】マトリクススイッチの各出力端子がそれぞれシャントを具備する。出力端子がオープン状態の時、出力端子にシャントが導通する。オープン状態の出力端子に導通した各入出力端子は、オープン状態の出力端子のシャントのインピーダンスで終端される。

(もっと読む)

出力回路

【課題】Lレベル出力時の動作電流を低減できる出力回路を提供する。

【解決手段】パルス生成部103は、入力信号DATAがLレベルに変化すると、そのタイミングから所定時間だけHレベルとなるパルスを発生する。メイン出力部101は、パルス生成部103がパルスを出力する間、トランジスタP1、N1、N2がオンになってLレベルの信号を出力する。パルスが立ち下がると、トランジスタP1、N1がオフになり、出力ノードDoutの電位は、Lレベル保持部102の抵抗R2、R3により、Lレベルに保持される。

(もっと読む)

入出力切換回路、それを搭載した半導体集積装置

【課題】 入出力切換回路に、特性悪化を抑制しながら入出力兼用の端子を設ける。

【解決手段】 第1セレクタ10は、外部から入力される複数の信号を選択する。第1オペアンプOP1は、第1セレクタ10の選択した信号を所定の増幅率で増幅する。第1出力端子32は、第1オペアンプOP1の出力信号を外部に出力する。第1出力端子32と第2セレクタ20との間には経路が設けられる。第1出力端子32から信号が入力される場合、第1オペアンプOP1をハイインピーダンス状態に設定する。第8抵抗34は、第1出力端子32から信号が入力される場合、終端抵抗として機能する。

(もっと読む)

半導体集積回路装置

【課題】 回路の簡素化を図りつつ、高い周波数でのデータ転送を含んだ多様な信号出力動作を可能にした半導体集積回路装置を提供する。

【解決手段】 複数の出力MOSFETの組み合わせによって複数通りの出力インピーダンスの設定が可能とされる出力回路に対して、入力信号の信号変化タイミングに対応して第1制御信号に基づいて伝送線路の特性インピーダンスよりも小さな第1出力インピーダンスにより出力信号を形成し、上記入力信号の信号変化タイミングにより遅れた第1時間経過後に第2制御信号に基づいて特性インピーダンスに整合された第2出力インピーダンスにより出力信号を形成するようにする。

(もっと読む)

コネクタ、車載バス駆動装置、保護回路、アダプタ、車載バス支線用ワイヤハーネス、車載バス支線用波形整形装置及び車載バス用ジョイントコネクタ

【課題】自動車における通信エラーを低減し、バス・トポロジ設計上、自由に通信ラインを設計できるようにする。

【解決手段】車載バス21の幹線7から車載バス駆動装置の最終出力段13に至る通信ライン中に抵抗17a,17bを挿入する。ケーブル・スタブ長が長くなっても、その反射量を減衰させることができ、通信ラインでのリンギングを減少させることができる。したがって、接続ノード数、バス長、ノード間距離等のバス・トポロジ上の制約を軽減することができ、通信ラインを自由に設計することが可能になる。抵抗17a,17bを挿入するだけでよいため、対策にかかるコストが低くて済む。

(もっと読む)

半導体リレー装置

【課題】 本発明は半導体リレー装置において、特性インピーダンスを改善することにより、その高周波特性を向上させることを目的とする。

【解決手段】 発光素子11と、発光素子からの光を受光する受光素子12と、受光によって生成された信号を受けて外部回路を動作させるスイッチ回路であるMOS素子13と、MOS素子13と外部回路とを接続する信号配線17a及び18aを有する半導体リレー装置10において、信号配線17a及び18aの特性インピーダンスを制御するグランド板を20信号配線17a及び18aに近接して、前記信号配線17a及び18aと直接接続することなく配置する。

(もっと読む)

1 - 20 / 20

[ Back to top ]