Fターム[5J055EZ48]の内容

Fターム[5J055EZ48]に分類される特許

1 - 20 / 26

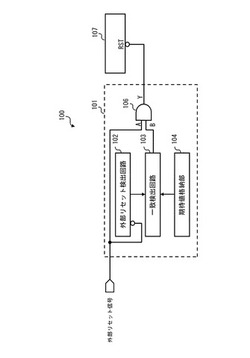

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

負荷駆動装置及び負荷駆動制御装置

【課題】パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

(もっと読む)

半導体装置、出力回路、及び、半導体装置における入出力バッファ回路の制御方法

【課題】異なる電源電圧で使用されることが考えられる半導体装置において、好適な出力回路を有する半導体装置を提供する。

【解決手段】少なくとも出力端子の機能を有する信号端子と、電源端子と、電源端子から電源電圧が供給され内部出力信号を受けて信号端子を駆動する第一及び第二の出力バッファ回路を備えた出力回路と、電源電圧を判定し出力回路の動作を制御する電源電圧判定回路と、を備え、電源電圧判定回路が、第1の電位にあると判定したときには、第1の出力バッファ回路を活性化させると共に、第2の出力バッファ回路を非活性化させ、第2の電位にあると判定したときには、前記第1、第2の出力バッファ回路を共に活性化させる。

(もっと読む)

電流発生回路及び表示装置

【課題】複数の単位電流を生成するための複数の電流トランジスタ備えて表示データの階調に応じた階調電流を生成する電流発生回路において、回路規模を小さくすること。

【解決手段】例えば8ビット(bit)データの場合、バイアス発生回路10の各出力端子から8つのそれぞれ電位レベルの異なる各バイアス電位VN1〜VN8を出力し、このバイアス発生回路10の各出力端子にチャネル幅(W)及びチャネル長(L)が同一に設定された8個の定電流トランジスタQ10〜Q17のゲート電極を接続して各定電流トランジスタQ10〜Q17にデータの各ビットに対応した単位電流を流し、これら電流トランジスタQ10〜Q17を選択的に動作させて、各単位電流を選択して生成した階調電流をディスプレイ5に供給する。

(もっと読む)

ヒューズ装置

【課題】切断したヒューズにグローバックが発生した場合にも、正確なヒューズデータを生成し得るヒューズ装置を提供する。

【解決手段】切断したグローバック検出用ヒューズf0の抵抗値と、第一の基準抵抗R0の抵抗値の差に基づく検出信号Xを生成するグローバック検出部11と、検出信号Xに基づいて抵抗値が変化する第二の基準抵抗TN9の抵抗値と、ヒューズデータ生成用ヒューズf1,f2,fnの抵抗値との比較結果をヒューズデータDAとして出力するヒューズ部13aとを備えた。

(もっと読む)

直流過電流遮断装置

【課題】直流給電において、負荷に過電流が流れた場合、負荷電流路を瞬時に自動的に遮断する。さらに、負荷短絡が発生した場合でも、瞬時に自動的に負荷電流路を遮断する。

【解決手段】第1コイルの一端に外部の直流電源の一方の極の電位が印加され、第1半導体素子の他端に外部の直流電源の他方の極の電位が印加されているとき、第1コイルの他端と第2コイルの他端間に所定の電流値を超えた電流が流れると、第1半導体素子の一端の電位により、第2制御端を制御し、さらに第2半導体素子の一端の電位により、第1制御端を制御し、第1半導体素子が有する電流路を遮断する。

(もっと読む)

駆動能力調節回路及びデータ出力回路

【課題】ヒューズのカッティング有無によってスペックで定められた駆動力以外の駆動力にデータドライバの駆動力を調節できるようにすることによって、使用者の要求に合わせてデータドライバの駆動力を容易に調節できるようにした駆動能力調節回路及びデータ出力回路を提供する。

【解決手段】ヒューズのカッティング有無によってヒューズ信号を生成するヒューズ信号生成部と、前記ヒューズ信号に応答して選択信号を生成する選択信号生成部と、設定信号を受信し、前記選択信号に応答して駆動制御信号を生成する駆動制御信号生成部と、前記駆動制御信号をデコーディングして駆動信号を生成する駆動信号生成部と、を含む駆動能力調節回路を構成する。

(もっと読む)

バッファ回路

【課題】 複数のパッドに対応して、半導体メモリ装置で占める面積が減ったバッファ回路を提供する。

【解決手段】 半導体メモリ装置のバッファ回路は、差動増幅構造のインタフェース部と共通バイアス供給部とを含み、前記インタフェース部は複数の入力信号にそれぞれ対応し、前記各入力信号と共通バイアス信号とを差動増幅し、前記共通バイアス供給部は基準電圧によって、駆動されることによって前記共通バイアス信号を前記各インタフェース部に共通で提供する。このような構成により本発明によるバッファ回路が占める面積が減ることができるという効果がある。

(もっと読む)

IC内のヒューズ・プログラミング電流を制御するためのシステムおよび方法

【課題】自動的に適切なプログラミング電流を決定して印加するためのシステムを提供する。

【解決手段】システムは、複数の測定ヒューズに複数の相違する電流を流し、複数の測定ヒューズの対応するものを破壊することなく切断した1つまたは複数の電流を特定し、特定された電流のうちの1つを自動的に選択するように構成されている測定回路と、選択された電流で1つまたは複数の目標ヒューズをプログラムするように構成されているプログラミング回路と、を具備する。

(もっと読む)

半導体集積回路

【課題】簡単な回路構成を用いながら、ヒューズを切断するか否かによってリセット信号のパルス幅を変更することができる半導体集積回路を提供する。

【解決手段】この半導体集積回路は、リセット信号が供給される第1のノードとリセット信号が出力される第2のノードとの間に直列に接続され、抵抗をそれぞれ含む複数の第1の回路と、第2のノードと基準電位との間に並列に接続され、容量をそれぞれ含む複数の第2の回路と、第1のノードに供給されるリセット信号と第2のノードから出力されるリセット信号とを用いて論理演算を行うことにより、リセット信号のパルス幅を調節して出力する論理回路とを具備し、複数の第1の回路の内の少なくとも1つにおいて、抵抗と並列にヒューズが接続されており、複数の第2の回路の内の少なくとも1つにおいて、容量と直列にヒューズが接続されている。

(もっと読む)

パワー半導体装置

【課題】一度異常が検出されたなら、電源を遮断しても継続的に通電を制限できるパワー半導体装置を提供する。

【解決手段】制御信号が入力される外部制御端子8と、出力電流が流入または流出する2つの外部出力端子3,4と、出力電流を制御するパワー半導体素子2とを有する半導体装置1に、パワー半導体素子2の動作状態に応じた電気信号を出力する動作状態検出回路6と、動作状態検出回路6の出力が入力され、動作状態検出回路6の出力がパワー半導体素子2の異常を示す値になると所定の出力状態となり、電源が遮断されても所定の出力状態を保持し続ける不揮発性の状態保持回路7と、前記制御信号および状態保持回路の出力に応じて、パワー半導体素子2の出力を制限する制御回路5とを設ける。

(もっと読む)

負荷駆動制御装置

【課題】電流駆動素子の温度異常時にも負荷への通電を継続させた上で、電流駆動素子を確実に保護可能な負荷駆動制御装置を提供する。

【解決手段】電流駆動素子であるトランジスタの温度が過剰に高い温度異常状態かどうかかが判定され(S101)、温度異常状態でない場合には(S101:No)、トランジスタがPWM制御される。また、温度異常状態であり(S101:Yes)、且つ、トランジスタがPWM制御中の場合には(S102:Yes)、トランジスタがフルON固定状態に制御される(S103)。そして、温度異常状態であり、且つ、トランジスタがPWM制御中でない場合には(S102:No)、トランジスタを制御するための制御信号のデューティ比やスイッチング周波数を低い値に設定することにより、フルON固定状態にした場合よりもスイッチング損失が低くなるようにトランジスタが低損失制御される(S104)。

(もっと読む)

半導体集積回路

【課題】製造工程上のばらつきを高精度で補正することができ、かつ、回路の大規模化を抑えることができる半導体集積回路を提供する。

【解決手段】この半導体集積回路は、第1の電位と第2の電位との間に直列に接続され、第1の電位と第2の電位との間の電圧を分圧することにより複数の電圧を生成する複数の抵抗と、複数の抵抗の内の少なくとも1つに並列に接続された少なくとも1つのスイッチ回路と、複数の抵抗の内の少なくとも他の1つに並列に接続された少なくとも1つのヒューズと、外部から供給される制御信号に従って、少なくとも1つのスイッチ回路をオン/オフさせるように制御する制御回路とを具備する。

(もっと読む)

電流異常検出回路及びその異常検出時電流値調整方法

【課題】電位制御回路に製造ばらつきがあっても正常に電流の異常を検出することが可能な電流異常検出回路及びその異常検出時電流値調整方法を提供する。

【解決手段】分圧回路40の下流側に配したバイアス抵抗42のバイアス電圧Vbを調整して、第1異常用閾値電圧Vocを第2異常用閾値電圧Vfcと同じ量だけ底上げするという1箇所に対する調整作業で「過電流異常」に検出精度の低下を抑制しつつ、高い検出精度が求められる「ヒューズ異常」についてオフセット電圧ΔV、第2異常用閾値電圧Vfc及び比較回路32のばらつきによる影響を一度に排除できる。

(もっと読む)

内部電圧発生回路

【課題】異なる目標電位を有する2種類以上の内部電位の生成の際にチャージポンプの動作時期を調節し、これらの電位の間に発生され得るラッチアップ現象を防止できるようにすること。

【解決手段】本発明の内部電圧発生回路は、ポンプ電圧を生成するポンプ電圧発生手段と、前記ポンプ電圧と周辺電圧とのレベルを比較し、イネーブル信号を出力するレベル比較器と、前記イネーブル信号に応じてポンプイネーブル信号を出力し、前記イネーブル信号に応じて前記周辺電圧を生成する周辺電圧発生手段とを備える。

(もっと読む)

半導体集積回路装置、電源装置、電気機器

【課題】本発明は、安価な手段によって、より安全性の高い温度保護動作を行うことが可能な半導体集積回路装置、並びに、これを備えた電源装置及び電子機器を提供することを目的とする。

【解決手段】本発明に係るスイッチング電源IC1は、監視対象温度が第1閾値温度に達したときには、遮断信号Stsd1に応じて、スイッチN1、N2をいずれもオフさせる一方、監視対象温度が第1閾値温度よりも高い第2閾値温度に達したときには、遮断信号Stsd2に応じて、外部接続されたフューズF1を溶断すべく、スイッチN1、N2をいずれもオンさせる構成とされている。

(もっと読む)

ヒューズ切断テスト回路及びヒューズ切断テスト方法並びに半導体回路

【課題】

不完全な切断状態の検出まで含めたヒューズの切断判定を高速且つ高精度に行うこと

【解決手段】

本発明に係るヒューズ切断テスト方法は、ヒューズの状態をテストするヒューズ切断テスト方法であって、当該ヒューズに流れる電流の値に基づいて、当該ヒューズの切断、非切断及びその中間の状態のいずれかを判断するヒューズ切断テスト方法。これにより、不完全な切断状態の検出まで含めたヒューズの切断判定を高速且つ高精度に行うことができる。

(もっと読む)

半導体装置

【課題】ヒューズに直列にプルダウン抵抗を配置するのみで、論理状態をラッチすることができ、貫通電流を一定値以下に抑えつつ、回路構成がより簡単な制御回路を提供する。

【解決手段】制御パラメータ情報の情報格納部は、電源とプルダウン抵抗との間に接続されており、電源投入後の初期化信号に基づき非導通となる第1のスイッチと、第1のスイッチと直列に接続されたプルダウン抵抗と、プルダウン抵抗と直列に接続され、接地された初期化信号に基づき導通後に非導通となる第2のスイッチからなる制御部によって制御パラメータ情報が抽出され、抽出された制御パラメータ情報は情報保持部で保持される。

(もっと読む)

1 - 20 / 26

[ Back to top ]