Fターム[5J056CC14]の内容

Fターム[5J056CC14]に分類される特許

1 - 20 / 577

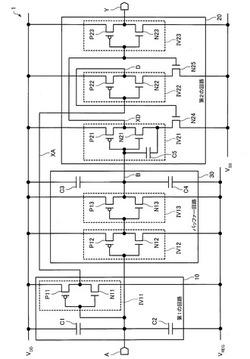

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置

【課題】プルアップ又はプルダウンのための専用端子を設けず、ソフトウェアによる初期化を待たずにプルアップ又はプルダウンの有無を設定する。

【解決手段】複数の端子を有する半導体装置であって、複数の端子を任意の数の端子毎に任意の数のグループにそれぞれ区分する第一の区分手段と、区分されたグループのそれぞれに含まれる任意の数の端子を、マスタ端子とスレーブ端子とに区分する第二の区分手段と、マスタ端子に対して論理レベルの設定を行う論理レベル設定手段と、マスタ端子に設定された論理レベルに応じて、スレーブ端子をプルアップ状態又は開放状態に切り替える切り替え手段と、を含む。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体装置

【課題】より少ない調整ステップでキャリブレーションを完了する。

【解決手段】出力端子(DQに相当)と、出力端子と接続され、出力端子を調整可能なインピーダンスで駆動する出力回路(210に相当)と、出力回路のインピーダンスを段階的に調整するキャリブレーション回路(100)と、を備え、キャリブレーション回路は、キャリブレーション動作の実行を指示するコマンドを受けて、インピーダンスの調整を開始し、インピーダンスを変化させる変化幅を、開始直後に対し以降においてより狭めるように調整する。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

集積回路装置

【課題】断熱動作を行う回路への電源電圧の供給を最適化することで好適な動作特性を実現する。

【解決手段】集積回路装置が、CPU10と電源生成回路40とを具備している。当該集積回路装置が高速モードに設定されると、電源生成回路40が直流の電源電圧をCPU10に供給する。この場合、CPU10は、通常のCMOS動作を行う。一方、当該集積回路装置が小電力モードに設定されると、電源生成回路40が交流の電源電圧をCPU10に供給する。CPU10は、複数の交流の電源電圧が供給されることで断熱動作を行う。該交流の電源電圧の少なくとも2つの電源電圧は、互いに、プルアップ及び/又はプルダウンのタイミングと、デューティ比とが異なっている。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

低いデューティサイクル歪みを有するレベルシフタ

【課題】低いデューティサイクル歪み及び高い電源電圧マージンの高速レベルシフティング回路を提供する。

【解決手段】レベルシフタ100は、反転回路104と、クロス接続されたレベルシフティングラッチ102と、SRロジックゲートラッチ103とを含み、レベルシフティングラッチ102の第1、第2出力は、SRロジックゲートラッチ103のセット(S)入力ノード121およびリセット(R)入力ノード120に接続され、反転回路104は、レベルシフティングラッチ102の第1入力ノード112に非反転の信号を供給すると共に、第2入力ノード113に反転の信号を供給し、入力信号のロウからハイへの変化はSRロジックゲートラッチ103をリセットし、ハイからロウへの変化はSRロジックゲートラッチ103をセットするように構成されている。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

半導体装置、及び出力バッファのインピーダンスを調整する方法

【課題】出力バッファのインピーダンスを制御する複数の制御ビットを転送するデータバスの配線面積を削減できる半導体装置、及び出力バッファのインピーダンスを調整する方法を提供する。

【解決手段】インピーダンス制御情報を生成するZQ回路(ZQ回路40)と、前記インピーダンス制御情報を受けて自身のインピーダンスが制御される出力バッファ(出力回路80)と、を備え、前記インピーダンス制御情報を構成する複数の制御ビット情報は前記ZQ回路からシリアルに転送される。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

1 - 20 / 577

[ Back to top ]