Fターム[5J056CC15]の内容

Fターム[5J056CC15]に分類される特許

1 - 17 / 17

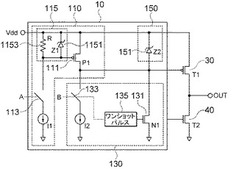

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

レベルシフト回路、および電力変換装置

【課題】電源電圧の変動の際に、半導体装置の製造ばらつきがあったとしても、容易に誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達するレベルシフト回路を提供する。

【解決手段】レベルシフト回路において、高電圧側の電源電圧変動dV/dtが回路のロジックレベルに影響を与える程度に発生した時において、この変動はセット側にもリセット側にも起こることを利用し、時定数生成回路、もしくは電源電圧変動が先に起こる個所からの信号によって、第1、第2の論理回路において、誤動作の信号が通過するのをマスクして防止する。このマスクするタイミングに充分、余裕をとることにより、半導体プロセスにおける製造ばらつきが個々の素子にあったとしても、高電圧側の電源電圧変動dV/dtが発生時の誤信号がフリップフロップに伝わるのを防止でき、誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達する。

(もっと読む)

電源回路

【課題】どの条件下でも一定のパルス幅で駆動する電源回路を提供する

【解決手段】電源回路10は、外部回路20と接続可能である。電源回路10は、一定の内部電圧を外部回路20に印加するフィードバック回路12と、パルスのパルス幅に応じた電荷を外部回路20に供給する電荷供給回路14と、外部回路20のオペレーションに対応するオペレーション状態に依存しない一定のパルスを電荷供給回路14に供給する電源制御回路16と、備える。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

入出力回路

【課題】消費電力の増大を防止することが可能な入出力回路を提供する。

【解決手段】本発明の入出力回路は、信号の入力部に接続された第1トランジスタと、前記第1トランジスタのゲートに接続されたノードの電位を制御するための第2トランジスタと、所定電圧に基づいて前記第2トランジスタを制御するためのバイアス電圧を生成し、当該バイアス電圧を前記第2トランジスタのゲートに印加するバイアス回路と、前記入力部と出力端子との間に設けられたインバータと、一方の入力に内部電圧が印加され、他方の入力に前記インバータの出力が接続された排他的論理積回路と、前記第1トランジスタのゲートと前記排他的論理積回路との間に設けられ、前記入力部の電位に基づいて前記第1トランジスタのゲートと前記排他的論理積回路との接続を導通/遮断するトランスファゲートとを有することを特徴とする。

(もっと読む)

双方向バッファ回路及び信号レベル変換回路

【課題】データ転送レートを高く保ちつつ、構成が簡素な双方向バッファ回路及び信号レベル変換回路を提供する。

【解決手段】第1の端子からの信号が入力され、第2の端子へ出力する第1の出力バッファと、前記第1の端子からの信号と前記第2の端子からの信号との論理演算により、第1の制御信号を出力可能な第1の制御回路と、前記第1の制御信号により前記第2の端子を一時的に駆動可能な第1のワンショットバッファと、前記第2の端子からの信号が入力され、前記第1の端子へ出力する第2の出力バッファと、前記第1の端子からの信号と前記第2の端子からの信号との論理演算により、第2の制御信号を出力可能な第2の制御回路と、前記第2の制御信号により前記第1の端子を一時的に駆動可能な第2のワンショットバッファと、を備える。

(もっと読む)

レベルシフト回路

【課題】レベルシフトを高速に動作させる。

【解決手段】入力部2は、入力信号の立ち上がりで第1のワンショットパルス信号を生成し、入力信号の立ち下がりで第1のワンショットパルス信号と同極性の第2のワンショットパルス信号を生成し、生成した第1および第2のワンショットパルス信号を出力信号によって消失させる。レベルシフト部3は、第1のワンショットパルス信号の信号レベルを変換するレベル変換回路LS1と、第2のワンショットパルス信号の信号レベルを変換するレベル変換回路LS2とを含む。出力反転部4は、レベル変換された第1および第2のワンショットパルス信号に対応して駆動され、出力信号を生成する。保持回路1は、生成された出力信号のレベルを保持する。

(もっと読む)

半導体集積回路装置

【課題】負荷を短時間で安定状態にすることが可能な半導体集積回路装置を提供する。

【解決手段】例えば、スタートアップ回路ST−UPと、電流バイアス回路IBIASと、温度補正回路T−CPSと、スイッチ回路SW1,SW2と、プリチャージ回路PC1,PC2と、PMOSトランジスタMP1,MP2を備えた定電流回路ISを設ける。ST−UPは、イネーブル信号ENを受けて1ショットパルス信号を生成する。IBIASは、MP1のゲートを駆動し、例えば正の温度特性を備えた電流I1を生成する。T−CPSは、MP2のゲートを駆動し、例えば負の温度特性を備えた電流I2を生成する。SW1,SW2は、ENが非活性の際にIBIASおよびT−CPSの電源を遮断する。PC1,PC2は、ST−UPからの1ショットパルス信号を受けて、MP1,MP2を一定期間オーバードライブする。

(もっと読む)

出力回路

【課題】出力信号のリンギングを抑制することのできる出力回路を提供する。

【解決手段】ドライブトランジスタ(1)は、内部信号に応答して第1の電源ノード(300)上の電圧を出力ノード(6)へ伝達する。比較回路(490)は、内部信号出力タイミングを規定するクロック信号(φck)に応答して活性化されて、第1の電源ノード(300)上の電圧と基準電圧(Vref)とを比較する。トランジスタ素子(492)が、比較手段の出力信号に応答して第2の電源ノード(Vcc)と第1の電源ノードとの間に電流の流れを生じさせる。このとき、第1の電源ノードの電位上昇時間は、クロック信号の遷移時間よりも長い。

(もっと読む)

半導体装置の入出力回路

【課題】 pull−down抵抗が端子に設けられている場合においても、

AC特性を改善することを目的とする。

【解決手段】 半導体内部電源電圧よりも高電圧の外部信号線に接続される出力端子部6と、フローティングNウェルを有し複数のPチャネル型トランジスタ52、53、54とアナログスイッチ51aにより構成され半導体内部信号を外部へ出力するハイ側出力回路部と、複数のNチャネル型トランジスタ55、57が直列に接続され半導体内部信号を外部へ出力するロー側出力回路部とを備えた半導体装置の入出力回路において、前記アナログスイッチを構成するPチャネル型トランジスタ51aの閾値電圧を他のトランジスタの閾値電圧より低く設定した。

(もっと読む)

容量帰還を用いる信号ドライバのための方法およびシステム

エッジレートの制御回路及び方法は、多様な回路装置及び方法を用いてインプリメントされる。そのような方法の1つを使用して、バスの出力信号は、分離スイッチ(106)を用いてトランジスタ(108)のゲートから帰還コンデンサ(106)を切り離すことによって制御される。トランジスタ(108)は、出力信号を制御するのに用いられる。スイッチ(112)を用いて帰還コンデンサ(116)に選択的に結合される電荷分配コンデンサ(114)を用いて、所定量の電荷が、帰還コンデンサ(116)から取り除かれる。スイッチ(112)は、出力電圧に達した出力信号に応答してイネーブルとなり、かつ、基準電圧に達した電荷分配コンデンサ(114)に応答してディスエーブルとなる。  (もっと読む)

(もっと読む)

実装基板の電源制御装置および半導体基板

【課題】外部からの入力を完全に遮断して、低消費電力化を達成することが可能な実装基板の電源制御装置および半導体基板を提供することを目的とする。

【解決手段】集積回路を実装する実装基板の電源制御装置において、半導体基板101に実装されるI/Oパット111、112と、半導体基板に実装されるVcc1系、3系電気回路121、131と、I/Oパット111とVcc1系電気回路121間に接続されるVcc4系アイソレータ部150と、I/Oパット116とVcc3系電気回路131間に接続されるVcc4系アイソレータ部160とを備えている。

(もっと読む)

集積回路装置ドライバを制御するための方法およびシステム、ならびに装置ドライバの出力電圧レベルを調整するための方法およびシステム

【課題】集積回路装置における出力ドライバの駆動強度を制御するためのシステムおよび方法を提供する。

【解決手段】集積回路装置における出力ドライバの駆動強度を制御するためのシステムおよび方法は、代表的な実施例において、不感帯を必要とすることなく単一の基準電圧および単一のコンパレータを用いる。この発明の技術は、出力電圧が常に、単一の基準電圧によって設定される目標レベルの駆動強度から最下位の1ビット以内にあることを保証する。

(もっと読む)

入出力回路および半導体入出力装置

【課題】 消費電力の増大を防止することが可能な入出力回路および半導体入出力装置を提供する。

【解決手段】 トライステート出力回路(入出力回路)1は、イネーブル信号oeに基づいて出力パッドPADoを駆動するP−MOSトランジスタ65と、P−MOSトランジスタ65のゲートに接続されたノードpgの電位を制御するためのP−MOSトランジスタ64と、イネーブル信号oeの信号レベルが遷移した際に所定時間幅のパルス信号oe5および−oe5を出力するワンショットパルス発生回路10と、パルス信号oe5および−oe5が出力されている期間、P−MOSトランジスタ64を制御するためのバイアス電圧Vbiasを生成し、バイアス電圧VbiasをP−MOSトランジスタ64のゲートに印加するバイアス回路30とを有する。

(もっと読む)

半導体集積回路

【課題】 ヒューズ素子のプログラムにかける時間を短縮し、以てシステムLSIの検査コストの増大を抑制する。

【解決手段】 ヒューズ素子31とプログラムトランジスタ32とを直列接続し、フリップフロップ23が起動信号に応答してプログラムトランジスタ32をオンさせることによりヒューズ素子31のプログラムを開始し、ヒューズ素子31とプログラムトランジスタ32との接続点の電圧の変化を通じてヒューズ素子31の抵抗値の変化を2入力NAND回路35にて監視しつつ、ヒューズ素子31の抵抗値が所定の抵抗値まで増加した時点で2入力NAND回路35が終了信号を出力する。フリップフロップ23は、この終了信号に応答してプログラムトランジスタ32をオフさせることによりヒューズ素子31のプログラムを自動的に終了する。これにより、ヒューズ素子31の抵抗値を最小限のプログラム時間で所定値まで増加させる。

(もっと読む)

バッファにおける伝搬遅延及びプロセス及び温度の影響を低減する方法

低速出力エッジを有するバッファ回路が記載されている。パルスのより高値の電流が、ワンショットタイミング回路から駆動されて、出力MOSFETのターンオンか又はターンオフの開始を加速させるために、電流パルスが前記バッファの該出力MOSFETの制御ゲート内へと注入される。前記開始とターンオン及びターンオフとに至る時には、より低値の電流源が、前記出力MOSFETの前記ゲートを駆動するために継続する。一実施形態において、ワンショットは、入力信号の立ち上がりエッジと立ち下がりエッジとからトリガされる。前記より高値の電流パルスの効果は、バッファによる回路遅延を低減することである。更にまた、温度、供給電圧、及びプロセスの変動が起きる時に、実質的に一定となるようバッファ回路の遅延を維持するために、温度に応じるように、及び供給電圧に応じるように、パルス幅を設計することができる。

(もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]