Fターム[5J056CC19]の内容

Fターム[5J056CC19]に分類される特許

1 - 20 / 44

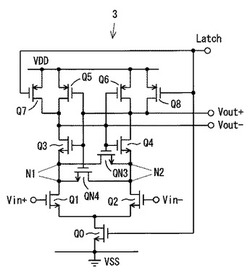

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

差動入力回路および差動入力回路の電圧特性調整方法

【課題】ソースが共通接続されそれぞれのゲートが二つの入力端子に接続さた二つのトランジスタを有する差動対を備える差動入力回路において、より適正に入力オフセットをより小さくする。

【解決手段】トランジスタTin1,トランジスタTin2のドレインに高電圧印加回路60を接続し、トランジスタTin1のソースおよびトランジスタTin2のソースと接地電圧印加点GNDとの間にトランジスタTsenを設け、論理ローレベルの電圧の制御信号SENをスイッチング回路70に入力すると共に制御信号Tcとしてクロック信号を入力して入力端子IN1に電圧V1を印加すると共に入力端子IN2に電圧V2を印加し、検出した出力端子OUT,OUTBの電圧に応じてトランジスタTin1,Tin2のドレインに高電圧印加回路60により電源電圧Vddhを印加する

(もっと読む)

半導体記憶装置

【課題】電源電圧の停止及び復帰を行う構成において、外部回路より半導体記憶装置を制御するための信号数を削減する。

【解決手段】酸化物半導体を半導体層に有するトランジスタを有する記憶回路と、記憶回路に保持されたデータを読み出すための電荷を蓄積する容量素子と、容量素子への電荷の蓄積を制御するための電荷蓄積回路と、データの読み出し状態を制御するデータ検出回路と、電源電圧が供給された直後の期間において、電源電圧の信号と電源電圧を遅延させた信号とにより、電荷蓄積回路による容量素子への電荷の蓄積をさせるための信号を生成するタイミング制御回路と、容量素子の一方の電極の電位を反転して出力するインバータ回路と、を有する構成とする。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr1Cで構成されるインバータ回路1において、トランジスタT2のゲートと高電圧線L3との間に接続されたトランジスタT4,T5と、トランジスタT2のゲートと低電圧線L1との間に接続されたトランジスタT3とのオンオフ動作により、全期間に渡ってトランジスタT1,T2が同時にオンしないようになっている。

(もっと読む)

判定帰還型イコライズ回路

【課題】低電圧動作及び高速動作が可能な、判定帰還型のイコライズ回路を提供すること。

【解決手段】本発明にかかる判定帰還型イコライズ回路は、ダイナミック型サンプル回路1、ラッチ回路2及びバッファ回路3を備える。ダイナミック型サンプル回路1は、入力データIN及びINB、フィードバック信号FB1〜FBn及びFBB1〜FBBnをサンプリングし、サンプリングした信号を加算したサンプル信号SS及びSSBを出力する。ラッチ回路2は、差動サンプル信号サンプル信号SS及びSSBの差電圧を増幅し、増幅した信号を保持する。なお、ラッチ回路2は、差動サンプル信号SS及びSSBが過渡状態にあるときの差電圧を増幅する。バッファ回路3は、ラッチ回路2により保持された信号を出力データOUT及びOUTBとして出力する。

(もっと読む)

ダイナミック回路の初期化方法

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路の初期化方法は、所定の条件でダイナミックノードの初期化を開始するステップと、複数の入力信号の少なくとも一部について論理評価を行うステップと、論理評価の結果が真のとき、ダイナミックノードの初期化を停止するステップとを備えている。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

プログラマブルデバイス回路

【課題】スイッチノードのデータ転送時間を極小として動作を高速化することができるプログラマブルデバイス回路を提供する。

【解決手段】二次元アレイ状に配置されている複数の回路ブロックに個々に接続されている複数のスイッチノード100が相互接続により二次元の可変自在な接続網を形成する。このスイッチノード100が、回路ブロックがデータ出力を実行しているときに並行してプリチャージ動作を実行するプリチャージロジック回路からなる。プリチャージロジック回路はプリチャージ動作に多分に時間を必要とすることでデータ転送時間を短縮できる。そのプリチャージ時間は回路ブロックのデータ出力時間と重複しているのでタイムロスとならない。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

電圧供給回路

【課題】非常に簡略な回路構成で低消費電流化が可能な電圧供給回路を提供する。

【解決手段】値が異なる複数の供給電圧(V1〜V5)を発生させる電圧供給回路であって、論理回路部(インバータIL0−1、IL0−2、IH0−1、及びIH0−2)と、前記論理回路部の一方の出力によって充電動作がオン/オフ制御され、前記論理回路部の他方の出力によって放電動作がオン/オフ制御され、自己の出力電圧が前記供給電圧及び前記論理回路部の入力となる充放電回路部(PチャンネルMOSトランジスタP0及びNチャンネルMOSトランジスタN0)とを備え、前記値が異なる複数の供給電圧の発生において前記論理回路部及び前記充放電回路部を共用している電圧供給回路。

(もっと読む)

集積回路およびこれを有するソースドライバ装置

【課題】データ保存機能(またはラッチ機能)、レベルシフト機能、およびデコード機能が統合されたコンパクトな集積回路を提供し、チップサイズが小さく信頼性テストの時間を減らすことができるソースドライバ装置を提供する。

【解決手段】本発明の集積回路は、保存ノードSNと、第1制御信号CONT1に応答して保存ノードSNをプリチャージするための第1高電圧トランジスタHVT1と、複数の入力信号をデコードして保存ノードSNに伝達するデコード手段320と、第2制御信号CONT2に応答してデコード手段320の出力を保存ノードSNに伝達する第2高電圧トランジスタHVT2と、を含む。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続され、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トランジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジスタのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする。

(もっと読む)

半導体集積回路

【課題】ループフィルタのオンチップ化を可能とし高速応答を実現しロック後に十分な雑音抑圧効果を得るPLL回路を内蔵する半導体集積回路を提供する。

【解決手段】位相周波数比較器1、第1と第2のチャージポンプ2、3、ループフィルタ4、電圧制御発振器5、分周器6を含むPLL回路を内蔵する。PLL回路の動作モードは、ロック動作が停止されたスタンバイ状態と、ロック動作を開始するロック応答動作と、ロック応答動作によって開始されたロック動作を継続する定常ロック動作とを含む。定常ロック動作では、第1のチャージポンプ2の充放電電流よりも、第2のチャージポンプ3の充放電電流が小さく設定され、第1と第2のチャージポンプ2、3は、位相周波数比較器1の出力に応答してループフィルタ4の互いに逆相の充放電動作を実行する。ロック動作を開始するロック応答動作では、逆位相の前記第2のチャージポンプ3による充放電動作が停止される。

(もっと読む)

レベルシフト回路、電気光学装置、およびレベルシフト方法

【課題】レベル変換の信頼性を向上すると共に構成を簡素化する。

【解決手段】ラッチ回路LATの出力ノードN2にはトランジスタTnpが設けられている。このトランジスタTnpは、入力信号IN1の論理レベルが遷移する直前の所定期間においてアクティブとなるプリチャージ信号PRCによってオン状態となり、出力ノードN1をローレベル(VSS2)にプリチャージする。入力ノードN1にはトランジスタTndが設けられている。トランジスタTndは入力信号IN1はローレベルからハイレベルに遷移するとオン状態となり、入力ノードN1の電位をローレベル(VSS2)に設定する。これによって、ラッチ回路LATの記憶内容を確実に更新することができる。

(もっと読む)

駆動回路

【課題】低電圧動作が可能で、高速動作可能なLVDS(Low Voltage Differential Signaling、低電圧差動信号)回路を提供する。

【解決手段】LVDS回路(1)は、LVDS基本回路(1a)と、スイッチ回路(SW1〜SW8)と、バイアス回路(30)とを有する。LVDS基本回路(1a)は、トランジスタ(MP1)、トランジスタ(MN1)、トランジスタ(MP2)、トランジスタ(MN2)とを有する。制御回路(90)によってオン・オフするスイッチ回路(SW1〜SW8)を設けたことにより、トランジスタ(MP1、MN1、MP2、MN2)は電流源として機能する。すなわち、負荷回路(110)を含む経路に実質的にスイッチング素子を含まず、電圧降下が起きず、低電圧動作が可能となる。

(もっと読む)

連想メモリセル、連想メモリセルアレイ、アドレス検索メモリおよびネットワークアドレス検索装置

【課題】検索動作時の低消費電力化を可能にする連想メモリセル、検索動作を低消費電力のもとで実行できる方策を講じて高速化を可能にする連想メモリセルアレイ、それを用いたアドレス検索メモリおよび使い勝手の優れたシステムLSIたるネットワークアドレス検索装置を得ること。

【解決手段】連想メモリセルは、データ入出力を行う2つのビット線BL,ZBLに接続され書き込まれたデータを保持する第1の記憶ノードおよび第2の記憶ノードを有するメモリセルと、2つのMOSトランジスタ103,104からなる一致比較回路と、出力線141に接続され比較の結果不一致のときにプリチャージレベルから電荷引き抜きが行われ降下する出力線151の電位レベルが接地電位レベルに到達する以前の所定電位レベルで止まるようにするクランプ回路151とを備えている。

(もっと読む)

送信回路及びその制御方法

【課題】従来の送信回路は、外部より混入するノイズによって差動信号によって生成されるデータ信号にノイズが発生する問題があった。

【解決手段】本発明にかかる送信回路は、出力端子と電源端子との間に逆流防止素子D1〜D4が接続される第1、第2の駆動回路11、12と、第1、第2の駆動回路11、12の出力を制御する制御回路13とを有する送信回路であって、制御回路13は、第1、第2の駆動回路11、12が第1又は第2の論理レベルを出力する第1の状態から、第1、第2の駆動回路11、12が第1、第2の論理レベルの中間レベルを出力する第2の状態に移行する間に、逆流防止素子D1〜D4を介して前記第1、第2の駆動回路に貫通電流が流れる第3の状態に第1、第2の駆動回路11、12を制御するものである。

(もっと読む)

1 - 20 / 44

[ Back to top ]