Fターム[5J056CC25]の内容

Fターム[5J056CC25]に分類される特許

1 - 20 / 26

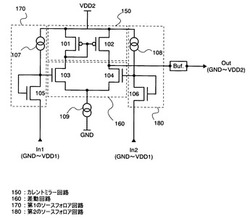

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

集積回路

【課題】単独の動作モード信号で動作モードを切り替えるコンパレータ回路において、コンペアモードでコンパレータ回路の出力値が確定した後も、入力部から出力部に向けて不要な電流が流れてしまう。

【解決手段】本発明の集積回路では、コンパレータ回路に、入力部および出力部の間の、リーク電流が通る電流パスに含まれるトランジスタを制御する論理回路を追加する。この論理回路は、動作モード信号と、コンパレータ回路の出力信号とを入力し、コンパレータ回路の出力信号が確定した後は電流パスを遮断状態にする。

(もっと読む)

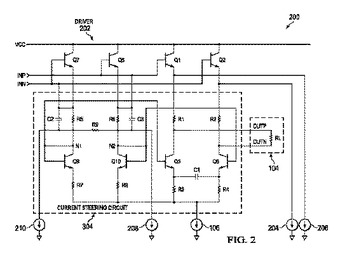

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

インターフェイス回路、LSI、サーバ装置、およびインターフェイス回路のトレーニング方法

【課題】 波形整形のための信号処理機能を有するインターフェイス回路において、波形整形のために付加される回路の影響で、消費電力が大きくなってしまう。また、システム内では複数の基板がバックプレーンに接続されるため、距離が近いものから遠いものまでが混在することになるが、距離に応じて基板を換えるわけではなく、共通の基板を用いるため、インターフェイス回路は最も遠い場合に対応する構成で準備する必要がある。すなわち、最も距離が長いものに対応した波形整形回路を準備し、それらを伝送距離が短い場所でも使用することになり、全体の消費電力が増大するという問題が生じる。

【解決手段】 本発明のインターフェイス回路は、波形整形回路の一部または全ての動作を停止させる。これにより、伝送距離に応じて、インターフェイス回路内の波形整形回路の動作範囲の切りかえを可能とし、波形整形回路の中の動作範囲を制限することができ、インターフェイス回路、インターフェイス回路を含むLSIやサーバ装置の消費電力を低減できる。

(もっと読む)

論理回路および該論理回路を有する表示装置

【課題】デプレション型の単極性のトランジスタでも動作可能な論理回路を提供することを課題とする。

【解決手段】ソースフォロワ回路と、該ソースフォロワ回路の出力部が入力部に接続され、具備するトランジスタのすべてが単極性の論理回路と、を有し、ソースフォロワ回路に接続されている低電位側の配線の電位は、該トランジスタのすべてが単極性の論理回路に接続されている低電位側の配線よりも低くして論理回路を構成する。このようにすることで、デプレション型の単極性のトランジスタでも動作可能な論理回路を提供することができる。

(もっと読む)

検出回路

【課題】プロセスミスマッチ等によるサンプルごとの検出電圧レベルのばらつきを低減させることができ、高速動作を行うことが可能な検出回路を提供する。

【解決手段】1対のシリアルデータ信号の一方が反転入力端に入力され、他方が非反転入力端に入力される第1検出用レシーバ回路と、1対のシリアルデータ信号の一方が非反転入力端に入力され、他方が反転入力端に入力される第2検出用レシーバ回路と、第1検出用レシーバ回路及び第2検出用レシーバ回路の各出力信号に基づいて、入力検出及び切断検出の少なくとも一方を行う検出回路とを備え、第1検出用レシーバ回路及び第2検出用レシーバ回路は、それぞれ第1差動入力回路及び第1負荷回路を含む差動増幅回路と、差動増幅回路の閾値に設ける第1オフセット制御回路とを有し、第1負荷回路はドレインが独立でゲートを共通とし、ゲートに所定の電圧が印加される1対のMOSトランジスタを含んで構成される。

(もっと読む)

入力インタフェース回路

【課題】 外部機器の出力タイプに合わせてシンク型とソース型とに容易に切換えることができ、且つ製作コストを低減できる入力インタフェース回路を提供すること。

【解決手段】 入力インタフェース回路は、外部機器50に接続された端子A,Bと、ディップSW8,9と、端子Aに接続されたFET30を含むVCCバイパス回路22と端子Bに接続されたFET40を含むGNDバイパス回路23と、VCCバイパス回路22のFET30とGNDバイパス回路23のFET40を駆動する為のFET駆動回路21と、ディップSW8,9の設定信号に基づいてFET駆動回路21を制御する制御部3と、NPN入力対応モードのとき端子Aからの入力信号レベルを低く変換して制御部3へ出力するシンク用レベル変換回路24と、PNP入力対応モードのとき端子Bからの入力信号レベルを低く変換して制御部3へ出力するソース用レベル変換回路25とを設けた。

(もっと読む)

出力回路

【課題】複雑な遅延回路を用いずにプリエンファシスの信号を生成し、また、プリエンファシスの強度を変化させても、出力のコモンモードレベルが変化しない出力回路を提供する。

【解決手段】信号入力に比例した出力電流を生成する相互コンダクタンス回路と、前記信号入力からプリエンファシス電流を生成するプリエンファシス電流出力回路と、プリエンファシス電流出力回路の出力のAC電流成分を、調整電圧入力に基づく所定の係数で増幅するプリエンファシス電流調整回路と、前記相互コンダクタンス回路の出力電流と前記プリエンファシス電流調整回路の出力電流とが流れ、出力を生成する負荷回路とを備える。

(もっと読む)

半導体装置

【課題】増幅回路の利得を補償するためにGm補償バイアス電圧を与えても、増幅回路の出力電流電圧の変動が少なく、出力信号の歪み特性が良好な半導体装置を提供する。

【解決手段】半導体装置において、利得制御回路と、前記利得制御回路により利得が一定に制御された第1の回路と、前記第1の回路に対するバイアス回路とを備え、前記第1の回路は、第1のトランジスタと負荷抵抗とを有し、前記第1の回路の増幅率又は減衰率は前記第1のトランジスタの相互コンダクタンスと前記負荷抵抗の抵抗値との積に比例し、前記負荷抵抗に印加される電圧を前記半導体装置の出力とし、前記バイアス回路は、前記第1のトランジスタに流れるドレイン電流に比例した電流と前記負荷抵抗値に反比例した電流との差分電流を生成して出力し、前記バイアス回路の出力は前記第1の回路の出力ノードに接続される。

(もっと読む)

差動制御回路

【課題】差動回路の入力トランジスタのホットキャリア劣化を遅らすことができる差動制御回路を提供する。

【解決手段】動作モード設定回路をなすアップダウンカウンタ24は、最上位ビット出力信号S0を動作モード設定信号として出力する。第1の分配回路28は、最上位ビット出力信号S0がHレベルとされる第1の動作モード時には、入力信号SINを第1の入力トランジスタ19のゲートに与えると共に、基準電圧VREFを第2の入力トランジスタ20のゲートに与え、最上位ビット出力信号S0がLレベルとされる第2の動作モード時には、入力信号SINを第2の入力トランジスタ20のゲートに与えると共に、基準電圧VREFを第1の入力トランジスタ19のゲートに与える。

(もっと読む)

バッファ回路

【課題】低電圧から動作し、回路電流の変化が少なく、低周波から信号を通せ、半導体集積回路上に形成して好適とされるバッファ回路を提供する。

【解決手段】電流駆動されたMOSトランジスタM1のゲートには入力電圧が印加され、ソースから出力電圧を出力するソースフォロワ回路において、バックゲート電圧が印加され、バックゲート電圧を制御することで前記ソース電圧が所望の値になるようにする。OPアンプA1の正相入力端子に、ゲートにバイアス電圧が印加されたMOSトランジスタM2のソースが接続され、OPアンプA1の出力電圧が前記バックゲート電圧として供給される。

(もっと読む)

高速シリアルデータ信号送信器ドライバ回路網

【課題】高速シリアルデジタルデータ信号送信器ドライバ回路網を提供すること。

【解決手段】約10Gbpsの範囲のシリアルビットレートを有する高速シリアルデータ信号を出力するための送信器ドライバ回路網であって、メインドライバステージとポストタップドライバステージとだけを有するHツリードライバ回路網を備えている、回路網であって、該Hツリードライバ回路網の一部分を形成する少なくとも1つのトランジスタが、さらに、該回路網に対する静電放電保護を提供する、回路網。

(もっと読む)

低電圧アプリケーションのためのマルチモード出力構成を有する自己バイアス装置差動信号回路のための装置および方法

差動シグナリング回路網、電流源コントローラおよびトランジスタ実装電流源の対を有するディジタルデータ送信装置が開示される。前記電流源コントローラは、前記差動シグナリング回路網の検出された動作モードに基づいて電流源制御信号を生成する。前記トランジスタ実装電流源の対は、前記電流源制御信号に応答して、前記差動出力端子における前記出力電圧レベルを調整するために、供給源電流を選択的に生成する。また、前記ディジタルデータ送信装置は、電流源バルクバイアス信号を生成する電流源バルクバイアス回路も有し、前記電流源バルクバイアス信号は、前記差動シグナリング回路網がある動作モードで動作時に、前記トランジスタ実装電流源の対間の電流リークを遅延させる。  (もっと読む)

(もっと読む)

低オフセット入力回路

【課題】 入力回路の回路特性ばらつきが信号受信動作に与える影響が無視できないような信号伝送システムにおいて、半導体集積回路の端子数が増加せず、半導体集積回路の外部に新たな信号観測手段、ばらつき調整量計算手段を付加する必要がなく、高速動作が可能で、常時信号受信動作を続けることができる低オフセット入力回路の実現方法を提供する。

【解決手段】 入力回路40と、オートゼロアンプ42と、アナログディジタル変換回路43と、符号化回路44と、信号保持回路45とからなる信号受信回路において、入力回路40の出力誤差信号をオートゼロアンプ42で増幅し、その信号をディジタル化および、必要に応じて符号化した信号を保持回路45で保持し、その保持された信号で入力回路40の回路特性ばらつきを調整する。

(もっと読む)

ソースフォロワ回路

【課題】MOSトランジスタの温度特性に起因する出力電圧の変動を低減することが可能なソースフォロワ回路を低コストに提供する。

【解決手段】第1実施形態のソースフォロワ回路10は、各トランジスタMN2,MP4を組み合わせて両者の温度特性を相補させたカレントミラー回路である出力回路12の前段に、出力回路12の温度特性を補正するための温度特性補正回路11が接続されている。そして、温度特性補正回路11を構成する各抵抗R1,R2の抵抗比を0.5に設定することにより、ソースフォロワ回路10の出力電圧VOUTの温度特性を平坦化させ、温度特性に起因する出力電圧VOUTの変動を無くすことができる。また、温度特性補正回路11は簡単な構成であるため低コストに実現できる。

(もっと読む)

出力ドライバ回路および方法

【課題】

従来のカレントモード出力ドライバ回路と比べてより消費電力の少ない、プリエンファシス機能を有する出力ドライバ回路を提供する。

【解決手段】

本発明に係る出力ドライバ回路は、第1のデータ信号を受信し、第1のデータ信号に基づいて第2のデータ信号を出力する複数の、電流減算を実施する第1の差動対をもつ、プリドライバ段と、電気的にプリドライバ段と接続され、プリドライバ段からの第2のデータ信号を受信する、伝送ラインに出力信号を伝送する第2の差動対をもつ、出力ドライバ段とを備えている。

(もっと読む)

バッファ回路、終端検出装置及び終端検出方法

【課題】信号の出力の有無に関わらず、終端されているかどうかを正しく検出するバッファ回路、そのようなバッファ回路を備えた終端検出装置、及び終端検出方法を提供する。

【解決手段】バッファ回路(130)は、出力端子(13)を備えて、前記出力端子から0Vより大きな信号を出力する出力回路(10)と、出力端子から流れ出る電流に基づいて、出力端子が終端されているか否かを判別する判別器(20)と、を有する。

(もっと読む)

1 - 20 / 26

[ Back to top ]