Fターム[5J056DD23]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | nPnトランジスタのみ (31)

Fターム[5J056DD23]に分類される特許

1 - 20 / 31

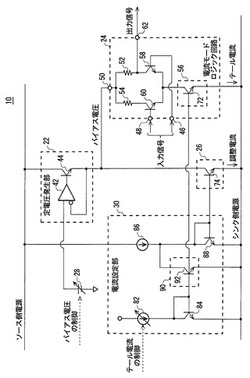

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

信号出力回路

【課題】トランジスタ製造工程をnpn型の製造工程のみとして、使用可能な化合物半導体の自由度を高め、単相のデジタル信号により外部から出力透過/遮断を切替制御する。

【解決手段】トランジスタとしてnpn型を用いて構成し、入力バッファ11で、外部入力された単相切替指示信号10Sを、互いの位相が反転している差動切替指示信号11Sに変換し、発生制御回路13で、差動切替指示信号11Sに基づいて、制御電圧発生回路14における制御電圧VCSの発生を制御するための発生制御信号13Sを出力し、制御電圧発生回路14で、発生制御信号13Sに基づいて、単相切替指示信号10Sの論理に応じて電圧値が変化する制御電圧VCSを発生させて出力し、出力回路15で、入力された差動入力信号INをインピーダンス変換し差動出力信号OUTとして出力し、制御電圧VCSに基づいて当該差動入力信号INの出力透過/遮断を切り替える。

(もっと読む)

半導体集積回路

【課題】コンデンサの供給する電源電圧の低下により、誤動作を起こす虞がある。

【解決手段】通常動作より低い消費電力状態である低消費電力モードを有する半導体集積回路であって、前記低消費電力モード状態時に、電源電圧レベルを検出する検出手段と、前記検出した電源電圧レベルを記憶する記憶手段と、前記通常動作時よりも小さい電流を流すことで、前記電源電圧を低下させる擬似負荷手段と、前記擬似負荷手段により電流を流す前に前記記憶手段で記憶した第1の電圧レベルに応じて前記検出手段の検出レベルを第2の電圧レベルに切り換える切換え手段と、前記擬似負荷手段により電流を流すことにより低下した前記電源電圧が、前記第2の電圧レベルとなるかを判定し、前記低消費電力モードを解除するか否かの制御を行う制御手段と、を有する半導体集積回路。

(もっと読む)

半導体出力回路

【課題】入力信号に対して出力信号が高速に応答し、かつ、半導体出力回路の消費電力を低減させることが可能である半導体出力回路を提供する。

【解決手段】本発明の半導体出力回路は、ベースが定電流源に接続され、コレクタが第2のnpnトランジスタのエミッタに接続され、エミッタが第1のnpnトランジスタのコレクタに接続される第3のnpnトランジスタを含む。

(もっと読む)

クロック入力インターフェース回路

【課題】低消費電力なクロック入力インターフェース回路を提供する。

【解決手段】クロック入力インターフェース回路1は、インピーダンス整合・出力電圧調整抵抗R11,R13と、出力電圧調整抵抗R12,R14と、電流安定化抵抗R15,R16と、反射防止終端抵抗R17と、DCレベル阻止容量C1,C2と、RFバイパス容量C3,C4と、電流源トランジスタQ1,Q2とから成る。クロック入力端子CKにクロック信号を入力する伝送線路とインピーダンス整合し、かつ次段の回路の入力端子で必要とされるDCバイアス電圧を出力端子OT,OCに与えることができるように、抵抗R11〜R14,R17の値および容量C1〜C4の値が設定される。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

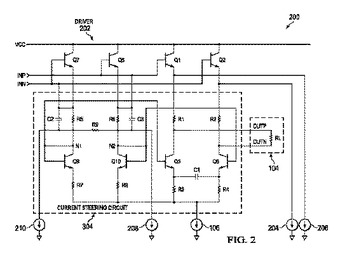

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

リンギング抑制回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できるリンギング抑制回路を提供する。

【解決手段】電源と信号線12Pとの間に接続されるNチャネルMOSFET19と、信号線12Mとグランドとの間に接続されるPチャネルMOSFET20とを備え、リンギング抑制回路18は、信号線12P,12Mの電位と、それぞれに対応するNチャネルMOSFET19,PチャネルMOSFET20のゲートに付与される電位との差に応じてNチャネルMOSFET19及びPチャネルMOSFET20をオンさせて、信号線12P,12Mに発生しようとするリンギングの抑制を図る。

(もっと読む)

比較回路

【課題】比較回路の自己発熱を抑制して、自己発熱対策に起因する当該比較回路の動作速

度の低下を防止できるようにする。

【解決手段】差動増幅部11,12にスイッチS1,S2をそれぞれ接続させる。スイッ

チS1をONにして差動増幅部11を動作させるときには、スイッチS2をOFFにして

差動増幅部12を停止させ、スイッチS2をONにして差動増幅部12を動作させるとき

には、スイッチS1をOFFにして差動増幅部11を停止させる。この結果、スイッチS

1,S2によって差動増幅部11,12が交互に動作するので、差動増幅部11,12の

動作による自己発熱を抑制することができ、自己発熱対策に起因する比較回路1の動作速

度の低下を防止できる。

(もっと読む)

半導体集積回路

【課題】電源線のレイアウト面積を広げることなく、コア回路とバイアス供給回路との間

の電圧降下を抑え、かつ、コア回路間の高速信号ノードを短縮できるようにする。

【解決手段】Si基板11にトランジスタQ及び抵抗素子Rを有して高電位側の電源線と

低電位側の配線D1とバイアス供給用の配線D2とに接続されてトランジスタ動作をする

コア回路1と、Si基板11に設けられてコア回路1にバイアスを供給するバイアス供給

回路とを備え、コア回路1の中の定電流源用のトランジスタQに、その一端が接続された

抵抗素子Rの他端がバイアス供給用の配線D2に接続され、この配線D2が接続された抵

抗素子Rの他端がコンタクトホール35を介してバイアス供給用の配線D2よりも上層の

低電位側の配線D1に接続されるものである。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

ドライバ・コンパレータ回路およびそれを用いた試験装置

【課題】双方向伝送において送信信号をキャンセルする。

【解決手段】第1抵抗R1は、その第1端子に第1電圧VH’が印加され、その第2端子が入出力端子P1と接続される。第2抵抗R2は、その第1端子に第1電圧VH’が印加される。テイル電流源12は、所定のテイル電流Ia’を生成する。電流スイッチ10は、第2デバイス102に送信すべきデータPATを受け、その値に応じて第1抵抗R1の第2端子と第2抵抗R2の第2端子の一方を選択し、テイル電流源12と結合する。分圧回路DIV1は、第1抵抗R1の第2端子と第2抵抗R2の第2端子の間に順に直列に設けられた第3抵抗R3および第4抵抗R4を含む。負荷バランサLB1は、その第1端子に第2電圧VLBが印加され、その第2端子が第2抵抗R2の第2端子と接続された第5抵抗R5を含む。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

出力回路

【課題】消費電流を削減した出力回路を提供する。

【解決手段】入力端子にベースが接続されコレクタが第1の電源端子に接続されエミッタが出力端子に接続された第1のトランジスタと、コレクタが前記出力端子に接続されエミッタが第2の電源端子に接続された第2のトランジスタと、該第2のトランジスタとともに第1のカレントミラー回路を構成する第3のトランジスタと、該第1のカレントミラー回路に電流を供給する第1の電流源とを備える出力回路において、前記第1の電流源を前記入力端子に入力する入力電圧を電流に変換し、前記入力電圧の変化に逆比例して変化する電流を出力する電圧/電流変換回路で構成する。

(もっと読む)

入力判定装置

【課題】二種類のスイッチを混在して使用する場合において、容易な構成でプリント基板の共通化を図ることができる入力判定装置を提供する。

【解決手段】単一のプリント基板10に、判定部40を有する同一構成の入力回路30が複数形成されている。プリント基板10の外部にはグランド接地型のスイッチSW1と電位接続型のスイッチSW2,SW3が配置され、スイッチSW1は入力回路30のスイッチ接続端子53に接続されているとともに当該入力回路30の電位設定端子52が外部ケーブル60により電源端子11に接続されている。スイッチSW2,SW3は他の入力回路30のスイッチ接続端子53に接続されている。

(もっと読む)

出力回路

【課題】出力振幅の変更が容易な出力回路を提供する。

【解決手段】出力回路は、入力端子INに入力信号が入力され、コレクタ端子が直列に接続された抵抗R1および抵抗R2を介して電源端子に接続されるトランジスタQ2を含む増幅器1と、ベース端子がトランジスタQ2のコレクタ端子に接続され、コレクタ端子が抵抗R1と抵抗R2の接続点に接続され、エミッタ端子が出力端子OUTに接続される第2のトランジスタを含む増幅器2と、を備え、出力端子OUTに接続される可変抵抗R3の抵抗値の変化に応じて出力信号の振幅が変化する。

(もっと読む)

プリエンファシス回路

【課題】 簡単な構成でプリエンファシス信号を生成することが可能なプリエンファシス回路を実現する。

【解決手段】 信号の変化点で振幅を大きくするプリエンファシス回路において、差動入力信号を差動電流出力に変換する第1のトランスコンダクタンスアンプと、ハイパスフィルタ回路と、このハイパスフィルタ回路を介した前記差動入力信号を差動電流出力に変換する第2のトランスコンダクタンスアンプと、2つの前記差動電流出力をそれぞれ加算して電圧変換する第1及び第2の抵抗とを設ける。

(もっと読む)

信号ドライバおよびそれを用いた半導体試験装置

【課題】半導体試験装置では、測定カードを選択して用いることにより顧客の多様なニーズに対応しているが、仕様によっては測定カードが挿入されないスロットが発生し、このスロットに接続されている伝送路がノイズ発生源となって他の伝送路を流れる信号に悪影響を与えてしまうという課題を解決する。また、ドライバ、伝送路の不具合の原因を特定することができないという課題を解決する。

【解決手段】LV−PECLドライバのように、入力デジタル信号によってオン、オフが制御され、エミッタから出力を取り出す出力トランジスタを有する信号ドライバの出力端子を、抵抗を用いてプルアップするようにした。また、信号ドライバの出力電圧を監視する電圧検出部を設けた。

(もっと読む)

インターフェース回路

【課題】入力部3の入力信号S1を制御部2に入力するものにあって、入力部3と制御部2との間に接続された抵抗素子R3の発熱を防止することで、抵抗素子R3の耐久性を向上させる。

【解決手段】制御部2に接続された入力部3の入力信号S1を入力インターフェース部4を介して制御部2に入力するようにした入力インターフェース回路1において、入力部3と制御部2との間に接続された抵抗素子R1の発熱を防止すべく、入力部3からの入力信号S1を間欠的に制御部2に入力させる間欠入力手段5が設けられている。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

1 - 20 / 31

[ Back to top ]