Fターム[5J064BC04]の内容

圧縮、伸長、符号変換及びデコーダ (21,671) | 細部(回路)構成 (8,519) | レジスタ (179)

Fターム[5J064BC04]に分類される特許

1 - 20 / 179

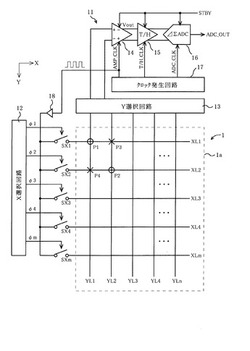

静電容量検出回路

【課題】静電容量検出回路において、デルタシグマ型AD変換器の精度(量子化ノイズ)を劣化させることなく、データ更新レートを短縮する。

【解決手段】デルタシグマ型AD変換器16から出力されるNビットのデジタルデータAD_OUTのデータ更新レートを短縮するために、デルタシグマ型AD変換器16のサンプリング・クロックADC_CLKの周波数は、電荷増幅器14のアンプ・クロックAMP_CLKの周波数より高く設定される。また、トラックホールド回路15を電荷増幅器14とデルタシグマ型AD変換器16の間に挿入することにより、電荷増幅器14の電荷転送モードにおける出力電圧AMP_OUTだけを周期的に取り込んで保持するようにしている。

(もっと読む)

予測符号化方法及び予測符号化装置

【課題】縞模様のような一定パターンの複数の画素からなる画像データがパケットをまたぐような期間続いた場合でも、復号値が縞模様を表す一定パターンとなるような符号化を行う。

【解決手段】予測符号化回路100は、減算器101にパケットの先頭を示す画素データが入力され、かつ、一致検出部110からの一致検出信号が論理値「0」であるときは、先頭データをセレクタ116及び117を通して量子化することなくそのまま外部へ出力する。ここで、縞模様のような一定パターンの複数の画素からなる画像データがパケットをまたぐような期間続いた場合、一致検出部110は論理値「1」の検出信号を出力してレジスタ116を端子1の入力を選択するように切り替え、レジスタ108に保持されている直前のパケットの復号値をレジスタ116及び117を通して外部へ出力する。

(もっと読む)

情報処理装置および情報処理方法

【課題】情報処理に必要なビット操作が多様化し、必要な処理も複雑化している。

【解決手段】情報処理装置10は入力レジスタ12に格納されたデータをビットごとに操作し、その結果を出力レジスタ14に格納する。セレクタ回路18は、入力レジスタ12からの128ビットの入力データから1ビットの出力データを選択する。アンド回路20は、対応するセレクタ回路18からのデータが有効な場合にのみ、当該データを出力レジスタ14の対応するビットに出力する。制御信号生成器16は各セレクタ回路18に、選択すべきビットの番号を示すセレクト信号を入力するとともに、各アンド回路20に、セレクタ回路18から入力されたデータが有効か無効かを示す信号を入力する。

(もっと読む)

データ変換方法、変換装置および画像符号化装置

【課題】 アダマール変換係数のDC係数と3つのAC係数を各々2段の演算で計算して、それら4つの係数を同じタイミングで計算することができ、全体として高速な変換技術を提供する。

【解決手段】 加減算部106は、入力端子101乃至104から入力した変換対象の4つの整数データのそれぞれを加減算し、中間データを生成する。減算部111は入力端子101に入力したデータから中間データを減算してDC係数データを生成し、出力端子112より出力する。加算部112乃至114は、減算部111と同じタイミングで、入力端子102乃至104に入力したそれぞれのデータに中間データを加算してAC係数データを生成し、出力端子122乃至124から出力する。

(もっと読む)

1ビットオーディオ信号用イコライズ装置

【課題】1ビットオーディオ信号に対するイコライジングを高品質なままリアルタイムに実行可能な装置を提供すること。

【解決手段】イコライジング機能を有するフィルタ処理部200を構成する4個のバイクワッドフィルタ210、230、250、270におけるフィルタ間に、並列処理可能にするタイミング合わせのための遅延器290、291、292を設けた構成としたので、各バイクワッドフィルタ210、230、250、270のフィルタリング演算を並列処理することができる。この結果、1ビットオーディオ信号に対するイコライジングを音質を劣化させずリアルタイムに実現可能となる。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理方法を提供する。

【解決手段】RISCによるマシン語のプログラムデータは、データ長が32ビットの固定フォーマットで決められた所定領域に対して、同じ意味のコードが格納されるため、LZ77符号による符号化を行う際のスライドが4バイト毎に一致する可能性が高くなる。そこで、バイト単位でプログラムデータの4バイト毎に小さい値の変換アドレス値TAddressを割り当てる変換テーブルを用いて、アドレス値Addressを変換する。そして、値が「0」〜「15」までの変換アドレス値TAddressを、符号長が4ビットの符号に符号化し、値が「15」〜「255」の変換アドレス値TAddressを符号長が8ビットの符号に符号化する。

(もっと読む)

AD変換装置、AD変換装置を用いた電流検出器及び電流検出器を用いたディジタルサーボ制御装置

【課題】予定外に連続して割り込みが発生した場合に、後に発生した不要な割込みをマスクして正常に割込みを行い、AD変換データを読み込むことができる回路構成とし、より信頼性の高いAD変換装置、電流検出器およびディジタルサーボ制御装置を提供する。

【解決手段】割込み信号セレクタ19の後段にカウンタ24によるマスク信号25とOR素子26で構成された割込み信号マスク回路27を備え、割込み信号発生後の一定時間、割込み信号をマスクする。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で信号の歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】シフトレジスタSREG、1ビットディジタルΔΣ信号を入力し、一対の信号を出力するスイッチ回路SW1〜SW(N)、出力された一対の信号を入力して一対の信号として出力するインピーダンス素子IMP1〜IMP(N)、出力された一対の信号の一方を入力する反転入力端子OPAa、他方を入力する非反転入力端子OPAb、1ビットディジタルΔΣ信号をディジタルアナログ変換した信号を出力する出力端子102を備える演算増幅器OPA、反転入力端子OPAaと出力端子102とに接続されるインピーダンス素子IMP0−N、非反転入力端子OPAbに一端が接続され、他端に基準電圧が与えられるインピーダンス素子IMP0−Pによりディジタルアナログ変換器を構成する。

(もっと読む)

情報処理装置、情報処理方法、プログラム及び記憶媒体

【課題】2種類以上の固定長符号で構成される符号化画像データを、効率的に可変長符号化する。

【解決手段】固定長符号のそれぞれを、入力符号として取得する。入力符号の固定長符号化方法を判定する。入力符号を可変長符号に変換する。何れかが生成した可変長符号を、入力符号を可変長符号化した結果として出力する。対応する固定長符号化方法が予め設定されており、入力符号が対応する固定長符号化方法によって符号化されている場合に、対応する固定長符号化方法によって生成された固定長符号を可変長化する方法として予め設定された可変長符号化方法を用いて、入力符号を可変長符号に変換する。

(もっと読む)

符号化装置、復号化装置、符号化方法、及び、復号化方法

【課題】従来、符号化装置内に復号装置を備えなければならない。

【解決手段】符号化装置は、メモリ101と、メモリ101に蓄積された複数のディジタル信号データをビット単位に比較し、ディジタル信号データの最上位ビットから最初に異なると判定したビットまでの位置情報を求める位置選定器104と、符号化に最適な符号語長となるrビットを選択する符号語長選定器105と、位置情報及び符号語長に基づいて、メモリ101に蓄積された複数のディジタル信号データからrビットを抽出して符号語列として出力する符号化器102と、位置情報、符号語長及び符号語列を所定規則に則ってフォーマット化し、ビットストリームとして出力するフォーマット器103と、出力されたビットストリームの符号長から次の連続した映像のディジタル信号データの符号化に使用する符号語長を算出する制御器106とを有する。

(もっと読む)

オーバサンプリングデータ変換用のトライレベル論理データシャッフリングのためのシステムおよび方法

【課題】素子不整合を低減する改良型シグマデルタノイズ整形DACを提供する。

【解決手段】符号付きバイナリデータを受け取り、符号付き指標データを供給する指標エンコーダを持ち、符号付き指標データは、正指標データおよび負指標データを含む。正指標データに応答して正入力データを受け取り、負指標データに応答して負入力データを受け取るシャッフラを持ち、デコーダはシャッフラ40から出力データを受け取り、復号化データをアナログ出力ステージに供給する。

(もっと読む)

符号化方法、プログラム

【課題】容易に既存の符号化方式と組み合わせることができ、かつ、送信側だけに機能を

追加するだけで、効果的に量子化ノイズの耳障り感を低減することが可能な符号化装置を

実現する。

【解決手段】第nサンプル目のディジタル音響信号サンプルxnとフィードバック信号サンプルとを加算して加算結果を得るステップと、入力された信号をサンプル毎に符号化する所定の符号化方式により加算結果から符号化信号を生成するステップと、符号化信号から上記符号化方式に対応する復号化方式により復号化信号サンプルを生成するステップと、復号化信号サンプルからディジタル音響信号サンプルを減算して減算結果を得るステップと、減算結果を1サンプリング時間遅延させてフィードバック信号サンプルを得る遅延ステップと、をディジタル音響信号サンプルxnの入力がxn+1、xn+2、・・・と継続する間、繰り返し実行する。

(もっと読む)

データ復号化装置およびデータ復号化方法

【課題】 圧縮処理されたデータの復号化を単純な回路構成と簡易な制御により実現するデータ復号化装置およびデータ復号化方法を提供する。

【解決手段】 符号化データを受信するデータ受信部と、テーブル中の符号について下位側にビット値0が付加されて所定ビット長となった第1付加符号の値と、下位側にビット値1が付加されて所定ビット長となった第2付加符号の値とのそれぞれと大小比較する比較部と、比較部による比較の結果、データの値が、第1付加符号の値以上かつ第2付加符号の値以下であった場合に、それら第1付加符号および第2付加符号の元となった符号に対応テーブルで対応付けられているデータ値を復号化データとして出力する出力部を備えた。

(もっと読む)

線形性改善回路、ΣΔA/D変換器、および受信装置

【課題】バイナリコードで演算する加算器が不要で、高速、低消費電力で動作することが可能な線形性改善回路、ΣΔA/D変換器、および受信装置を提供する。

【解決手段】線形性改善回路10は、nビットのA/D変換器の前回の出力コードに応じた第1シフト量を生成する第1シフト量生成部12と、入力コードデータを、供給される第1シフト量をもってビットシフトして出力する第1シフタ回路13と、第1シフタ回路の出力を格納し、格納データを第1シフタ回路の入力コードデータとして出力して第1シフタ回路とループ回路を形成し、かつ、格納コードデータを第2シフト量として出力するレジスタと、A/D変換器の出力コードを供給される第2シフト量をもってビットシフトしてnビットのD/A変換器に出力する第2シフタ回路16と、を有する。

(もっと読む)

復号装置

【課題】予測符号化と可変長符号化とを併用した圧縮符号化アルゴリズムにより圧縮符号化された画像データをデコードする際のデコード性能を向上させる。

【解決手段】水平方向に並んだ2つの処理対象画素の各々についての予測誤差がゼロである場合に、各処理対象画素の真上に位置する画素の画素値、左側の処理対象画素の左上および左隣に位置する各画素の画素値から当該右側の処理対象画素の画素値を算出する。一方、上記2つの処理対象画素のうちの左側のものの画素値については、同右側の処理対象画素の画素値の算出過程で必然的に求まる。

(もっと読む)

データが記憶された位置を選択する装置及び方法

【課題】データが記憶された複数の位置からそのデータが最近に書き込まれた位置を選択できる可能性を高める。

【解決手段】連想メモリセルアレイ26内の特定の文字データが記憶された複数のアドレスを表す信号MATCHが入力されると、ラッチ90、AND回路92、OR回路94によって、複数のアドレスの少なくとも一部がローアドレス領域内にあるかどうかが判定され、ラッチ90、NOT回路96、NAND回路98、AND回路100によって、複数のアドレスの少なくとも一部がローアドレス領域内にある場合にハイアドレス領域からの信号MATCHがマスクされ、プライオリティエンコーダ102が、マスクされずに入力された信号MATCHが表すアドレスのうちの最大のアドレスを、複数のアドレスのうちの選択すべきアドレスとして出力する。

(もっと読む)

ビット長を符号に変換する回路及び方法

【課題】複数の文字列の各々に割り当てられた複数のビット長を複数の符号に変換する際の処理時間を短縮する。

【解決手段】ハフマンテーブル復号回路において、文字に割り当てられたビット長の入力に応じて、各文字に割り当てられたビット長をbl[N]に格納し、同じビット長が割り当てられた文字列の中での各文字列の順番をcode_fin[N]に格納する。また、同じビット長が割り当てられた文字の数をbl_count[M]に格納し、これに基づき、同じビット長を有する最小符号をcode_min[M]に格納する。これにより、セレクタ31が、code_min[M]に格納された複数の最小基準のうちbl[N]で指定された最小符号を取り出し、加算回路32が、これをcode_fin[N]に格納された値に加算する処理を並列に行い、その結果を文字に割り当てられた符号とする。

(もっと読む)

データ圧縮装置、データ伸張装置、およびそれらを搭載した表示装置

【課題】品質の低下を抑制しながら、簡素な処理でデジタルデータを圧縮または伸張する。

【解決手段】共通ビット数検出部120は、デジタルデータを構成する複数のデジタル値を、最上位ビットからビット単位で比較していくことにより、複数のデジタル値間でビット値が共通する、最上位ビットからのビット数を共通ビット数として検出する。圧縮部130は、デジタル値の最上位ビットから、共通ビット数検出部120により検出された共通ビット数分のビットデータを破棄し、かつ当該デジタル値の最下位ビットから、予め設定された全体破棄ビット数から共通ビット数を減算した下位側破棄ビット数分のビットデータを破棄する。

(もっと読む)

エンコード装置

【課題】マーカと区別する判別データの削除および挿入を処理性能の低下を伴わずに処理するデコード装置およびエンコード装置を提供する。

【解決手段】本発明のデコード装置は、符号化データを保持するメモリと、前記符号化データを比較する比較器と前記符号化データからデータを削除する削除部を持つ第1のデコード回路と、前記第1のデコード回路の出力データを復号化する第2のデコード回路と、復号化されたデータを保持するメモリを備える。

(もっと読む)

データストリームを処理する装置

【課題】高解像度テレビジョンシステムにおいて符号化データを伝送するのに用いられる、トランスポート・データパケットを組み立てる方法および装置を提供する。

【解決手段】不完全なデータ・パケットは空白(ゼロにされたビット)ワードで満たされて、規定された数のワードを備えた完全なデータ・パケットを構成する。完全パケットを使用することによって、可変長コードワード・システム等における任意のデータ状態においてもデータのサーチおよび同期化が可能になる。

(もっと読む)

1 - 20 / 179

[ Back to top ]