Fターム[5J067HA25]の内容

Fターム[5J067HA25]の下位に属するFターム

可変抵抗 (14)

Tr又はダイオードで構成された抵抗 (1)

負性抵抗 (4)

Fターム[5J067HA25]に分類される特許

1 - 20 / 195

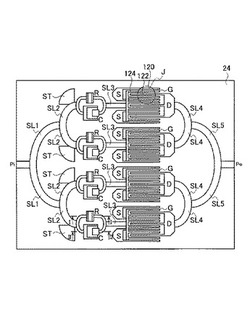

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

リミッター回路

【課題】接続される低雑音増幅器の破壊を防止すると共に、この増幅器の飽和の範囲を狭くし正常動作の範囲を広くすることが可能なリミッター回路を提供すること。

【解決手段】一例のリミッター回路は、高周波入力端子に接続され、一定の飽和入力電力範囲を有する低雑音増幅器の入力端子と接地との間に接続されたPINダイオードと、前記低雑音増幅器の入力端子に一端を接続され他端は接地される、所定周波数の1/4波長の長さの伝送線路と、前記低雑音増幅器の入力端子に前記飽和入力電力範囲に入る信号が入力されるときに、前記伝送線路の他端と接地との間に、直列接続される電力設定用抵抗器及び定電圧電源を接続し、前記低雑音増幅器の入力端子に入る信号を、この範囲より電力の小さい正常入力電力範囲の信号に下げて前記低雑音増幅器の入力端子に入力する手段と、を有する。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

電子回路

【課題】、高出力動作が可能なカレントリユース電子回路を提供すること。

【解決手段】第1端子、第2端子および制御端子を有し、前記第1端子が接地された第1トランジスタT1と、第1端子、第2端子および制御端子を有し、前記制御端子に前記第1トランジスタの第2端子が接続され、前記第1端子が前記第1トランジスタの前記第2端子と高周波的に接続され、前記第2端子に直流電源が接続される第2トランジスタT2と、前記第1トランジスタの第2端子と前記第2トランジスタの制御端子との間のノードに一端が接続され、他端が前記第2トランジスタの第1端子に接続された第1抵抗R1と、を具備した電子回路。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

高調波抑圧回路

【課題】高周波動作と、低コスト化および小型化とを両立させることが可能な高調波抑圧回路を得ること。

【解決手段】基本波の1/8波長の長さを有し、一端が入力端16aを形成し、他端が出力端16bを形成する主線路10と、一端が主線路10の入力端16aに接続された基本波の1/4波長の長さを有する第1の線路11aと、第1の線路11aの他端に一端が接続された抵抗体14および基本波の1/4波長の長さを有する第1のオープンスタブ12aと、抵抗体14の他端に接続された基本波の1/8波長の長さを有する第2のオープンスタブ13aと、一端が主線路10の出力端16bに接続された基本波の1/4波長の長さを有する第2の線路11bと、第2の線路11bの他端に接続された基本波の1/4波長の長さを有する第3のオープンスタブ12bおよび基本波の1/8波長の長さを有する第4のオープンスタブ13bと、を備える。

(もっと読む)

リニアライザ

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

光変調器駆動回路

【課題】分布定数型増幅器を用いた光変調器の駆動回路であって、光変調器からの光出力の立ち上がり時間や立ち下がり時間を短くし得る駆動回路を提供する。

【解決手段】光変調器駆動回路は、複数の第1の非反転増幅器及び反転増幅器を備える。第1の非反転増幅器は、入力端と出力端との間に設けられている。第1の非反転増幅器はそれぞれ、入力端からの入力信号を固有の遅延時間で受け、出力端において第1の遅延時間で出力信号を与える。反転増幅器は、入力端と出力端との間に設けられている。反転増幅器は、入力信号を受け、出力端において第1の遅延時間より大きい第2の遅延時間で出力信号を与える。

(もっと読む)

高調波処理回路、高周波増幅器及び高周波発振器

【課題】広帯域での2倍波整合を取れず、高効率化できる周波数範囲が狭い。

【解決手段】伝送線路2から構成されるメイン線路と、抵抗6と伝送線路5、7とが直列接続された回路から構成され、メイン線路と並列接続されたサブ線路と、一端がメイン線路とサブ線路との接続点に接続されたオープンスタブ3、4とを含んで構成される。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

電力合成器

【課題】 電力合成器の横寸法を低減しつつ、横寸法の低減に伴う特性劣化を防止する。

【解決手段】 入力側から第1線路、折返し線路、第2線路、直線線路が接続される直列回路を構成し、入力側が入力端子に接続される第1インピーダンス変成器と、第1インピーダンス変成器と同構成の第2インピーダンス変成器と、第1及び第2インピーダンス変成器とループを構成するアイソレーション回路と、第1及び第2インピーダンス変成器が共有する出力接点と出力端子との間に配置される出力インピーダンス変成器とを有する電力合成器であって、第1線路と第2線路は互いに平行に配置され、ループの横縦アスペクト比が1より小さく、第1線路の線幅を第1折返し線路の線幅より狭くして入力信号位相を90度回転し、アイソレーション回路で入力インピーダンスと整合し、出力インピーダンス変成器で出力インピーダンスと整合する。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

電流共有増幅器を用いた信号増幅

【課題】電流共有増幅器を用いた信号増幅を提供する。

【解決手段】電力増幅器は増幅段を有する。増幅段はトランジスターを有する。また少なくとも1つの増幅段は駆動段を有する。増幅段は、第1のトランジスターと有し及び第1の出力電力と関連付けられた第1の増幅段、並びに第2の出力電力と関連付けられた第2のトランジスターを有する第2の増幅段、を有する。電流共有結合は、第1の増幅段と第2の増幅段を結合する。第1の増幅段と第2の増幅段は、電流共有結合を通じて電流を共有する。電流共有結合は、第1の出力電力と第2の出力電力のスケーリングを助ける。

(もっと読む)

電子回路

【課題】分布定数線路の長さの誤差または製造ばらつき等による特性変動を抑制すること。

【解決手段】制御端子と、第1端子と、第2端子と、を有する第1トランジスタT1と、制御端子に前記第1トランジスタの第2端子が接続し、第2端子に直流電源が接続される第2トランジスタT2と、前記第2トランジスタの第1端子から前記第1トランジスタの第2端子に直流電流を供給する、互いに独立した配線からなる複数の直流経路11、12と、前記複数の直流経路内にそれぞれ直列に設けられた分布定数線路L11、L12と、を具備する電子回路。

(もっと読む)

高周波処理回路

【課題】発振抑制用の抵抗を備えながら高周波処理による高効率化を図る。

【解決手段】分配された高周波信号を伝送線路14a,14bの一端の入力部13a,13bに供給し、伝送線路14aは直列接続された伝送線路15aを介して被増幅用高周波信号として出力部16aから次段の増幅用トランジスタに供給する。伝送線路14bは直列接続された伝送線路15bを介して被増幅用高周波信号として出力部16bから次段の増幅用トランジスタに供給する。伝送線路14a,15aの接続点Paに一端を接続したスタブ19aと伝送線路14b,15bの接続点Pbに一端を接続したスタブ19bとの間に発振抑制用の抵抗R1を介挿接続した。接続点Pa,Pbの電位差がない場合は、抵抗R1が見えない状態となり、スタブ19a,19bは高周波信号処理の効率化に寄与し、抵抗R1はセルA,B間のループ発振の抑制させることが可能となる。

(もっと読む)

1 - 20 / 195

[ Back to top ]