Fターム[5J079GB02]の内容

電気機械共振器を用いた発振回路 (23,106) | 帰還路を含む共振部の構成(圧電発振回路のみ) (135) | 振動子に並列に付加要素 (18)

Fターム[5J079GB02]に分類される特許

1 - 18 / 18

圧電振動回路

【課題】

インバーターを用いて大きな負性抵抗を得、さらに広い発振周波数可変幅を得る圧電発振回路を提供する。及び、大きな負性抵抗を得ることができることを論理的に証明する。

【解決手段】

圧電振動回路として、インバーターの入出力間にコンデンサーと圧電振動子を並列接続した回路と、第1のコイル、第2のコイルを直列接続した回路を備え、第1のコイル、第2のコイルの接続点と回路の接地点間にパスコンデンサーを備え、接続点と接地点間を交流に対して短絡させ、さらに電源と接地間にはコンデンサーを挿入し、交流に対して短絡させ、前記インバーターの電源端子と接地端子間に電圧を印加し、発振回路として構成した。

(もっと読む)

共振回路及びその製造方法並びに電子装置

【課題】振動子の構造寸法のばらつきに起因する共振周波数の変動を抑制することのできる共振回路及びその製造方法を実現する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極12、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極13を有するMEMSレゾネータ10と、該MEMSレゾネータにバイアス電圧を印加する電圧印加手段20と、を具備し、前記電圧印加手段は、前記可動部と同じ層で構成され該層の厚みで抵抗値が変化する補償用抵抗R11と、該補償用抵抗に接続され前記可動部と異なる層で構成される基準抵抗R12とを備え、前記補償用抵抗と前記基準抵抗の接続点電位を前記MEMSレゾネータの第1の端子と第2の端子のうちの少なくとも一方の端子10bに出力する分圧回路を有する。

(もっと読む)

共振回路及びその製造方法並びに電子装置

【課題】振動子の構造寸法のばらつきに起因する共振周波数の変動を抑制することのできる共振回路及びその製造方法を実現する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極12、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極13を有するMEMSレゾネータ10と、該MEMSレゾネータにバイアス電圧を印加するための電圧印加手段20と、を具備し、前記電圧印加手段は、前記可動部を構成する層と同じ層で構成され、該層の厚みで抵抗値が変化する補償用抵抗R11と、該補償用抵抗に接続され、前記可動部を構成する層と異なる構造で構成される基準抵抗R12とを分圧抵抗とし、前記補償用抵抗と前記基準抵抗の接続点電位を前記MEMSレゾネータの少なくとも一方の端子10bに出力し、前記抵抗値の変化により前記層の厚みと正の相関を有する前記バイアス電圧を前記振動子に与える分圧回路を有する。

(もっと読む)

発振回路

【課題】安定して発振を停止させる発振回路を提供する。

【解決手段】発振を停止させるときに、インバータ回路12の入力端子と出力端子とをショートさせる。これにより、インバータ回路12のゲインが低下するので、発振停止時にオーバーシュート、アンダーシュートの発生がない安定した発振回路を提供することができる。

(もっと読む)

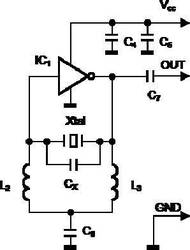

圧電発振回路

【課題】僅かな容量変化で発振周波数の発振周波数の可変幅を広げることができるCMOSインバータ型の圧電発振回路を提供する。

【解決手段】所定の周波数で発振する圧電振動子Xtalと、圧電振動子Xtalと並列に接続され、圧電振動子Xtalの発振出力を帰還させて増幅するCMOSインバータ10とを備える。そして、CMOSインバータ10の入力と接地との間には、第1のインダクタL2と第1のコンデンサC2とを直列に接続した第1の直列回路11が設けられている。またCMOSインバータ10の出力と接地との間には、コイルなどの第2のインダクタL3と第2のコンデンサC3とを直列に接続した第2の直列回路12が設けられている。さらに圧電振動子xtalに対して夫々並列に第3のコンデンサC4と抵抗R4とを接続するようにしている。

(もっと読む)

圧電発振器

【課題】被覆材を用いて振動子電極を両面とも絶縁することなく直接液体に浸漬可能で、液相中・気相中を問わず安定して発振可能な圧電発振器を提供する。

【解決手段】所定の周波数で励振される圧電振動子Zxtと、圧電振動子Zxtを励振させる論理素子INVと、圧電振動子Zxtに並列接続される容量素子Ceと、論理素子INVの出力に接続される第1のインダクタz2および第1のパスコンデンサCp1と、論理素子INVの入力に接続される第2のインダクタz3および第2のパスコンデンサCp2と、を備え、論理素子INVの出力より第1のインダクタz2を介して接地すると共に、論理素子INVの入力より第2のインダクタz3を介して接地することにより、容量素子Ceと第1のインダクタz2と第2のインダクタz3とが、圧電振動子Zxtの発振周波数において共振するタンク回路を構成する。

(もっと読む)

水晶発振器

【課題】従来の発振回路では、電圧可変容量と電源電圧間に大きな容量の固定容量が必要になり小型化の妨げになっていた。また大きな寄生容量が電圧化変容量に並列に挿入される構成のため、大きな周波数可変幅を得ることが難しかった。

【解決手段】帰還抵抗と反転増幅回路と水晶振動子を並列に接続し、反転増幅回路の入出力両側の接続点を直流カット容量と負荷容量を介して接地し、さらに前記直流カット容量と負荷容量の入出力両側の接続点を電圧可変容量を介して接続し、この電圧可変容量の両端に制御信号を印加して周波数調整を行う構成とする。

(もっと読む)

発振器

【課題】 周波数の温度依存特性をMEMSキャパシタの温度依存特性を利用して自動的に補正する、MEMS振動子を用いた発振器を提供する。

【解決手段】 機械的に振動するMEMS振動子と、MEMS振動子の共振周波数で発振して発振信号を出力する出力用発振回路と、周囲の温度によってアノード電極とカソードビームの距離が変わり、容量値が変化するMEMSキャパシタとを備える。

(もっと読む)

発振回路

【課題】動作電圧範囲の広い発振回路を提供する。

【解決手段】両端にキャパシタc1、C2が接続された振動子11と、出力抵抗R1を介して振動子11に並列接続されたインバータ12を有する反転増幅部13と、インバータ12に並列接続されたトランスミッションゲート14、15を有する帰還抵抗部16と、同一導電型で、閾値電圧の異なるn型第1および第2MOSトランジスタM1、M2の直列回路を有し、電源電圧Vddのレベルに応じて、第1および第2MOSトランジスタM1、M2が相補的にオンまたはオフして帰還抵抗部16の抵抗値を可変するための制御信号A1、A2を出力する制御手段17と、を具備する。

(もっと読む)

発振回路

【課題】自励発振が起こらず、出力対称性を確保できるようにした発振回路を提供する。

【解決手段】コルピッツ型の水晶発振回路において、CMOSインバータINV1の出力側(ノードN1)と電源VDDとの間に、CMOSインバータINV1の帰還バイアス電圧を高くするためのトランジスタMP1と発振出力が無いときONするトランジスタMP2とを直列接続して、電源投入初期時にそのノードN1をVDD/2より高い電圧にプルアップし、正常発振が開始してノードN3の電圧が所定値に達すると、トランジスタMP2をOFFしてノードN1のプルアップを解除する。また、CMOSインバータINV1の出力を反転するCMOSインバータINV2を接続し、その出力側のノードN2にアンド回路AND1を接続し、正常発振が開始してノードN3の電圧が所定値に達したとき、それから遅延回路DL1の遅延の後に、アンド回路AND1のゲートを開いて、ノードN2の発振信号を出力端子OUTに出力する。

(もっと読む)

発振器

【課題】 従来、発振周波数を選択するための負性抵抗の調整は製造段階で行うのみであって、経時変化に対応した調整は不可能であるという問題点があり、簡易な構成で、周波数選択特性を経時変化に応じて容易に調整することができる発振器を提供する。

【解決手段】 発振回路の周波数を選択可能な帰還ループに、インダクタンスLとバリキャップダイオードC3とを直列に接続した周波数選択回路10を設け、バリキャップダイオードC3の容量を電気的に制御することにより、負性抵抗を調整する発振器である。

(もっと読む)

圧電振動子の駆動装置および超音波髪処理装置

【課題】本発明は、負荷が変化した場合でも安定的に発振し得る圧電振動子の駆動装置および該駆動装置を用いた超音波髪処理装置を提供する。

【解決手段】本発明では、コルピッツ型自励発振回路によって圧電振動子PZを駆動するための圧電振動子の駆動装置1において、圧電振動子PZが接続された場合に、圧電振動子PZと並列に接続されるように、コンデンサC5とコイルL2との直列回路をコルピッツ型自励発振回路にさらに備える。

(もっと読む)

発振回路

【課題】低消費電力でありながら大きな負性抵抗を得ることができる発振回路を提供する。

【解決手段】発振回路は、SAW振動子Xと、SAW振動子Xと信号路を介して並列接続され発振駆動されるCMOSインバータA1〜A3と、CMOSインバータA1〜A3の出力側と入力側との間に、CMOSインバータA1〜A3の出力側から入力側に信号が正帰還するように、接続された負性抵抗増加回路10と、負性抵抗増加回路10とCMOSインバータA1〜A3の入力側との間に接続する容量素子としての帰還用コンデンサCfと、を含む。

(もっと読む)

水晶発振器

【目的】水晶振動子の等価並列容量を相殺し、設計を容易にして例えば周波数可変幅を広げて雑音の少ない高周波水晶発振器を提供する。

【構成】増幅率を1以上とした発振用増幅器と前記発振用増幅器の入出力間を正帰還とする帰還回路とからなり、前記帰還回路には等価並列容量を有する水晶振動子及び前記水晶振動子の両端子間に設けられて前記等価並列容量を相殺する中和回路とを備えた水晶発振器において、

前記中和回路は第1及び第2電流反転回路との出力側が前記水晶振動子の両端子間に接続し、前記第1及び第2電流反転回路との入力側の間に中和コンデンサを接続してなり、

前記第1及び第2電流反転回路は前記等価並列容量の電流と同一方向とした中和コンデンサの電流方向を反転し、前記中和回路の両端子間の電流を前記等価並列容量及び前記中和コンデンサの電流とは逆向きにしたことを特徴とする水晶発振器。

(もっと読む)

水晶発振器

【目的】本発明は水晶共振子を設けて発振周波数の相雑音を小さくし、Q値の高い水晶共振子である故にその帯域幅が狭くて発振周波数が通過しないことによって生ずる水晶発振器の発振停止を防止する。

【構成】インダクタ成分としての水晶振動子に分割コンデンサを接続してなる共振回路と、前記水晶振動子と分割コンデンサの接続点にベースを前記分割コンデンサの接続点にエミッタを接続した発振用トランジスタと、前記分割コンデンサの接続点とエミッタとの間に設けた負荷抵抗を有する帰還線路と、前記帰還線路に挿入された水晶共振子とからなる水晶発振器において、前記水晶共振子に並列に抵抗を接続した構成とする。

(もっと読む)

発振器結晶の温度を検出する装置

特に移動無線機器の支持体上に配される発振器結晶2の温度を検出する装置では、検出された温度は発振器結晶2が受ける温度のできるだけ正確なレプリカであるべきである。この目的のために、温度センサ7は、発振器結晶2又は発振器結晶ハウジング2’と同じ周囲温度を受けるように、支持体1上に配される。温度センサ7および発振器結晶2は、電気的に並列となるように位置する。  (もっと読む)

(もっと読む)

VCXOの起動時間を短縮するための方法と装置

無線端末(10)の所望の基準周波数を生成するための、低減された起動時間を有するVCXO(Voltage Controlled Crystal Oscillator)(100)のような電圧制御発振器(100)が本願明細書において記載されている。本発明によれば、VCXO(100)は、電圧コントローラ(110)によって発振器(120)に印加された可変電圧に基づいて、所望の基準周波数を生成する発振器(120)を含む。加えて、VCXO(100)は、発振器(120)に伴うキャパシタンスを低減するためバイアス電圧を発振器の入力ノードに印加し、VCXO(100)のDC電流消費または同調レンジに悪影響を与えること無く起動時間を低減する起動コントローラ(130)を含む。  (もっと読む)

(もっと読む)

圧電発振回路

【目的】周波数可変幅が大きく雑音を小さくした圧電発振回路を提供する。

【構成】圧電振動子と発振回路とを接続して発振閉ループを形成してなる圧電発振回路において、前記圧電振動子の端子間に位相反転器とコンデンサの直列回路を接続し、前記コンデンサの容量と前記圧電振動子の並列容量とを相殺する構成とする。

(もっと読む)

1 - 18 / 18

[ Back to top ]