Fターム[5J081GG06]の内容

LC分布定数、CR発振器 (9,854) | 出力構成 (309) | 出力回路 (223) | 分岐・分配・選択切換回路 (18)

Fターム[5J081GG06]に分類される特許

1 - 18 / 18

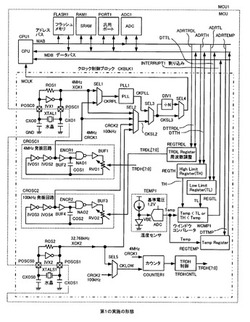

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

発振器およびMMIC

【課題】 高周波の発振器において、プロセスバラツキにより発振周波数が仕様範囲から外れてしまう問題がある。通常はトリミング等により周波数調整を行う方法がある。しかし、高周波発振器を樹脂で封止するトリミングを行うことはできない。さらに、樹脂により寄生容量が変化してしまうため樹脂封止前後で発振周波数が変化してしまうため、別の方法による周波数調整方法が必要となる。

【解決手段】 同一基板上に発振器を複数設けて、それぞれの発振周波数が異なるようにする。また、各発振器を外部からの印加電圧によって発振/停止を制御できるようにして、複数の発振器の中から最適な発振器一台のみを発振させる。

(もっと読む)

温度補償型圧電発振器

【課題】圧電振動素子を搭載した温度補償型圧電発振器の小型化が進んでも、消費電力が少なく、短時間で立ち上がり、温度補償型圧電発振器の表面に新たに外部接続用電極端子を設けることがない温度補償型圧電発振器を提供することを課題とする。

【解決手段】第1のスイッチは、機能端子から入力された信号により電源電圧端子と増幅回路部の第2のインバータとの間を接続または切断し、第2のスイッチは、切替信号制御回路部からの切替信号により、第1のスイッチ又は可変容量ダイオードのカソードと、機能端子との接続を切り替え、第3のスイッチは、チップセレクト回路部からの切替信号により、メモリ部又は、第2のスイッチと、機能端子との接続を切り替える。

(もっと読む)

4位相出力電圧制御発振器

【課題】小型で低価格および高精度な位相差を持った4位相出力電圧制御発振器を提供すること。

【解決手段】1つの電圧制御発振器、3つのハイブリッドカプラと1つの遅延線を備え、電圧制御発振器の出力を3つのハイブリッドカプラと1つの遅延線により4つに分岐して互いに(π/4)異なる位相差の4信号を出力する4位相出力電圧制御発振器であって、1つの電圧制御発振器回路4が多層プリント配線板上の最上層に形成され、3つのハイブリッドカプラ回路21、22、23と1つの遅延回路10が同じ多層プリント配線板の内層で構成されると共に、これ等ハイブリッドカプラ回路と遅延回路はそれぞれトリプレートストリップライン導体構造を有しかつ多層プリント配線板内層の同一平面上にそれぞれ形成されていることを特徴とする。

(もっと読む)

2位相出力電圧制御発振器

【課題】小型で低価格および高精度な位相差を持った2位相出力電圧制御発振器を提供すること。

【解決手段】1つの電圧制御発振器とハイブリッドカプラとを備え、電圧制御発振器の出力をハイブリッドカプラにより2つに分岐して互いに(π/4)異なる位相差の2信号を出力する2位相出力電圧制御発振器1であって、1つの上記電圧制御発振器回路4が多層プリント配線板上の最上層に形成され、上記ハイブリッドカプラ回路2が同じ多層プリント配線板の内層で構成されると共に、上記ハイブリッドカプラ回路2はトリプレートストリップライン導体構造を有しかつ上記多層プリント配線板内層の同一平面上に形成されていることを特徴とする。

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

バースト発振器

【課題】従来のバースト発振器の構成では、発振周波数を開閉するスイッチにおけるリークにより、オフ状態の休止期間であっても高周波の発振信号が出力にリークして出てしまうという課題があった。

【解決手段】本発明のバースト発振器は、発振信号を断続的に出力端から出力するバースト発振器であって、発振信号を発生する発振器と、発振器の電源供給ラインと出力端との間に接続され発振信号の出力端からの出力を断続させるスイッチと、出力端から高周波アースラインに順方向に接続されたダイオードと、発振器の出力と出力端の間に接続され発振信号の波長λの1/4ライン長をもつ伝送ラインとを備える。

(もっと読む)

半導体装置

【課題】 端子数を削減しながら、半導体装置に搭載されている外部発振子を用いた発振回路と自励発振回路を1品種で使い分けることができるようにする。

【解決手段】 半導体装置20には、バイアス検知回路1、発振回路2、発振回路3、インバータINV1、インバータINV2、クロックドインバータCINV1、クロックドインバータCINV2、及び端子Pad1乃至3が設けられている。発振回路2から生成される高精度のクロック信号CLKを使用する場合、外部の低電位側電源Vss側に設けられた外部端子OPad3と外部端子Opad1の間を接続する。一方、自励発振回路である発振回路3から生成される比較的低消費電流のクロック信号CLKを使用する場合、抵抗R1を介して外部の高電位側電源Vdd側に設けられた外部端子Opad2と外部端子Opad1の間を接続する。

(もっと読む)

クロック信号の生成及び分配装置

【課題】 数ギガヘルツ以上の高周波域においても、高精度のクロック信号を生成し分配可能なクロック生成分配装置を提供すること、及び20GHzに達するような高周波域においても、各電圧制御発振器が同一位相で発振し、希望する周波数のクロック信号が生成でき、高周波クロック信号を、より安定にチップ内の各部に分配する分散VCO型クロック生成分配装置を提供すること。

【解決手段】 各電圧制御発振器としてLC共振型電圧制御発振器を採用し、さらにその発振ノード間の接続配線のインダクタ成分を相対的に小さくして、あるいは、LC共振発振器を注入同期により同期して発振させることにより、各LC共振型電圧制御発振器が安定して同一位相で発振するようにする。

(もっと読む)

発振回路

【課題】 小型化かつ位相雑音を低減することができる発振回路を提供することを課題とする。

【解決手段】 差動対を構成する第1及び第2のトランジスタ(101,102)と、第1及び第2のトランジスタの第1の端子側に接続される出力合成回路(103)と、第1及び第2のトランジスタの第2の端子側に接続される電流源(106)とを有する発振回路が提供される。

(もっと読む)

電圧制御発振器

【課題】各発振周波数において出力信号の品質を劣化させずにすむような2周波数選択電圧制御発振器を提供することにある。

【解決手段】発振周波数を決定する帯域通過フィルタと、これの前段および後段に設けられた整合回路と、フィードバックループの損失を補完するための増幅回路と、発振条件および発振周波数を決定する固定移相器と、発振周波数を外部からの電圧信号によってコントロールするための電圧制御可変移相器と、外部出力とループ内出力への分配を決める分配器とをシリーズに配置して構成される電圧制御発振器を2回路有し、更に各該電圧制御発振器の電源切り替え回路と各該電圧制御発振器の出力信号を束ねる結合回路を有する2周波数電圧制御発振器において、前記結合回路として、キャパシタ、インダクタ、抵抗から成る2入力低域通過フィルタの回路構成を持たせる。

(もっと読む)

高周波発振器

【課題】 簡素な構造で、優れたQ値、およびC/N特性を有し、負荷特性に優れる高周波発振器を構成する。

【解決手段】 高周波発振器は、共振回路10と、該共振回路10に接続するとともに出力端子OUTに接続する帰還増幅回路1とを備える。帰還増幅回路1は、ベースが共振回路10に接続し、コレクタがインダクタL11を介して駆動電源端子Vbに接続するとともにコンデンサC2を介してグランドに接続することにより高周波的に接地し、エミッタがエミッタ抵抗R1、インダクタL1の直列回路とコンデンサC1とを介してグランドに接続し、ベース−エミッタ間に帰還用コンデンサC3が接続した発振用トランジスタTr1を備える。この発振用トランジスタTr1のベースがバイアス抵抗R12を介して出力端子OUTに接続する。

(もっと読む)

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

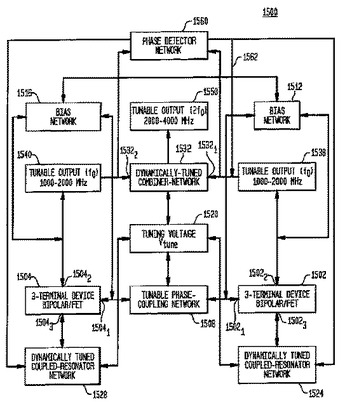

集積型低ノイズ・マイクロ波広帯域プッシュプッシュ電圧制御発振器

広帯域周波数選択性をサポートする同調電圧回路網を介して1対の3端子装置の端子に結合された周波数可変な結合共振器回路網を備えた回路を含む電圧制御発振器が提供される。集積回路形態への組み込みに適した広帯域周波数可変共振器も提供される。

(もっと読む)

(もっと読む)

伝送線路型共振器を用いた高周波発振器

【課題】回路の小型化や低損失化に適し、例えば4相Push-Push発振器をも実現可能とする高周波発振器を提供する。

【解決手段】高周波共振器に2つの発振用能動素子を接続して前記高周波共振器を共用した2つの発振系を形成し、前記発振系の出力を合成してなる高周波発振器において、前記高周波共振器を伝送線路型共振器から形成し、前記伝送線路型共振器の互いに逆相関係にある2つの共振波動点に前記発振用能動素子を接続し、さらに前記伝送線路型共振器の電気的対称点に合成線路を接続して高周波出力を得たことを基本的な解決手段とする。

(もっと読む)

1 - 18 / 18

[ Back to top ]