Fターム[5J098AD15]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 調整可能、制御可能 (185) | 調整の簡素化、容易な調整 (24)

Fターム[5J098AD15]に分類される特許

1 - 20 / 24

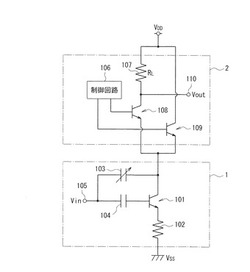

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

フィルタ較正

【課題】費用対効果が大きく、簡単であり、さらに正確な、フィルタを較正する方法を提供する。

【解決手段】フィルタ104、116は、較正中に発振器として再構成される。フィルタを再構成するために、スイッチおよび/または他の構成が使用されて、フィルタの負のフィードバックループに対して正のフィードバックループを再構成する。フィルタのコンポーネントを調整して、所望のフィルタ特性に対応する発振を達成するために発振パラメータが次に測定される。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

受信装置及びイメージ除去方法

【課題】ウィーバー方式又はハートレー方式等のイメージ除去構成と複素フィルタを組み合わせて用いる場合に、希望信号及びイメージ信号の直交性を共に維持する。

【解決手段】直交ミキサ(ミキサ101及び102)は、RF信号をダウンコンバートし、I信号及びQ信号を生成する。複素フィルタ103は、正の周波数領域と負の周波数領域との間で非対称な周波数利得特性を有し、I信号及びQ信号に含まれるイメージ信号を希望信号に比べて抑圧する。直交補償回路106は、複素フィルタ103の後段に配置され、複素フィルタ103によってイメージ抑圧されたI信号及びQ信号の間における希望信号の位相差誤差及び振幅誤差を打ち消すように、I信号及びQ信号を補正する。また、制御回路117は、複素フィルタの後段にてI信号及びQ信号に現れるイメージ信号の位相差誤差及び振幅誤差を打ち消すように、複素フィルタ103の素子特性を調整する。

(もっと読む)

フィルタ回路

【課題】高速に動作することが可能であり、周波数特性制御するためのフィルタ制御信号生成回路が小規模でしかも設計に要する時間が短時間で済むようなフィルタ回路を提供する。

【解決手段】Gm−Cフィルタのフィルタ制御信号生成回路を、MOSトランジスタ32、MOSトランジスタ32とゲート同士が接続されるMOSトランジスタ33、MOSトランジスタ32とドレイン同士が接続されるMOSトランジスタ30、ドレインとゲートが接続され、MOSトランジスタ30とゲート同士が接続され、MOSトランジスタ33とドレイン同士が接続されるMOSトランジスタ31、MOSトランジスタ30〜33のうちの1つのソースに接続される抵抗素子34によって構成し、MOSトランジスタ33,30のドレインに接続される出力端子35または出力端子36からフィルタ制御信号を出力させる。

(もっと読む)

周波数依存性消去回路、およびそれを用いた位相シフト回路

【課題】入力信号に対して出力信号の振幅に変化がなく位相のみが90°ずれており、かつ広帯域に渡って回路定数の変更なしに精度を保つことができる周波数依存性消去回路、およびそれを用いた位相シフト回路を提供する。

【解決手段】周波数依存性消去回路2は、入力端子に積分器5および微分器6をそれぞれ接続し、前記積分器5および微分器6を掛け算器8に接続し、前記掛け算器8で前記積分器5および微分器6の出力を掛け合わせ、信号振幅の周波数依存性を消去し、位相のみを90度シフトするように構成する。

(もっと読む)

フィルタ回路

【課題】本発明は、フィルタリング特性調整機能を有するアナログフィルタを有するフィルタ回路に関し、アナログフィルタのフィルタリング特性を簡易な補正回路によって補正する機能を備える。

【解決手段】アナログフィルタ50と、レプリカ回路としての発振器61と、周波数比較ロジック62を備え、周波数比較ロジック62で、その発振器61の発振周波数が基準周波数となるように、発振器61とアナログフィルタ50との双方を同時に調整する。

(もっと読む)

パッシブイコライザ

【課題】ゲインを増大させるために負のインピーダンスを用いることができるパッシブイコライザを提供する。

【解決手段】

ゲインを増大させるために負のインピーダンスを利用するパッシブイコライザは、第1のRCループと、第2のRCループと、カスケードRL回路および交差結合反転器ユニットとを含む。第1のRCループおよび第2のRCループのそれぞれは、第1の抵抗器と、ノードで第1の抵抗器に直列に接続され、それによって抵抗器直列を形成する第2の抵抗器と、抵抗器直列に並列に接続されるコンデンサとを含む。カスケードRL回路は、RCループの間に接続され、第5の抵抗器と、第6の抵抗器と、第5の抵抗器と第6の抵抗器との間に接続されるインダクタとを含む。優れた高周波数ゲインを得るために負のインピーダンスの特徴を用いるために、交差結合反転器ユニットは、RL回路に並列に接続され、RCループの間に接続される。

(もっと読む)

フィルタ回路および無線機器

【課題】中心周波数を調整する周波数チューニングが容易に行えるフィルタ回路を提供する。

【解決手段】

本発明に係るフィルタ回路10は、チューニング時、スイッチ回路4を導通状態として、トランスコンダクタンス回路6を含むフィードバックループを有する発振回路8を構成する。発振回路8は、スイッチ回路4によりLCRタンク回路2をバイパスして、LCRタンク回路1とインダクタ3とを負荷回路としている。上記フィードバックループは、発振回路8の出力をトランスコンダクタンス回路6に入力する。スイッチ回路4を用いて以上のように発振回路8を構成することで、フィルタ回路10の中心周波数と発振回路8の発振周波数とが同一となる。それゆえ、特許文献1に開示されている自動チューニング技術を用いて容易に周波数チューニングを行うことができる。

(もっと読む)

遅延素子、可変遅延線及び電圧制御発振器並びにそれを備えた表示装置及びシステム

【課題】温度が変化しても中心発振周波数が安定している電圧制御発振器等を、簡単な構成で提供する。

【解決手段】入力信号Viに遅延量τdを加えて出力信号Voとする遅延発生部11と、遅延τdを制御する遅延制御部12とを備えている。遅延制御部12は、遅延量τdを調節する第一の制御信号としての制御信号S1を出力する遅延調節回路13と、温度による特性変化を補償する第二の制御信号としての制御信号S2を出力する温度補償回路14とを有し、制御信号S1と制御信号S2とを合成して得た第三の制御信号としての制御信号S3を遅延発生部11へ出力することにより遅延量τdを制御する。遅延制御部12は、遅延調節回路13と温度補償回路14とを直列に接続することにより、制御信号S3を得ている。

(もっと読む)

フィルタ周波数特性検出装置及びフィルタ周波数特性テスト装置

【課題】複雑な回路構成とすることなく、周波数特性の検出を容易に行う。

【解決手段】フィルタ周波数特性検出装置は、第1及び第2の信号が入力されるフィルタ11と、このフィルタを通過した第1及び第2の信号を比較するコンパレータ13と、このコンパレータに入力される第1及び第2の信号にオフセットを与えるオフセット調整回路12と、コンパレータの出力結果に基づき第1及び第2の信号の振幅の変化をデューティ比として検出するデューティ比検出回路14と、このデューティ比検出回路の検出結果に基づきフィルタの周波数特性を調整する周波数特性調整回路15とを具備する。

(もっと読む)

インピーダンス調整回路

【課題】 DIMMに実装されているSDRAMのOCDインピーダンス測定・調整が短時間で実行でき、設計が容易なインピーダンス調整回路を提供する。

【解決手段】 調整コードに対応してインピーダンスが可変の出力ドライバを有する、複数のメモリチップD0〜D7をランク選択信号とデータマスク信号の組合せにより選択して、インピーダンスの測定及び調整を行うインピーダンス調整回路において、異なるランクのメモリチップD0〜D7にランク選択信号をそれぞれ出力する複数のランク選択回路31,32と、ランクごとにメモリチップを選択するデータマスク信号をそれぞれ出力する複数のデータマスク選択回路41〜48とを備えたことを特徴とする。

(もっと読む)

可変容量回路

【課題】可変容量ダイオード2への印加逆制御電圧変化対その容量変化の関係を線形にする補正手段に負性インピーダンス変換回路3を用い、容量変化範囲を狭くせず、複雑な補正手段を用いずに済む可変容量回路を提供する。

【解決手段】非接地側入力端子1aと接地側入力端子1b間に接続され、可制御電圧形成装置6の可変制御電圧が供給される可変容量ダイオード2と、入力端と出力端と接地端を有し、入力端が記非接地側入力端子1aに、出力端が容量素子5を介して接地側入力端子1bに接続された負性インピーダンス変換回路3を備え、容量素子5の容量を非接地側入力端子1aと接地側入力端子1b間に形成される分布容量に略等しい値に選び、可制御電圧形成装置6の調整によって可変制御電圧を線形変化させるに伴い可変容量ダイオード2の容量を対数的に変化させるように形成した。

(もっと読む)

減衰器

【課題】 簡単な回路構成で減衰比の調整が可能な減衰器を実現する。

【解決手段】 減衰比の調整が可能な減衰器において、入力電圧信号を低周波成分電流に変換する抵抗と、前記入力電圧信号を高周波成分電流に変換する容量と、抵抗と容量が並列接続された負荷回路と、前記低周波成分電流及び前記高周波成分電流を互いに独立した割合で加算した電流を前記負荷回路に供給する減衰比調整手段と、前記減衰比調整手段に流れ込む前記低周波成分電流の電流値を調整する入力電流値調整手段とを設ける。

(もっと読む)

帯域通過型フィルタ

【課題】本発明は、帯域通過型フィルタに関し、簡素な構成で周波数や帯域幅を連続的に変更することにある。

【解決手段】入力信号を2分配する分配器24と、分配器24により分配された一方の信号をカットオフ周波数f1で低域通過させる第1の低域通過フィルタ28と、第1の低域通過フィルタ28から出力される信号を位相が180°ずれるように変換する位相器30と、分配器24により分配された他方の信号と位相器30から出力される信号とを合成する混合器32と、混合器32から出力される信号を、第1の低域通過フィルタ28のカットオフ周波数f1よりも高いカットオフ周波数f2にて低域通過させる第2の低域通過フィルタ34と、を備える。また、第1及び第2の低域通過フィルタ28,34をそれぞれ、独立してカットオフ周波数の変更が可能な低域通過フィルタとする。

(もっと読む)

可変容量回路とこれを用いた電圧制御発振回路

【課題】低電圧動作に適し、動作周波数レンジが広げられ、安定動作が得られ、位相ノイズやジッタの低減を図れる。

【解決手段】電圧可変容量回路は、電圧可変容量手段としてのNMOS42と、NMOS42のドレインにソース電位と異なる電位を供給するための電位供給部41とから構成されている。NMOS42のゲート42gと接地端子GNDとの間に発生する等価容量Cgを可変できる電位範囲や、変化の傾きを電気的・回路設計的に調整することが可能となる。更に、電圧制御端子VCに印加する制御電位vcに対して等価容量Cgは単調に変化し、制御電位vcの有効な電位範囲は拡大する。前記電圧可変容量回路をVCOに用いることで、VCOの発振周波数fは、電圧制御端子VCに印加する制御電位vcによって、制御できる。

(もっと読む)

アクティブキャパシタ

【課題】一つのオペアンプ2と複数の抵抗と一つのリアクタンス素子からなるアクティブオールパス形90度遅相回路の使用で回路構成を著しく簡素化でき、抵抗の抵抗値の調整でキャパシタンス値を変化できるアクティブキャパシタを提供する。

【解決手段】オペアンプ2とその反転入力端と入力端子1間に接続された第1抵抗3とその非反転入力端と入力端子1間に接続された第2抵抗4とその出力端と反転入力端間に接続された第3抵抗5とその非反転入力端と接地点間に接続されたキャパシタ6とからなるアクティブオールパス形90度遅相回路と、アクティブオールパス形90度進相回路の入出力端子間に接続された第1乃至第3抵抗3、4、5の各抵抗値及びキャパシタ6のインピーダンス値よりも十分に低い抵抗値を有する第4抵抗7を備え、入力端子と接地点間に等価キャパシタを得ている。

(もっと読む)

非線形回路

【課題】 非線形特性を示す非線形素子23に、その非線形特性と相補の非線形特性を有する制御電圧を供給し、当該非線形特性が実質的な線形特性を呈するように補正する非線形回路を提供する。

【解決手段】 オペアンプ7とその負帰還回路8、9とその正帰還回路10と入力抵抗12と第2入力抵抗13とを備え、入力制御電圧を非線形基本制御電圧に変換する非線形基本回路2、分圧抵抗14、15を備え、入力制御電圧を分圧する加重回路3、オフセット電圧源16を備え、オフセット電圧を発生するオフセット電圧付加回路4、第2オペアンプ17とその負帰還回路18、19と第3、第4、第5入力抵抗20、21、22とを備え、非線形基本制御電圧、分圧制御電圧、オフセット電圧を加算出力する加算回路5を有し、第2オペアンプ17の出力に非線形素子23を含んだ被制御負荷回路6が接続される。

(もっと読む)

可変抵抗回路

【課題】 PINダイオード回路1に制御電圧補償回路を接続し、制御電圧Vcの変化に対する高周波抵抗Rfの変化の関係をほぼ直線状にして高周波抵抗Rfの調整がし易い可変抵抗回路を提供する。

【解決手段】 制御電圧VcによりPINダイオード8、9の高周波抵抗Rfが調整されるPINダイオード回路1、制御電圧Vcの一方に、レベルシフト回路2でレベルシフトし、ツェナダイオード回路3でツェナダイオード特性を用いて非線形特性を与える第1手段、制御電圧Vcの他方に、重み付け回路4で電圧オフセットを与える第2手段、第1手段及び第2手段の各出力電圧を加算する加算回路5を備え、加算回路5の出力をPINダイオード回路1に加える際に、レベルシフト回路2のシフト電圧、ツェナダイオード回路3のツェナ特性、重み付け回路4の電圧オフセットを選択調整し、PINダイオード回路1の高周波抵抗Rfの値を制御電圧Vcの変化に対してほぼ直線状に変化するように設定した。

(もっと読む)

チューナ回路

【課題】周波数変換回路前段の前置フィルタの特性の調整作業を容易化し得る回路を内蔵したチューナ回路を提供する。

【解決手段】前置フィルタ10により選択された高周波信号と局部発振器30により生成された局部発振信号とが入力され、差の周波数成分を出力する第1の周波数変換回路22と、第1の周波数変換回路の出力信号から所望の中間周波信号を出力する中間周波フィルタ23と、前置フィルタにより選択された高周波信号を前置フィルタ特性調整時にスルーさせるために付加され、前置フィルタにより選択された高周波信号と局部発振信号とが入力され、差の周波数成分を出力する第2の周波数変換回路25と、中間周波フィルタから出力する中間周波信号と第2の周波数変換回路の出力信号のどちらか一方を選択し、増幅して出力する増幅器24とを具備する。

(もっと読む)

1 - 20 / 24

[ Back to top ]