Fターム[5J106CC44]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | アナログ型 (51) | ラグ・ラグリード型 (16)

Fターム[5J106CC44]に分類される特許

1 - 16 / 16

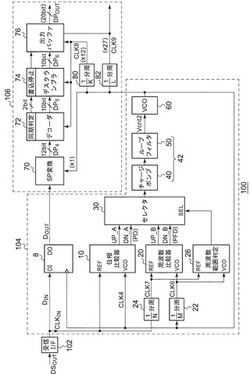

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

位相ロックループ回路

【課題】簡素な回路構成で、電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路1と、検出された位相差に応じた電流を容量に出力するチャージポンプ回路2と、容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路4とを有する位相ロックループ回路にて、制御電圧がロック状態時の電圧であった場合に電圧制御発振回路4の入力部に流れるリーク電流に等しい電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号に電圧制御発振部からの周波数信号を同期させて出力するPLL装置において、外部からの基準信号に不具合が生じても周波数の変動が抑えられるようにすること。

【解決手段】外部からの基準周波数信号の信号レベルを監視し、その信号レベルが設定範囲内であるときには、位相差データ作成手段により作成された位相差に関するデータを用いてPLL制御を行うが、前記信号レベルが設定外れたときには、信号の供給が停止あるいは異常が起きたものと認識して記憶部に記憶されている位相差に関するデータ、例えば蓄積している最新のデータあるいは予め作成しておいたデータに切り替えてPLL制御を行う。

(もっと読む)

PLL装置

【課題】極めて高い周波数安定度が得られるPLL装置を提供すること

【解決手段】恒温槽付き水晶発振器(OCXO)から40MHzの矩形波である周波数信号によりA/D(アナログ/ディジタル)変換部により標準信号をサンプリングし、そのディジタル信号を直交変換部により直交変換処理し、標準信号とOCXOからの周波数信号との位相差に相当する位相のベクトルを複素表示したときの実数部分(I)及び虚数部分(Q)を取り出す。このベクトルの角速度を検出し、この角速度に対応する直流電圧をPWM制御部を介して生成し、OCXOに供給する。

(もっと読む)

位相同期回路

【目的】 入力信号のジッタのみに応じて適切なループフィルタ特性を適用可能なことを課題とする。

【構成】 入力信号INと発振出力OUTとの間の位相差を検出する位相比較器11と、該位相比較器の比較出力を積分するループフィルタ12と、該ループフィルタの出力に対応する周波数の前記発振出力を生成する発振回路13とを備え、入力信号に位相同期した発振信号を出力する位相同期回路であって、入力信号に位相同期し、十分に位相雑音の少ない基準信号PLを生成するPLL回路21と、入力信号と基準信号間の位相差を検出する位相比較器22と、該位相比較器の比較出力を積分するローパスフィルタ23と、該ローパスフィルタの出力を周波数解析して得られた周波数成分に基づき第1の周波数f1を求めると共に、該第1の周波数よりも低い一定の関係にある第2の周波数f2によってループフィルタ12の帯域幅を制御するフィルタ制御部24とを備える。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子側のインピーダンスを低くし、VCOの位相雑音特性の劣化を防ぎ、VCOの固体バラツキや温度変化に対して固有周波数を一定値に保つVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータをアナログ出力する粗調用DAC4と、微調用周波数のデジタルデータをアナログ出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを抵抗R6 で接続し、LPF5の出力とLPF7の出力とをコンデンサC8 で容量結合し、LPF7に電圧制御手段としての可変抵抗R4 を設けたVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

周波数変調器およびこれを用いたFM送信回路

【課題】PLLを用いた周波数変調器を簡素化する。

【解決手段】周波数変調器100において、VCO12は、入力端子13に印加された電圧Vcntに応じた周波数で発振する。分周器14は、VCO12の出力信号Soutを分周する。位相比較器16は、分周器14の出力信号Sfbを、基準クロック信号CKrefと比較し、位相差に応じた電圧Vpcを出力する。ループフィルタ18は、位相比較器16の出力端子17からVCO12の入力端子13に至る経路上に設けられ、位相比較器16の出力電圧Vpcの高周波成分を除去する。ループフィルタ18が位相比較器16の出力端子17からVCO12の入力端子13に至る経路と接続される端子とは別に、変調信号Sinを入力するための端子19をループフィルタ18に設ける。

(もっと読む)

リーク電流補償回路を備えたPLL回路

【課題】ループフィルタを構成するMOSトランジスタのリーク電流による電圧制御発振回路のコントロール電圧の変動を防止し、回路面積の縮小が図られたPLL回路を提供する。

【解決手段】

ループフィルタの電圧をサンプリングし保持するサンプル・ホールド回路と、そのサンプル・ホールド回路により保持された保持電圧とループフィルタの電圧を比較する演算増幅器と、比較結果によりループフィルタから漏洩したリーク電流を補償するリーク電流補償経路を備え、ループフィルタを構成するMOS容量のゲート酸化膜をサンプル・ホールド回路を構成するMOS容量のゲート酸化膜よりも薄いものを用いる。

(もっと読む)

PLL周波数シンセサイザ

【課題】ロックアップタイムが短縮でき、かつ回路規模も小さくて済むPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザにおいて、ループフィルタ7をノッチ周波数がリファレンス周波数に設定されたツインT型ノッチフィルタ71とツインT型ノッチフィルタ71の後ろに直列接続されたローパスフィルタ72とで構成すると共に、ツインT型ノッチフィルタ71の一部を構成する抵抗R2とローパスフィルタ72の一部を構成する抵抗R2とを共用にした。

(もっと読む)

発振器

【課題】電流制御型発振回路を用いた発振器において、位相雑音特性の劣化やデッドロック状態となることを回避して、安定した発振動作を実現することを目的とする。

【解決手段】発振周波数制御回路を構成する差動増幅回路の差動対の各電流経路に抵抗Q1、Q3を挿入し、差動対の出力電流Ia,Ibの直線領域における傾きを緩やかにする。また当該差動対の一方のトランジスタのベースに印加する基準電圧を低く設定することで、直線領域を低電圧側にシフトさせ、低電圧側の飽和領域が生じないようにする。さらに、電流制御型発振回路の出力信号と基準信号との位相の比較結果を発振周波数制御電圧に変換する際に、回路共通の正電圧電源Vccに代えてレギュレータの出力によりの上限電圧を制限することで、直線領域より上側の飽和領域にが移動しないようにする。

(もっと読む)

位相同期回路

【課題】 入力信号と比較信号との位相比較により位相同期化する位相同期回路に関し、ピークジッタの抑圧を図る。

【解決手段】 入力信号INと比較信号COMPとの位相を比較する位相比較器1と、この位相比較器1の比較出力信号を入力するチャージポンプ2と、このチャージポンプ2の出力信号を入力するループフィルタ3と、このループフィルタ3の出力信号を制御電圧として入力する電圧制御発振器4とを含む位相同期回路に於いて、チャージポンプ3と電圧制御発振器4との間に、制御電圧を、位相比較器1の不感帯の外で位相同期状態となるようにシフトする電圧シフト回路6を設けた。

(もっと読む)

無線通信システム

【課題】 従来のPLL回路においては、分周比の切替え後可変分周器の出力(帰還側パルス)の最初の立上がりが基準側分周器の出力(基準側パルス)の立上がりよりも早くなるか遅くなるかは、一義的に決まっておらず、分周比の切替えタイミングに依存してしまい、周波数引込み時間が変動するという問題点があった。

【解決手段】 発振系回路から供給される局部発振信号の周波数は、フィルタからの出力電圧に従って変更され、アンテナから受信される信号と上記局部発振信号とを合成する受信系回路と、第2の制御信号に応答して、上記フィルタに所定の電圧をセットする設定手段と、上記第1の制御信号を生成し、上記発振系回路から供給され上記第1の周波数から上記第2の周波数へ変更される局部発振信号の変化に応じて上記第2の制御信号を生成する制御手段とを含むことようにした。

(もっと読む)

PLL回路

【課題】 周波数を切替えた際に短時間に希望する周波数に収束するものであって、しかもCPUなどを必要としない簡単な構成で、かつ安価なPLL回路を提供する。

【解決手段】 PLL回路は、基準信号S0と出力信号S1とが入力される周波数検出回路6を備えている。周波数検出回路6は、基準信号S0の周波数と電圧制御発振回路4からフィードバックされる出力信号S1の周波数とを比較して、出力信号S1の周波数が所定の範囲内に入ったときに、ローパスフィルタ3に対してアクティブ信号を出力するように構成される。この周波数検出回路6から出力されるアクティブ信号によりローパスフィルタ3の時定数を大きくするように制御している。

(もっと読む)

1 - 16 / 16

[ Back to top ]