Fターム[5J106CC45]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | アナログ型 (51) | 能動型 (18)

Fターム[5J106CC45]に分類される特許

1 - 18 / 18

通信装置、位相同期ループ、移動体および通信方法

【課題】通信装置、位相同期ループ、移動体および通信方法を提供すること。

【解決手段】受信信号の同期保持を行うための位相同期ループ254を備え、前記位相同期ループは、n次の位相同期ループ用の回路構成nを包含する、m次の位相同期ループ用の回路構成m(m>n)、を有するループフィルタ109と、前記ループフィルタにおいて有効化される回路構成を、前記回路構成nと前記回路構成mとで切替える切替部と、を含む、通信装置。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

PLL回路及びそれを用いた周波数設定回路

【課題】ループフィルタ出力での基準周波数成分を十分に落とせ、かつ、PLLループ内の位相余裕を確保できるPLL回路の提供。

【解決手段】本発明のPLL回路は、電気信号により発振周波数が制御される周波数発振器(VCOまたはICO)13からの出力信号が高域通過フィルタ(HPF)14を介して位相検波器11の一方の入力端子に入力され、位相比較器11の他方の入力端子には基準周波数が入力され、前記位相比較器11の出力信号はループフィルタ12を介して、その直流成分を前記電気信号として周波数発振器13を制御する。

(もっと読む)

搬送波同期回路および搬送波同期方法

【課題】局部発振器の周波数ドリフトが大きい場合、及び、周波数同期部の周波数検出精度があまり高くない場合においても、伝送品質を劣化させることなく、高速かつ安定的に搬送波との同期を確立する。

【解決手段】位相同期部52は、周波数同期部51による周波数同期処理後の残留周波数誤差Δf'を検出し、周波数同期部51に帰還させる。周波数同期部51は、収束判定回路82からの収束ステートを監視し、残留周波数誤差Δf'が収束したタイミングにおいて、位相同期部52からの残留周波数誤差Δf'に対する周波数引き込みを行う。本発明は、例えば、無線デジタル通信などの搬送波同期回路に適用できる。

(もっと読む)

位相同期回路

【課題】タイミングジッタをより低く抑えて安定したクロックパルスを得る。

【解決手段】水平・垂直同期分離回路10から分離出力された水平及び垂直同期信号に基づき、Vブランキング期間中の水平位相変動の比較的大きな期間である連続した5Hの水平同期期間においては、各水平同期期間に対応して発生させるサンプリングパルス信号をマスク処理し、このマスク処理されたサンプリングパルス信号に基づいてVCO発振回路50の発振周波数を電圧制御するようにした。

(もっと読む)

位相同期回路および電子機器

【課題】位相同期回路において、発振回路の周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止する。

【解決手段】ゲイン特性情報取得部107Aは、判定基準周波数f1,f2を使って、初期電流Iini と各周波数で発振させるための周波数制御電流Iosciとを合成して電流制御発振部101Aに供給しながら、実動時の電流制御発振部101Aの周波数変換ゲインKcco を規定する判定基準周波数f1,f2の各発振制御信号Iosci_1,Iosci_2の差の情報(Iout_2 )を測定し、そのデータを周波数比較結果保持部172_2に記憶しておく。位相同期動作時には、周波数比較結果保持部172_2に記憶しておいた周波数比較結果fcompのデータD(f2)に基づく制御電流Icpcnt を補正信号として使って、周波数変換ゲインKcco のばらつきが相殺されるように駆動部104Zを制御する。

(もっと読む)

位相同期回路

【課題】入力信号と帰還信号との位相同期を行う位相同期回路に関し、簡単な構成で位相同期引込みの迅速化を図る。

【解決手段】入力信号と電圧制御発振器3の出力又は分周した帰還信号との位相比較を行うチャージポンプを含む位相比較器1と、この位相比較器1の出力信号を、演算増幅器OP1からなるローパスフィルタ2を介して電圧制御発振器3の制御電圧とし、この電圧制御発振器3の出力信号又は分周した信号を帰還信号とする位相同期回路に於いて、ローパスフィルタ2を構成する演算増幅器OP1の参照電圧Vrefを、この演算増幅器OP1と位相比較器1との間に流れる電流が増加する方向に制御して、電圧制御発振器3の制御電圧Vcontを位相引込方向に変化させる手段を備えている。

(もっと読む)

雑音除去を有するループフィルタ

【解決手段】 ループフィルタは、第1及び第2の信号経路720,730、演算増幅器(オペアンプ)736及び雑音除去経路740を含む。第1の信号経路720は、第1の信号に第1の伝達関数を供給する。第2の信号経路730は、第2の信号に第2の伝達関数を供給する。第2の信号は、第1の信号のスケール化バージョンである。キャパシタ734は、因子アルファだけ小さくスケールされる。オペアンプは、第1及び第2の信号経路に結合され、オペアンプ雑音を有する制御信号VCTRLを生成するために第1及び第2の信号経路からの信号を合計することを容易にするように形成される。雑音除去経路740は、オペアンプに結合され、制御信号中のオペアンプ雑音を相殺するのに使用される雑音除去信号VCTRLを生成する。制御信号VCTRL及び雑音消去信号VNは、電圧制御発振器(VCO)内に含まれるバリキャップ750の各ノードに適用される。 (もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】位相比較器のフリップフロップ間の誤差に起因するスプリアスを抑圧することができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】位相比較器33から出力された位相比較信号Dnu(t)を第1の利得値αnuで電圧増幅するとともに、その位相比較器33から出力された位相比較信号Dnd(t)を第1の利得値αnuと異なる第2の利得値αndで電圧増幅し、電圧増幅後の位相比較信号Dnu(t)と電圧増幅後の第2の位相比較信号Dnd(t)との差分信号を出力する減算回路33を設ける。

(もっと読む)

位相制御回路

【課題】経時変化や温度変化に拘らず、常に最適なタイミングの調整をすることが可能な位相制御回路を実現する。

【解決手段】位相を制御する位相制御回路において、クロック信号を遅延する可変遅延回路と、遅延されたクロック信号がクロック入力端子に入力され、データ信号がデータ入力端子に入力される第1のフリップフロップ回路と、データ信号がクロック入力端子に入力され、遅延されたクロック信号がデータ入力端子に入力される第2のフリップフロップ回路と、第2のフリップフロップ回路の出力信号に基づいて可変遅延回路の遅延量を制御する積分回路とを備える。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)。二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。  (もっと読む)

(もっと読む)

PLL回路におけるアクティブフィルタ。

【課題】 PLL回路の内部のローパスフィルタを構成する回路素子、特に静電容量の値を小さくすることによって、ローパスフィルタをチップに内蔵化可能とする。

【解決手段】 位相比較器の後段に2つのチャージポンプ回路を備えるPLL回路内で用いられるアクティブフィルタが、一方のチャージポンプ回路の出力とアースとの間に接続される第1の回路要素と、他方のチャージポンプ回路の出力とアースとの間に接続される第2の回路要素と、第1、第2の回路要素のそれぞれの両端の電圧を加算する電圧加算器とを備える。

(もっと読む)

信号間の位相、周波数、および到達時間の差分を検出するシステムおよび方法

2つの信号間(118および120)の位相、周波数、および到達時間の差分を検出するシステムおよび方法であって、遅延およびジッタを最小にし、2つの信号(118および120)が実質的に同一であったときでも安定して動作する。システムは、2つのシングルエンド型チャージポンプ(188)、位相周波数検出(PFD)回路(280)を含む。極性判定フリップフロップに供給される基準信号が、同期化される信号に対して先行しているとき第1PFDは安定している。極性判定回路に供給され同期化される信号が、基準信号に対して先行しているとき第2相補PFD回路は安定しているが、反転極性出力を有する。極性選択論理回路(284)は、選択されたPFDの極性判定もしくは非極性判定フリップフロップの活性化の間の遅延によって決定される期間において、最初に活性化されたPFDが極性を制御することを保証する。  (もっと読む)

(もっと読む)

信号処理装置

【課題】 PLL回路において、速やかに正確に発振周波数を目標周波数にロックする。

【解決手段】 入力信号の電圧に応じて出力信号の周波数Fvcoを制御するVCO10と、ローカル発振器12の生成するローカル信号と出力信号とを混合器14により混合した信号を1/N分周するループ内分周器18と、基準信号発振器20の出力する基準信号を1/R分周する基準分周器22と、ループ内分周器18の出力と基準分周器22の出力との位相差に応じた信号を出力する位相比較器30と、低周波成分を通過させてVCO10に与えるループフィルタ50と、Fvcoが目標値FtになるためにVCO10に与えるべき入力信号の電圧Vtとループフィルタ50の出力との差分を出力する減算器66と、位相比較器30の出力また減算器66の出力をループフィルタ50に与えるスイッチ42、44とを備える。

(もっと読む)

位相同期回路

【課題】 入力信号と比較信号との位相比較により位相同期化する位相同期回路に関し、ピークジッタの抑圧を図る。

【解決手段】 入力信号INと比較信号COMPとの位相を比較する位相比較器1と、この位相比較器1の比較出力信号を入力するチャージポンプ2と、このチャージポンプ2の出力信号を入力するループフィルタ3と、このループフィルタ3の出力信号を制御電圧として入力する電圧制御発振器4とを含む位相同期回路に於いて、チャージポンプ3と電圧制御発振器4との間に、制御電圧を、位相比較器1の不感帯の外で位相同期状態となるようにシフトする電圧シフト回路6を設けた。

(もっと読む)

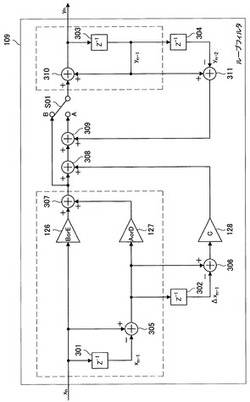

位相同期ループ回路

【課題】 アナログ(特に能動型)ループフィルタのオフセットを自動的に補正して同期クロックまたは周波数の安定性および精度を向上させる。

【解決手段】 このPLL回路は、能動型ループフィルタ30を有する一般的なPLL回路の構成に加えて、周波数比較回路42、DAC制御回路44およびDAC(ディジタル−アナログ変換器)46を備える。オフセット計測モード中は、位相誤差信号生成部(12,14)および周波数誤差信号生成部(18,20)のそれぞれの出力を切り、オフセット計測同期ループ(42,44,46,30,40)において同期を確立させ、そのときのオフセット補正コードEDSを同定して保持する。定常モードでは、DAC制御回路44がオフセット補正コードEDSをDAC46に入力し、DAC46がオフセット補正信号EASをループフィルタ30に与える。

(もっと読む)

PLL回路、PLL回路の位相調整方法

【課題】 Transient Wander成分(入力位相跳躍成分)のみを自動検出し、出力位相を入力位相変動前の位相に立て直す。

【解決手段】 Phase build-out Detector部300は、PLL部100の入力位相を監視し、Transient Wander成分(入力位相跳躍成分)とCycle Wander成分(周期的な位相雑音成分)を同時に検出し、Transient Wander成分のみが検出された場合に、Phase build-out Actuator部200でPLL部のPhase Detector部101、Digital Amp1部102及びDigital Filter部103をリセットし、出力位相を入力位相変動前の位相に立て直す。このとき、同時に検出されるCycle Wander成分に対しては位相の立て直しを行わない。

(もっと読む)

1 - 18 / 18

[ Back to top ]