Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

321 - 330 / 330

電圧制御発振器、ならびにそれを用いたPLL回路および無線通信機器

【課題】 広い周波数可変範囲を得るために複数のバンドを用いた場合、全てのバンドにおいて、良好な位相雑音特性を有し、かつ周波数感度を同程度にすることができる電圧制御発振器を提供すること。

【解決手段】 電圧制御発振器は、インダクタ回路と可変容量回路と高周波スイッチ回路とで構成された並列共振回路と、負性抵抗回路と、周波数制御部と、周波数感度制御部とを備える。周波数制御部は、高周波スイッチ回路が有するスイッチング素子のオンオフを制御することによって、発振周波数のバンドをシフトさせる。周波数感度制御部は、使用するバンドに応じて、制御電圧に対する可変容量回路全体の容量の変化率を調整する。周波数感度制御部は、差動信号の仮想接地点に接続されている。

(もっと読む)

PLL回路およびDLL回路

【課題】 ロックするまでの時間を短縮することができ、初期制御電圧を、回路の用途に応じて変更することができ、製造条件等により、ロックするまでの時間が変動することを防ぐことのできるPLL回路およびDLL回路を提供する。また、ジッタを迅速に低減することのできるDLL回路を提供する。

【解決手段】 PLL回路は、位相比較器3と、チャージポンプ4と、ループフィルタ5と、電圧制御発振器6と、選択信号に応じて制御電圧のレベルを選択する電圧設定回路10と、複数個の選択信号のうち少なくとも1つを出力し、電圧制御発振器6において周波数の増減された出力クロックの、入力クロックに対する逓倍数を検出し、複数個の選択信号の中から最適な選択信号を特定し、電圧設定回路10に出力する設定値判定回路9とを含み、各回路は、待機信号に応じて処理の開始および停止を行なう。

(もっと読む)

アイドル時間ループスタビライザを備えた電荷ポンプPLLに基づいたバーストモード受信器

【課題】

【解決手段】バーストモード受信器は、入来信号を受信するデジタル位相検出器を含む。前記受信器はまた、前記デジタル位相検出器からのパルス信号を受信して、前記入来クロック位相と前記ローカル生成ロック位相を比較して前記電荷ポンプを制御する電荷ポンプと、前記電荷ポンプからの電荷値を受信し、制御信号を生成するループフィルタと、前記制御信号を受信し、回復されたクロックを生成し、前記回復されたクロックをデジタル位相検出器に供給するローカルクロック生成器とを含む。

(もっと読む)

通信用半導体集積回路および無線通信システム

受信用VCO(250)と送信用VCO(240a,240b)と中間周波数用VCO(230)のうち少なくとも1つのVCOが変復調回路と共に1つの半導体チップ上に形成された通信用半導体集積回路において、オンチップのVCOを複数の周波数帯で動作可能に構成し、また該VCOの発振周波数を測定する回路(22)および測定された値を記憶する記憶回路(18)と該記憶回路に記憶されている測定値と外部からの設定値とを比較して上記VCOの使用周波数帯を決定する回路(19)を設けるとともに、該記憶回路の記憶データを外部へ読出しまた外部から書き込むことができるように構成した。  (もっと読む)

(もっと読む)

電圧制御発振器プリセット回路

周波数合成回路は、周波数が或る値にプリセットされ、入力電圧に応じて発振信号を生成する電圧制御発振器(40)を含む。デジタル処理装置(60)は、前記回路が位相ロックループモードで動作することをディスエーブルにすることが出来る。前記回路がディスエーブルにされたら、前記装置は、各々の第1及び第2ループフィルタ入力電圧値に応じて前記発振信号の第1及び第2周波数を決定する。更に、前記装置は、2つの前記周波数、前記周波数分割器の分割比及び前記基準信号から制御値を生成する。前記回路は、前記制御値に応じて前記ループフィルタ入力電圧をプリセット値にプリセットするよう構成されるD/A変換器(70)を更に有する。前記発振器の出力が対応入力プリセット値において発振したら、前記装置(60)は、前記D/A変換器(70)をディスエーブルにし、前記周波数合成回路が位相ロックループモードで動作することをイネーブルにする。  (もっと読む)

(もっと読む)

温度安定化された電圧制御発振器

セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a-310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370,380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b;320a、320bを含んでいる。 (もっと読む)

フェーズロックドループ回路

入力基準信号Urefと入力信号Up,inとの間の位相差ΔΦを検出するための位相比較器であって、Kpが前記位相比較器の位相検出器ゲインである位相比較器と、入力信号Uvco,inに応じて角周波数ωvco,outを有する周期的な出力信号Uvco,outを生成するための電圧制御発振器(VCO)であって、Kvcoが前記電圧制御発振器の電圧制御発振器ゲインである電圧制御発振器(VCO)と、フェーズロックドループ回路の動作中にループゲインK:=Kp×Kvcoが所定の範囲内のままとなるようにフェーズロックドループ回路の動作中に前記位相検出器ゲインKpを制御するようになっているコントローラと、を備えるフェーズロックドループ回路(PLL回路)。  (もっと読む)

(もっと読む)

PLL回路

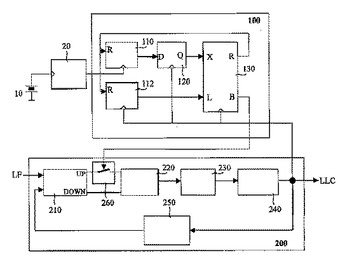

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

半導体集積回路

【課題】 高い周波数範囲と低い周波数範囲との広い範囲においてそれぞれ良好な特性を得ることの可能なPLL回路を提供する。

【解決手段】 制御電圧Vcに応じた周波数で発振動作する電圧制御発振器31を有し、発振信号を分周した比較信号φcompと基準クロックφinとの位相比較を行って、該位相比較の結果を制御電圧Vcにフィードバックさせることで基準クロックφinと発振信号φoutとを同期させるPLL回路において、電圧制御発振器31に、制御電圧Vcを制御電流Icに変換する電圧電流変換回路311と、制御電圧にほとんど依存しない補助電流Isを制御電流Icに付加する補助電流付加回路314と、制御電流Icの大きさに応じた周波数で発振動作する周波数可変発振器162と、制御電圧Vcの値に基づき補助電流付加回路314の動作状態のオン・オフを切り換える制御手段32とを設けた。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

321 - 330 / 330

[ Back to top ]