Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

161 - 180 / 330

発振開始検出回路及び半導体集積回路

【課題】チャージポンプ方式の発振開始検出回路において、プロセスのばらつき等に起因する誤動作を確実に防止する。

【解決手段】この発振開始検出回路は、発振回路によって生成される発振信号を入力して、所定の期間をおいて交互に活性化される第1の制御信号及び第2の制御信号を生成する制御信号生成回路と、第1の制御信号が活性化されているときにオン状態となる少なくとも1つのトランジスタ、及び、第2の制御信号が活性化されているときにオン状態となる少なくとも1つのトランジスタが直列に接続され、第1の電源電位から電荷を移送するトランジスタ列と、トランジスタ列に含まれている複数のトランジスタによって移送される電荷をそれぞれ蓄積する複数のコンデンサと、検出信号を生成する最終段のコンデンサの端子を第2の電源電位にプルダウン又はプルアップする抵抗とを含む。

(もっと読む)

PLL装置、映像同期制御装置及び表示装置

【課題】コストを抑えつつ、外部同期信号と内部同期信号との同期スピードを早くすることができるPLL装置、映像同期制御装置及び表示装置を提供する。

【解決手段】位相差比較部11が外部同期信号とフィードバックされて入力される内部同期信号との位相差を検出する。位相差判定部12は、検出された位相差が所定のしきい値以上であるか否か又は所定のしきい値未満であるか否かを判定する。VCXO18は、位相差判定部12の判定結果に応じて、フィードバックされる出力信号の周波数を可変する。

(もっと読む)

通信装置、及びそのシステムクロック制御方法

【課題】 受信バッファ量を増減させずに、IP網の揺らぎに対処する。

【解決手段】 通信装置であるIP−PBX100は、IP網5からのパケットを一時的に溜める受信バッファ32と、受信バッファに溜まったパケットをシステムクロック信号に同期して順次処理するパケット処理部33と、受信バッファに溜まっているデータ量を検出するバッファデータ量検出部40と、バッファデータ量検出部で検出されたデータ量に応じた周波数のシステムクロック信号を発振するシステムクロック発振部50と、を備えている。

(もっと読む)

局所発振回路

【課題】消費電力を低減できる局所発振回路を提供する。

【解決手段】周波数fsの基準振動信号と周波数fout/(m×n)の分周信号の位相を比較する位相比較器1と、上記両信号の位相のずれに応じた電流IOUTを出力する電荷ポンプ10と、上記出力電流IOUTに応じた制御電圧VCを生成するループフィルタ3と、上記制御電圧VCに応じた発振周波数foutの信号を出力する電圧制御発振器4と、電圧制御発振器4の出力信号を設定周波数に応じた分周値(m×n)で分周して上記分周信号を出力する前置分周器5および可変カウンタ6とを備え、上記発振周波数foutを上記設定周波数に引き込む局所発振回路において、上記電荷ポンプ10は、出力電流IOUTの値を上記設定周波数に応じて切り換える。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

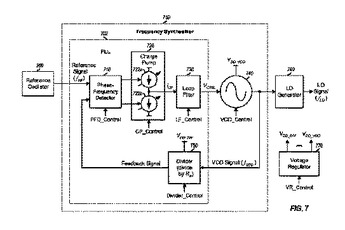

位相ロック・ループにおけるVCOの動的バイアス印加

局部発振器が位相ロック・ループを含む。前記位相ロック・ループは電圧制御発振器(VCO)と新規のVCO制御回路を含む。前記VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。前記命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、前記VCO制御回路は、前記PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次に前記PLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程は前期PLLがロックされたままで行われる。  (もっと読む)

(もっと読む)

クロックトランスファ機能を有するクロック回路及び方法

装置(10)は、移行元クロックと移行先クロックと移行クロックとから選択した出力クロックを出力するマルチプレクサ(20)を含む。さらに、移行元クロックと移行先クロックとの間の位相差を計算する位相差計算モジュール(22)と、複数のクロックを生成するように構成されたクロック生成モジュール(12)とを含む。さらに、複数のクロックのうち1つのクロックを移行トラックとして選択するクロック選択モジュール(14)と、(1)移行元クロックと移行先クロックとの間の位相差に基づき、複数のクロックのうちの1つのクロックを移行クロックとして選択する信号をクロック選択モジュールに出力し、(2)移行元クロックと移行先クロックと移行クロックとのうち1つのクロックを出力クロックとして出力する信号をマルチプレクサに出力する制御回路(16)とを含む。

(もっと読む)

(もっと読む)

位相ロックループ回路

【課題】出力クロック信号の周波数を高精度で制御することができる位相ロックループ回路を提供する。

【解決手段】制御電圧を保持する容量(104)と、リファレンスクロック信号に対するフィードバック信号の位相差を検出する位相検出器(101)と、前記検出された位相差に応じて、前記容量を電源電圧又は基準電位に接続する第1のスイッチ回路(SW1,SW2)と、前記容量の制御電圧に応じた発振周波数の出力クロック信号を生成し、前記出力クロック信号又は前記出力クロック信号に応じた信号を前記フィードバック信号として前記位相検出器に出力する電圧制御発振器(105)と、前記リファレンスクロック信号のエッジから一定期間又は前記出力クロック信号若しくは前記出力クロック信号に応じた信号のエッジから一定期間前記容量を前記基準電位又は前記電源電圧に接続する第2のスイッチ回路(SW3)とを有する位相ロックループ回路が提供される。

(もっと読む)

フェーズロックドループ回路

【課題】入力される水平同期信号に対して、サンプリングクロックの周期の値に制約されることなく、位相誤差量を低減することができるフェーズロックドループ回路を提供する。

【解決手段】入力される水平同期信号(H-sync)は、逓倍PLL回路2から出力される、周期が等しく、1/4周期分づつずれた位相関係の4種の第1〜第4サンプリングクロックによりサンプリング回路でそれぞれサンプリングされ、各サンプリングクロックに位相同期した4種の水平同期出力データが生成され、これらはさらに加算回路6で加算されて加算水平同期出力データが生成された後、位相比較器13に入力され、分周器14で分周されたシステムクロック(第1サンプリングクロック)と位相比較される。

(もっと読む)

データ駆動回路及び遅延固定ループ回路

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず正常に動作可能なデータ駆動回路及び遅延固定ループ回路を提供する。

【解決手段】第1のデータ信号を第2のクロック信号に基づいてサンプリングし、アナログ変換することにより得られた第2のデータ信号を出力するデータ駆動部と、第2のデータ信号の変化開始時点から所定期間内であることを知らせるマスク信号を生成するマスク信号生成部と、第1のクロック信号から第2のクロック信号−第1のクロック信号と第2のクロック信号の間には遅延が存在し、該遅延は前記第1のクロック信号と第2のクロック信号の間の位相差に応じて変化し、位相差に応じる前記遅延の変化は前記マスク信号により遮断される−を生成する遅延固定ループと、を備える。

(もっと読む)

無線通信装置におけるシュプール軽減を伴う発振器信号生成

無線通信装置内で発振器信号を生成する技法を説明する。位相同期ループ(PLL)を使用して選択された周波数チャネルの発振器信号を生成することができる。異なるPLL設定を周波数チャネルのPLL内のブロックに使用することができる。異なるPLL設定は、異なるPLLループ帯域幅、チャージポンプ電流の異なる量、高分周比および低分周比の異なるセットに関連する異なる周波数方程式、異なるプリスケーラ比および/または異なる整数分周比に関連する異なる分周方式、スーパーヘテロダイン受信機または送信機の高側注入または低側注入、ならびに/あるいは発振器などの1つまたは複数の回路ブロックに対する異なる供給電圧に対するものとすることができる。PLL設定の適切なセットを、シュプールに起因する悪影響を軽減できるように周波数チャネル毎に選択することができる。  (もっと読む)

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

【課題】制御信号だけではなく、周波数も制御可能な変調機能を有する発振器、及びその発振器を用いた位相同期ループ回路を提供する。

【解決手段】出力信号の帰還信号と基準信号との位相を比較して、位相差を示す信号を出力する位相検出器1081と、位相検出器1081の出力信号が供給され、位相差をなくすための制御信号を出力するループフィルタ1082と、ループフィルタ1082からの制御信号に基づく周波数で発振する発振器1083とを備え、発振器1083は、制御信号に変調信号を加えることによって周波数を変調する変調手段を備える位相同期ループ回路(PLL回路)。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を上昇させた場合であっても、電圧制御発振回路のコンデンサの充放電電流の増加を抑制する。

【解決手段】コンデンサの充電電圧を入力電圧に応じた周波数で発振させる電圧制御発振回路であって、コンデンサの充電電圧の最低電圧が第1電圧、充電電圧の最高電圧が第1電圧より高い第2電圧となるよう、コンデンサを繰り返し充放電する充放電回路と、入力電圧に応じて第1電圧と第2電圧との差を制御する制御回路と、を備える。

(もっと読む)

遅延回路およびそれを用いた信号発生回路

【課題】 プログラマブル遅延回路のオフセット遅延時間が周囲温度などの周囲条件によって変化するので、このプログラマブル遅延回路を用いた信号発生回路の出力波形信号が不安定になってしまうという課題を解決する。

【解決手段】 プログラマブル遅延回路と遅延回路を直列接続してプログラマブル遅延回路にクロックを入力し、この2つ遅延回路の合計遅延時間が一定になるように前記プログラマブル遅延回路の遅延時間を制御すると共に、このプログラマブル遅延回路の出力を複数のプログラマブル遅延回路に入力するようにした。また、この複数のプログラマブル遅延回路を用いて信号発生回路を構成した。周囲条件が変化しても複数のプログラマブル遅延回路のクロックに対する遅延時間が変動することがない。

(もっと読む)

クロック生成制御回路

【課題】 CPUの負荷を軽減することが可能なクロック生成制御回路を提供する。

【解決手段】 本願発明は、発振回路が出力するクロック信号のパルス数を所定期間カウントし、所定期間及び周波数に応じた設定値と等しくなったときにカウント制御信号の出力レベルを切り替えるカウンタと、所定期間を示すタイミング信号とカウント制御信号とのタイミングの誤差を検出し、誤差検出信号を出力する誤差検出回路と、を備え、周波数制御回路は、誤差検出信号に基づいて制御信号を生成することで、上記課題を解決することができる。

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

直接変換プロセスにおける局部発振器漏洩制御

【課題】直接変換プロセスにおける局部発振器の漏洩制御。

【解決手段】ゼロ中間周波数(IF)受信機あるいは送信機における、局部発振器(LO)周波数を発生するためのシステムおよび方法が与えられる。電圧制御発振器(VCO)から信号が受信される。信号はVCO周波数を有している。VCO周波数は分周された周波数を有している信号を生成するために数値Nによって分周される。VCO周波数を有している信号はそこで、出力周波数を有している出力信号を生成するために、分周された周波数を有している信号と混合される。局部発振器漏洩が減少される。したがって、受信機あるいは送信機は、複数の無線通信帯域およびモードで動作し、そして組み合わせられた規格を満足することが可能である。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

分周回路および分周方法

【課題】50%デューティ・サイクルを有するプログラマブル整数クロック分割の回路お

よび方法。

【解決手段】整数分割値により入力信号の周波数を分割する回路および方法。回路は一般

的に(a)入力信号を受信する第1の複数の直列接続された遅延要素および第1の設定可

能なフィードバック・ネットワークを含む第1周波数分割器、(b)入力信号の逆転を受

信する第2の複数の直列接続された遅延要素および第2の設定可能なフィードバック・ネ

ットワークを含む第2周波数分割器、(c)第1および第2周波数分割器の出力を選択し

および/あるいは組み合わせ、周波数分割出力信号を形成するよう構成される設定可能な

論理、および(d)第1および第2の設定可能なフィードバック・ネットワークおよび設

定可能な論理を選択可能な形で設定するよう構成されるプログラマブル回路、を含む。

(もっと読む)

161 - 180 / 330

[ Back to top ]