Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

141 - 160 / 330

張り出し無線装置、信号伝送速度の判別方法及び判別プログラム

【課題】変復調装置からベースバンド信号の伝送を受けて張り出し無線装置が動作する信号伝送系における信号の伝送速度を判別する。

【解決手段】変復調装置からベースバンド信号の伝送を受けて動作する張り出し無線装置であって、前記ベースバンド信号を基にしてパラレル信号およびクロック信号を生成するインタフェース部と、前記インタフェース部が生成する前記クロック信号と比較するための規定値の異なる信号を順次出力する制御部と、前記インタフェース部が生成する前記クロック信号と、前記制御部が出力する規定値の信号とが一致するか否かを検出し、前記両信号が一致した際に一致信号を出力するクロック回路とを有する。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

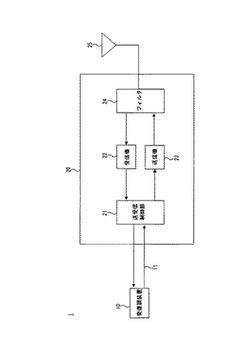

アナログ位相拘束ループ装置

【課題】単一で安定し信頼性のあるアナログのタイプIII位相拘束ループ装置を提供する。

【解決手段】位相検出器2は入力基準信号4及び出力信号6の位相差を表すエラー信号12を発生する。選択器14は第1帯域幅パラメータ値の選択時にエラー信号を第1信号経路8に供給し、第2帯域幅パラメータ値の選択時にエラー信号を第2信号経路10に供給する。第1信号経路はエラー信号を積分する第1積分器16と、その積分信号を積分してエラー電圧信号を発生する第2積分器18と、このエラー電圧信号に応答して第1信号経路出力信号を発生する電圧制御発振器20とを具えている。第2信号経路も同様な積分器22,24及び電圧制御発振器26を具えている。選択器28は第1帯域幅パラメータ値の選択時にVCO20の出力を選択し、第2帯域幅パラメータ値の選択時にVCO26の出力を選択する。選択器28の出力信号が位相検出器2に帰還する。

(もっと読む)

容量切り換え回路、VCO、およびPLL回路

【課題】 PLLおよびVCOの発振特性を改善できる容量切り換え回路を提供する。

【解決手段】 端子P1と端子P2との間に、コンデンサC1k(k=0〜n)と、FET(Q1k)と、コンデンサC2kとを直列接続する。FET(Q1k)のソースにFET(Q3k)のドレインを接続する。FET(Q1k)のドレインにFET(Q4k)のドレインを接続する。FET(Q3k、Q4k)のゲートは互いに接続し、それらのソースも互いに接続する。FET(Q1k)のゲートに、このFET(Q1k)をオンオフ制御する制御データbkを供給する。FET(Q4k)のソースに、少なくともFET(Q1k)がオフのときには、FET(Q3k、Q4k)をオフにするソースバイアス電圧VSkを供給する。

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】 広い範囲にわたって良好な特性のチャージポンプ電流の得られるチャージポンプ回路を提供する。

【解決手段】 第1のチャージポンプ部14Aに、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号が供給する。残るチャージポンプ部14B、14Cには、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号と、スイッチ回路SW1〜SW4をオフにする電位とが、スイッチ回路SWA〜SWDを通じて供給される。必要とするチャージポンプ電流に大きさに対応して、スイッチ回路SW11BA〜SW14Cを制御するとともに、定電流源Q1、Q2の出力電流の大きさを変更することにより、出力端子T3に、必要とする大きさのチャージポンプ電流を得る。

(もっと読む)

PLL回路およびそのIC

【課題】 PLL回路としての動作を中断することなく適切な発振信号を出力できるようにする。

【解決手段】 測定時、第1の制御電圧をVCO31に供給する電圧供給回路302と、VCO31の発振周波数を測定する周波数測定回路303とを設ける。使用時、VCO31に供給される第2の制御電圧の大きさを測定する電圧測定回路304を設ける。測定時、電圧供給回路302および周波数測定回路303により、第1の制御電圧とVCO31の発振周波数の変化の割り合いとの関係を示すデータテーブルを作成する。使用時、データテーブルを参照して、電圧測定回路の測定した第2の制御電圧を発振周波数の変化の割り合い示す制御感度に変換する。可変分周回路32の分周比Nにかかわらずオープンループ時の伝達関数が一定となるように、変換結果の制御感度によりチャージポンプ回路34のチャージポンプ電流の大きさを制御する。

(もっと読む)

PLL回路

【課題】PLLのロック時間を高速化する。

【解決手段】PLLを構成するローパスフィルタ107に対して回路の最大電圧を与えて充電する。その過程でクロック計数カウンタ102が基準クロック10の一周期におけるVCO出力クロックの数をカウントし、所定の2時点でのカウント値により基準クロックとVCO出力クロック27に対する分周クロックとのロックポイントにおける位相差を推定する。この推定は、演算処理回路105において、VCO個体のカタログデータに基づいて行ない、カウンタロード値24を算出し、分周カウンタ109はこれを分周信号28、位相比較器106は該推定位相差とし、充電後にローパスフィルタに供給する。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

クロック再生回路

【課題】短いビット同期時間、クロックワンダー追随性能、高い高周波ジッタ耐性、を同時に満たすクロック再生回路を提供する。

【解決手段】入力データ信号101と再生クロック102との位相差を検出する位相差検出回路103、位相差検出回路103の出力を平均化する平均化回路104、位相差検出回路103の出力をサンプル/ホールドするリセット付サンプル/ホールド回路105、平均化回路104の出力の積分値とリセット付サンプル/ホールド回路105の出力値との和に相当する位相の再生クロック102を生成する再生クロック生成回路106を備える。リセット付サンプル/ホールド回路105は、バースト伝送開始信号110を受けて位相差検出回路103の出力をサンプル/ホールドし、バースト伝送終了信号111を受けてホールドしている値を初期値にリセットする。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

PLL回路

【課題】複数のVCOを切り替えて使用するPLL回路において、VCOの位相雑音を最適化することである。

【解決手段】PLL回路11の複数のVCO12−1〜12−nの内の1つの選択は、VCO選択データにより行われ、キャパシタの選択はVSBデータにより行われる。バイアス電流設定回路25は、VCO選択データとVSBデータと制御電圧のデジタル変換値VTDをデコードして、予め定めたバイアス設定値を可変電流源I1に出力する。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

低域ろ波回路

【課題】容量素子の小型化を図る低域ろ波回路(ループフィルタ)において、容量素子としてMOS容量を使用した場合の電圧依存によるPLL応答特性のばらつきと、MOS容量として薄膜ゲートトランジスタを使用した場合のゲートリーク電流によるジッタ特性の劣化を抑制する。

【解決手段】ループフィルタは、第1の容量素子31と、この容量素子31に直列に接続された抵抗素子32及び第2の容量素子33とを備える。前記第1の容量素子31の一端に接続された第1の入力端IN1に第1の電流(Ip/10)を与え、前記第1の容量素子31の他端に接続された第2の入力端IN2に第2の電流(Ip/10)を与えることにより、第1の容量素子31の小型化が図られる。前記抵抗素子32に直列に接続された可変電圧電源35は、電圧制御端子36から、第1の容量素子31の両端の印加電圧が一定になるように制御される。

(もっと読む)

リアルタイムクロック回路のバックアップ電源回路および半導体装置

【課題】二次電池を過充電することなく、負荷回路の正確な消費電流の測定を可能にする。

【解決手段】リアルタイムクロック回路11のバックアップ電源回路20において、主電源Vinにより充電されるバックアップ電源20と、主電源Vinと、リアルタイムクロック回路11の電源端子間に介挿された第1スイッチ手段SW1と、バックアップ電源20と、リアルタイムクロック回路11の電源端子間に介挿された第2スイッチ手段SW2と、主電源Vinの電圧を検出し、該電圧が第1検出電圧以下の場合には第1スイッチ手段SW1をオフする第1電圧検出回路12と、主電源Vinの電圧を検出し、該電圧が第2検出電圧以上の場合には前記第2スイッチ手段SW2をオフする第2電圧検出回路13を備える。

(もっと読む)

起動制御回路付き水晶発振回路および位相同期回路

【課題】 水晶発振回路が定常発振に達するまでの起動時間を短くすることができる起動制御回路付き水晶発振回路、水晶発振回路の起動時間を短くすることで間欠動作の比率を大きくし、低消費電力化に寄与する位相同期回路を実現する。

る。

【解決手段】 水晶振動子と負性抵抗回路を備えた水晶発振回路の起動制御を行う起動制御回路を含み、一定の発振周波数の信号を出力させる起動制御回路付き水晶発振回路であって、水晶発振回路は、水晶振動子を励振する励振信号を外部から入力するための信号入力端子を備え、起動制御回路は、発振周波数またはそれに近い周波数を有する励振信号を生成し、水晶発振回路の起動時に励振信号を励振信号入力端子に入力し、水晶発振回路の発振周波数が安定する前に励振信号の入力を停止する構成である。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

PONシステムの局側装置、受信方法及びクロックデータ再生回路

【課題】 周波数変化を伴う入力信号に対しても高速かつ高精度に追従することができるクロックデータ再生回路を提供する。

【解決手段】 本発明のクロックデータ再生回路は、制御電圧Vcに対応する発振周波数でクロック信号Scを出力する電圧制御型発振器55と、入力信号(受信データ)RDとクロック信号Scとの位相差に対応してアップ信号Su又はダウン信号Sdを出力する位相比較器52と、アップ信号Su又はダウン信号Sdに対応するチャージポンプ電流Ipを生成するチャージポンプ53と、チャージポンプ電流Ipに対応する制御電圧Vcを生成するループフィルタ54と、位相差に基づいてチャージポンプ53又はループフィルタ54若しくはこれらの双方の動作パラメータを切り替える制御部58とを備えている。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

カレントミラー回路及びチャージポンプ回路

【課題】回路サイズを大きくすることなく、雑音を小さくすることができるカレントミラー回路及びチャージポンプ回路を得ることを目的とする。

【解決手段】カレントミラー回路1,2におけるトランジスタ12,22とトランジスタ13,23の間にスイッチ14,24を挿入し、トランジスタ13,23により入出力端子5から電流が出力される期間中又は入出力端子5から電流が引き込まれる期間中、そのスイッチ14,24がOFF(開状態)に制御されるように構成する。これにより、トランジスタの回路サイズを大きくすることなく、入出力端子5から出力される雑音を小さくすることができる。

(もっと読む)

141 - 160 / 330

[ Back to top ]