Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

101 - 120 / 330

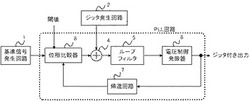

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

原子発振器

【課題】安価な原子発振器を構成する。

【解決手段】原子共鳴器10が発生する共鳴信号54を増幅する増幅器18と、所定の周波数の低周波信号LWVを出力する低周波位相変調信号発生器21と、共鳴信号54と低周波信号LWVとに基づき制御電圧VCを出力する位相弁別器20と、制御電圧VCに基づき原子共鳴器10が正常に動作しているか否かを示すアラーム信号ALMを出力するアラーム回路30と、所定の電圧VDを発生する電圧発生部32と、アラーム信号ALMに基づき原子共鳴器10が正常に動作している場合は制御電圧VCを出力し、正常に動作していない場合は所定の電圧VDを出力するスイッチ回路34と、スイッチ回路34の出力に基づき出力信号OUTの周波数が制御される電圧制御水晶発振器23と、出力信号OUTと低周波信号LWVとに基づき逓倍及び合成したマイクロ波MWVを出力する周波数逓倍合成変調部22と、を含む原子発振器1。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

半導体装置、携帯通信端末、ICカード及びマイクロコンピュータ

【課題】搬送波からクロック信号の抽出が出来ないときも内部動作が停止することなく通信動作を行うことができる非接触インタフェース技術を提供する。

【解決手段】変調された搬送波をアンテナ(10)から入力し、入力した搬送波から抽出したクロック信号(CLKREF)に基づいて内部クロック信号(CLKPLL)を生成し、内部クロック信号に同期動作する半導体装置(11)において、抽出されたクロック信号を入力して内部クロック信号を生成するPLL回路(13)に、前記搬送波から抽出されたクロック信号が離散的に途切れた場合に内部クロック信号をその直前の周波数に維持させる電圧制御発振機能を搭載する。これにより、前記搬送波から抽出されるクロック信号が途切れてもデコードやバスインタフェースなどの内部のデータ処理を継続することができる。

(もっと読む)

デジタルクロック・データ復元機およびこれを適用したトランシーバー

本発明は、デジタルフィルタ回路(digital filter)とデジタル制御発振器(DCO;digitally controlled oscillator)を用いて回路全体をデジタル回路化したクロック・データ復元機に関するものであり、本発明に係るデジタル制御発振器は、複数個のインバータチェーンを備えており、それぞれのインバータに電源電流を供給する電源電圧とインバータの間に可変抵抗スイッチングマトリックスを構成して供給電源を変化させ、発振周波数をチューニングする。

ここで、可変抵抗スイッチングマトリックスは、PMOSトランジスタ配列を用いて具現化するものの、低いレベルでの周波数チューニングステップと高いレベルでの周波数チューニングステップを互いに均等化するために、スイッチングマトリックスの列と列の間に垂直抵抗を追加挿入している。また、ジッタ発生問題を解消するために、第1シグマデルタモジュレータを用いてディザリング回路を具現化しており、セグメントサーモメーター方式を適用して少ない個数のルーティングラインでデジタル制御発振器をチューニングしている。  (もっと読む)

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

温度補償型水晶発振器の温度補償値設定方法

【課題】 各温度におけるD/A変換器の温度補償値を短時間で取得できる温度補償型水晶発振器の温度補償値設定方法を提供する。

【解決手段】 PC23が、PLL回路21からロック信号が入力されるまでは、PLL回路21からの制御電圧出力を選択してVCXO16に入力するようSW15を制御し、PLL回路21からロック信号を入力すると、A/D変換器12からの検出温度の値とPLL回路21からの制御電圧出力についてバッファ18、A/D変換器19により得られた電圧値を記憶すると共に、CPU13の内部メモリにロック状態の検出温度の値と制御電圧の値として設定して、D/A変換器14への温度補償値を取得する温度補償型水晶発振器の温度補償値設定方法である。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

基準信号発生装置

【課題】起動特性に基づく安定的な遷移曲線に対して変動が生じても、高精度に自走DAC値を推定できる基準信号発生装置を実現する。

【解決手段】制御部10は、自走DAC値の推定タイミングtNになると、当該タイミングtNから特定時間に亘って遡る区間MNを基準区間として、推定曲線201を算出する。制御部10は、基準区間MNと異なる補正区間LMの同期DAC値を取得し、推定曲線201から得られる推定同期DAC値との差分値ΔDを算出する。制御部10は、差分値ΔDに基づいて補正値Cdを算出し、各同期DAC値を補正値Cdで補正することで補正同期DAC値を取得する。制御部10は、この補正同期DAC値を含む同期DAC値から新たな推定曲線を算出し、自走DAC値を推定する。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

DLL回路、PLL回路

【課題】ロックイン時間を短縮しつつチャージポンプ回路の誤差電流に起因するジッタを低減する。

【解決手段】チャージポンプ回路30は、位相比較回路20による比較結果(充電信号UP0,放電信号DN0)に応答して正または負の出力電流Ioutを出力する。電流制御回路11は、遅延クロックCK(n)の遷移エッジを含む有効期間中に遅延クロックCK(1)の遷移エッジが発生することを検出し、その検出結果に応じてチャージポンプ回路30の出力電流Ioutの電流量を制御する。

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO・電流切替回路15は、外部から与えられる分周データに基づいて、複数のVCO22a〜22nの内の1つを選択するVCO選択信号を出力する。また、VCOを切り替える際に、可変チャージポンプ20の出力電流を通常(ロック時)より大きな値に変更する切替信号を出力する。VCO・電流切替回路15は、VCOの切り替えが終了したなら、可変チャージポンプ20の出力電流を通常時の小さい値に切り替える切替信号を出力する。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

チャージポンプ回路、及びクロック生成器

【課題】チャージポンプ容量の充電電流と放電電流とが等しくなるように補正する。

【解決手段】外部から充電制御信号を受けて制御電圧を増加させ、外部から放電制御信号を受けて制御電圧を減少させる第1のモードと、補正動作を行う第2のモードとを有したチャージポンプ回路であって、第1のモードにおいて、充電制御信号に応じて第1のノードを通して充電電流を流し出す充電部と、放電制御信号に応じて第2のノードを通して放電電流を吸い込む放電部と、第2のモードにおいて、第1のノードと第2のノードとに一端が接続される検出抵抗と、検出抵抗の他端に参照電圧を供給する電圧源と、充電部が検出抵抗の一端へ充電電流を流し出し放電部が検出抵抗の一端から放電電流を吸い込んだ状態における検出抵抗の一端の電圧と参照電圧との差に基づいて、充電部が流し出す充電電流と放電部が吸い込む放電電流とが等しくなるように補正する補正部とを備える。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部と、を有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記生成部から出力された前記制御電圧と前記参照電圧とを比較し、前記生成部から出力される制御電圧が前記参照電圧に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

周波数シンセサイザ及び無線送信装置

【課題】VCOの出力帯域を選択設定可能な周波数シンセサイザにおける消費電力を低減すること。

【解決手段】互いに並列に接続されたミキサ111と分周器112とを有する周波数変換回路110を設け、VCO101の周波数帯域選択時に分周器112を用いることにより、VCO101の周波数帯域選択時の位相比較器102の最高動作周波数を低くすることができ、消費電力を低減できる。また、送信時にはミキサ111を用いることにより、送信時のループゲインを下げずに済む。

(もっと読む)

デジタル放送受信装置、時刻情報生成回路、及びデジタル放送受信方法。

【課題】

従来の複数PCRに同期したSTCクロック再生方法は、複数チャンネル毎にPCRとの差分情報を参照するVCXOを独立に備えて複数のマスタクロックを生成し、これらマスタクロックを互いに独立に使用してSTCクロックを再生するPLLを有する構成となっており、高価な回路構成となっていた。

【解決手段】

複数PCRに同期させるために得られた各差分情報を一定周期で切り替えて、一組のVCXOに供給し、時分割にマスタクロックを生成し、各STCクロックを再生するPLLを機能させる。上記、切り替え時に未選択側の差分情報が必要なPLLは出力クロックの変動を抑えるためにPLL内部の位相比較をHoldさせることにより、安価で安定度の良い回路構成を可能にする。

(もっと読む)

PLL回路

【課題】ノイズの抑圧を効果的に行うことができるPLL回路を提供する。

【解決手段】位相比較器10と、チャージポンプ回路20と、ループフィルタ30と、VCO40と、N分周器50とを備える。チャージポンプ回路20の一実施形態は、アップ信号UP1によりスイッチ22をオンした後、アップ信号UP1を遅延させたアップ信号UP2により再度スイッチ22をオンする。同様に、ダウン信号DN1によりスイッチ23をオンした後、ダウン信号DN1を遅延させたダウン信号DN2により再度スイッチ23をオンする。

(もっと読む)

基準信号発生装置

【課題】温度に関連する各種の周波数変動要素の影響を抑制して、高精度な基準周波数信号を発生する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、自走用制御電圧信号を推定して記憶する。制御部10は、温度センサ16からの温度検出信号に基づいて電圧制御発振器14の温度を観測して記憶する。制御部10は、ホールドオーバを検出すると、その時点での温度を検出するとともに(S101)、記憶した過去の温度を含み温度の時間変化率を算出する(S102)。制御部10は、予め設定した制御補正値算出用係数を読み出し(S103)、当該係数により設定される演算式に、検出した温度および算出した温度の時間変化率を代入して、制御補正値を算出する(S104)。制御部10は、この制御補正値に基づいて自走用制御電圧信号を補正し、電圧制御発振器14へ与える。

(もっと読む)

101 - 120 / 330

[ Back to top ]