Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

21 - 40 / 330

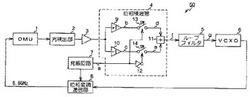

ルビジウム原子発振器

【課題】回路構成を単純化して部品コストを低減すると共に、回路の小型化を実現したルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器50は、ルビジウム原子の共振周波数により励振する光マイクロ波ユニット(OMU)1と、OMU1を透過した光の強度を検出する光検出部2と、Amp3に現れる周波数誤差信号の位相を検波する位相検波器4と、位相検波器4の出力信号を積分するループフィルタ5と、ループフィルタ5の電圧に基づいて所定の周波数を発振する電圧制御水晶発振器(VCXO)6と、マイクロ波の位相を低周波により変調する発振回路7と、VCXO6の発振信号をマイクロ波に逓倍する位相変調逓倍部8と、を備えて構成されている。

(もっと読む)

PLL回路

【課題】PLL回路の引き込時間を短縮する。

【解決手段】位相比較器10は、PLL回路100への入力クロックの位相と、PLL回路100の出力から分周器40を介して帰還される帰還クロックの位相とを比較し、その位相差に応じた信号を生成する。LPF20は、位相比較器10の出力信号に応じた直流電圧を生成する。電圧制御発振器30は、LPF20により生成された電圧に応じた周波数のクロックを出力する。サイクルスリップ予測回路50は、位相比較器10により生成される信号を監視し、サイクルスリップの発生を予測する。サイクルスリップ予測回路50によりサイクルスリップの発生が予測されたとき、入力クロックの位相、帰還クロックの位相および電圧制御発振器に入力される電圧のいずれかが調整される。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、送信回路100と、受信回路170と、制御部110と、記憶部130とを含む。記憶部130は、送信回路用キャリブレーションパラメーターと受信回路用キャリブレーションパラメーターとの相関を表す情報を記憶する。制御部110は、送信回路100の送信状態の検出結果に基づいて送信回路用キャリブレーションパラメーターを設定し、設定された送信回路用キャリブレーションパラメーターと相関を表す情報とに基づいて受信回路用キャリブレーションパラメーターを設定する。送信回路100は、送信回路用キャリブレーションパラメーターに基づく送信処理を行う。受信回路170は、受信回路用キャリブレーションパラメーターに基づく受信処理を行う。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

無線通信装置

【課題】周波数シンセサイザによる周波数信号を用いる無線通信装置の消費電力を低減する。

【解決手段】受信部が、受信した無線信号に基づく信号と周波数信号とを混合する第1ミキサと、当該第1ミキサの出力とローカル信号とを混合する第2ミキサと、当該第2ミキサの出力を復調して復調信号を生成する復調段とを含み、周波数シンセサイザが、制御入力電圧の変動に応じた周波数の周波数信号を生成するVCOと、当該VCOの出力周波数信号を分周して得られた信号と基準クロック信号との位相差に応じた電圧を制御入力電圧とするフィードバック回路と、からなり、当該VCOは、バイアス電流が大となるほど高い周波数で動作可能となる可変周波数発振器であって、当該バイアス電流が当該モード指定に応じて制御される無線通信装置。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

出力信号制御装置、出力信号制御方法および出力信号制御プログラム

【課題】入力信号を遅延させて出力信号を作成する際に、入力信号の変動が原因で出力信号の遅延が規定値内に納まらない場合であっても、この出力信号によるエラーの発生の抑制が可能な出力信号制御装置、方法およびプログラムを得ること。

【解決手段】位相差許容範囲判別手段12は、位相差測定手段11が測定した出力信号の位相差がこの出力信号を入力する回路で許容範囲内であるかを判別する。出力制御手段13は、許容範囲内でないと判別する状態で出力信号の出力を遮断し、許容範囲内となった段階で出力を開始する。

(もっと読む)

半導体装置

【課題】クロック周波数の設定を変えた場合でも電源や温度などに変動があっても、高精度なクロック信号を生成する。

【解決手段】周波数電圧変換回路13は、スイッチSW1,SW2から構成されるスイッチ部、静電容量素子C,C10〜C13、およびスイッチCSW0〜CSW3から構成されている。静電容量素子C10〜C13は、容量の絶対値が異なるもので構成され、設計者が意図する周波数範囲をカバーするよう設ける。静電容量値は、たとえば、2の重み付けがされている静電容量素子C11〜C13は、たとえば、4ビットの周波数調整制御信号SELC0〜SELC3に基づいて、スイッチCSW0〜CSW3が選択し、周波数の切り替えを行う。

(もっと読む)

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

アクチュエータの駆動装置ならびにそれを用いる平行移動機構、干渉計および分光器

【課題】被駆動部材となる可動部とそれを駆動する駆動部とを備えて成るアクチュエータをPLL回路で駆動し、機械共振駆動を行わせる駆動装置において、短時間でかつ確実な位相引き込み動作を可能にし、さらに回路規模の増大やコストアップを抑える。

【解決手段】PLL回路のループフィルタ部14aを、位相比較器13の位相比較信号Vpdを平滑化してVCO11へ制御電圧Vcとして与えるLPFとしての機能を実現する積分回路21に、基準電圧源22とリセット手段としての短絡スイッチ23とを設ける。したがって、前記制御電圧Vcは、積分動作に伴い、基準電圧Vrefから共振周波数の目標電圧付近に滑らかに移行するので、オーバーシュートやリンギングの発生がなく、短時間でかつ確実な位相引き込み動作(位相ロックイン)を行うことができる。また、PLLループの外部に、制御信号を掃引するための特別な構成を設ける必要もない。

(もっと読む)

21 - 40 / 330

[ Back to top ]