Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

121 - 140 / 330

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

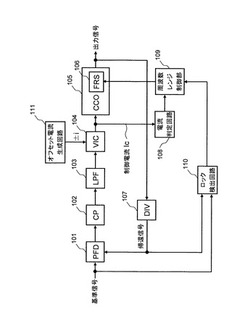

PLL回路

【課題】ループ帯域幅に変動が起こっても、容易に対応できるPLL回路を提供する。

【解決手段】位相比較回路は、帰還信号と外部より入力される基準信号との位相差を検出してチャージポンプに出力し、さらに帰還信号のみが入力した場合、帰還信号に同期したUP信号のみを出力するUPパルス制御を備えておりチャージポンプにその出力を入力し、チャージポンプの出力が入力したループフィルタの出力は電圧制御発振回路に入力し、さらにループフィルタの出力は比較回路の入力に接続され、比較回路の他の入力には基準電圧が入力し、基準電圧は電圧制御発振回路に入力し、比較回路の出力はラッチ回路に接続され、さらに基準信号が入力されたカウンタ回路の出力がラッチ回路に入力し、チャージポンプはラッチされたカウンタ回路によりカウントされた値に従って電流源を選択する選択手段を備えている。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切り替え時の周波数変動を低減することによって、高速に周波数切り替えが可能なPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザは、基準発振器と、分周器と、位相比較器と、チャージポンプと、ループフィルタと、VCOとを備えている。ループフィルタは、チャージポンプとVCOとの間に互いに並列に設けられた第1経路および第2経路と、第1経路上に設けられた第1スイッチと、第2経路上に設けられた第2スイッチとを含み、第1スイッチおよび第2スイッチの双方がオフ状態であるとしたときに、それぞれの寄生容量が互いに同じであり、第1経路および第2経路それぞれの抵抗値が互いに異なり、第1スイッチおよび第2スイッチの一方がオン状態であるとき、他方がオフ状態となる。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。抵抗回路や容量回路をスイッチングすることなく、自然角周波数ωnとダンピングファクタζをそれぞれ自由に変えることが可能な、新しい位相同期回路が実現される。使用用途に合わせた位相同期回路の選択の幅を広げることができる。

(もっと読む)

DLL回路

【課題】広い周波数帯域で動作するDLL回路を提供する。

【解決手段】入力クロック信号CLKの周波数を検出する周波数検出回路12が設けられ、当該検出結果に応じたデータはレジスタ13に格納される。レジスタ13は当該検出結果に応じたモード切替信号MODEをVCDL回路11に出力する。入力クロック信号CLKの周波数が所定値より小さい場合は、各遅延素子の遅延量が大きくなり、入力クロック信号CLKの周波数が所定値以上の場合は、各遅延素子の遅延量が小さくなるように構成されている。具体的には、VCDL回路11において、各遅延素子の出力端子にスイッチと容量素子を付加し、モード切替信号MODEに応じてスイッチをオン・オフさせることで、容量素子を各遅延素子の出力端子に接続するか否かを切り替えるという構成が採用されている。

(もっと読む)

PLL回路並びに無線通信装置

【課題】発振器毎の変換利得を吸収し、いずれの発振器を用いても発振周波数を安定して収束させることができる、優れたPLL回路を提供する。

【解決手段】ビット・シフト量演算部は、ディジタル制御発振器の変換利得の概算値と、位相比較器の出力の下限値及び上限値に相当するデータ変換部の出力の下限値及び上限値に基づいて、当該PLLを収束させるために必要なビット・シフト量nを決定する。ビット・シフト回路は、ディジタル制御発振器へのディジタル制御データに対し、当該帰還ループを収束させるために必要となるビット・シフト量を与える。

(もっと読む)

基準信号発生装置

【課題】外部環境による精度低下への影響を低下させ、且つ、ユーザに必要以上の手間を掛けることなく、安定して高精度な基準周波数信号を継続的に出力し続ける。

【解決手段】制御部10は、位相差の平均が、監視閾値未満であるかどうかによって、較正の有無を判定する。ここで、監視閾値は、当該基準周波数信号発生装置1が搭載される通信機器に求められる精度の仕様を満たすとともに、この仕様の限界に対して所定の余裕を持てるような値に設定されている。監視閾値未満の場合、制御部10は、自身で生成した維持用制御電圧信号を電圧制御発振器14へ与え、監視閾値に達する場合、ループフィルタ12からの制御電圧信号を電圧制御発振器14に与え、電圧制御発振器14はこの制御電圧信号に基づいて較正を行う。

(もっと読む)

チャージポンプ回路

【課題】位相比較周波数が高い場合にも、フリッカ雑音の影響を小さくし、チャージポンプ回路の出力の雑音密度のオフセット周波数依存を小さくする。

【解決手段】PLL回路に設けられ、位相比較回路が出力する制御信号に従って電流吐き出し用の電流源と電流吸い込み用の電流源をオン・オフ制御するチャージポンプ回路において、蓄積期間信号に従って前記電流源からの電荷を蓄積し、出力期間信号に従って蓄積された電荷を出力する電荷蓄積・放出回路を備え、蓄積期間信号は、位相比較回路からの制御信号の複数周期に跨った期間を持つように設定される。

(もっと読む)

PLL方式発振回路、ポーラ送信回路及び通信機器

【課題】VCO101の変調感度のばらつきを低減し、高速、高精度に所望の出力振幅を得ることができるPLL方式発振回路を提供する。

【解決手段】振幅検出器103は、VCO101の出力振幅を検出する。振幅制御部105は、振幅検出器103が検出したVCO101の出力振幅が所望の振幅になるように可変電流源109の電流値を制御する。LPF108は、振幅制御部105と可変電流源109との間に接続される。スイッチ107は、LPF108を振幅制御部105と可変電流源109との間に接続するか否かを切り替える。振幅制御部105は、LPF108又は切り替えスイッチ107のいずれか一方を介して、可変電流源109と接続される。

(もっと読む)

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

位相同期ループ回路

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】C結型の可変容量回路と直結型の可変容量回路とを上手く混在させて構成し、発振周波数の線形性及び可変範囲のバランスがとれた電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路110、C結型可変容量回路120及び140、直結型可変容量回路130、及び負性抵抗回路160と、基準電位Vref1及びVref2を生成する基準電位発生部180とを備える。各可変容量回路120、130、及び140の可変容量素子121、122、131、132、141、及び142のバックゲート端子には、発振周波数をフィードバック制御するための制御電位Vtが印加される。C結型可変容量回路120及び140の可変容量素子121、122、141及び142のゲート端子には、基準電位Vref1及びVref2がそれぞれ印加される。

(もっと読む)

位相同期回路および集積回路

【課題】 位相同期回路の位相比較回路が動作を停止した後に再開する場合に、発振回路の出力信号が基準信号の位相に同期するのにかかる時間を短縮する。

【解決手段】入力される基準信号および比較信号の位相差を示す信号を出力する位相比較回路と、第1のコンデンサを含み、前記位相比較回路の出力信号を積分する積分回路と、前記積分回路の出力信号の電圧値に応じた周波数を有する信号を出力する発振回路と、前記発振回路の出力信号を分周し、前記比較信号として前記位相比較回路に入力する分周回路と、前記第1のコンデンサと並列に接続される、スイッチ回路および第2のコンデンサの直列回路と、を有し、前記スイッチ回路は、前記位相比較回路の動作が停止した後にオンとなり、前記位相比較回路の動作が再開した後にオフとなる。

(もっと読む)

PLL回路

【課題】 PLL回路の出力周波数毎の閉ループ伝達特性を一定に保ち、所望の周波数を出力するのに必要な電圧制御発振器の制御電圧要求が大きい場合でも、電圧制御発振器を制御できるPLL回路を得る。

【解決手段】 PLL回路内にループフィルタ切替器6aを設け、ループフィルタ切替器6aは、その入力部に接続されたスイッチ8aと出力部に接続されたスイッチ8bとで、ループフィルタを選択的に切替え、各ループフィルタがオペアンプを用いた能動回路から構成される。

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

121 - 140 / 330

[ Back to top ]