Fターム[5J106DD08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | スイッチ (729)

Fターム[5J106DD08]の下位に属するFターム

セレクタ (399)

Fターム[5J106DD08]に分類される特許

41 - 60 / 330

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

PLL回路

【課題】出力クロック信号のロングタームジッタを抑制するPLL回路を提供する。

【解決手段】位相比較器、チャージポンプ回路、ループフィルタ、及び電圧制御発振器を有するPLL回路において、基準クロック信号と帰還クロック信号との位相差が所定の閾値より大きい場合には、位相差の単位量当たりに対する変化を小さくして位相差に応じた出力電流を出力し、位相差が所定の閾値以下である場合には、位相差の単位量当たりに対する変化を大きくして位相差に応じた出力電流を出力するようにして、ロック後のループ帯域を広げることができるようにする。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号の振幅レベルの適正範囲内を特定し、その適正範囲の内外に応じて電圧制御発振器に制御電圧を供給するPLL装置において、温度により動作が不安定になることを防ぐこと。

【解決手段】制御電圧出力部に供給される信号を位相比較部と予備信号供給部との間で切り替える切り替え部と、前記基準周波数信号の信号路とアースとの間に設けられ、当該基準周波数信号の振幅レベルを規制するために、ダイオードを逆並列に接続した保護回路と、この保護回路の雰囲気温度を検出する温度検出部と、外部からの前記基準周波数信号の振幅レベルを検出するレベル検出部と、を備えるようにPLL装置を構成し、検出温度に応じて前記切り替えの基準となるしきい値を設定し、前記ダイオードの温度特性により前記振幅レベルが変わることに対応する。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

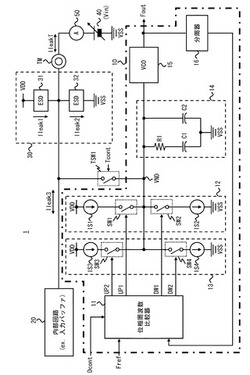

基準周波数発生装置

【課題】長時間にわたって基準周波数周波数の周波数安定度を維持可能で、かつ安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置1は、ルビジウム発振器11と、ルビジウム発振器11より周波数安定度が低い水晶発振器21と、判定部42と、切替スイッチ51a〜51fと、を備える。判定部42は、ルビジウム発振器11が正常な出力信号を出力している正常状態か、正常な出力信号を出力していない故障状態か、を判定する。切替スイッチ51c,51dは、ルビジウム発振器11が正常状態であると判定部42が判定しているときは、第1PLL回路を構成するように設定を行い、ルビジウム発振器11が故障状態であると判定部42が判定しているときは、第2PLL回路を構成するように設定を行う。

(もっと読む)

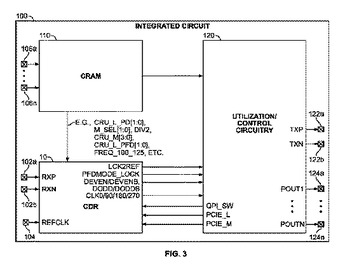

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

信号処理装置

【課題】 外部からの基準信号の周波数変化が安定している状態であるかどうかをユーザが容易に判別可能とする。

【解決手段】 外部機器から供給された基準信号を入力する入力手段と、前記入力手段により入力された基準信号とクロックとの位相差を検出する位相検出手段と、前記位相検出手段の出力に応じた周波数の前記クロックを発生する発生手段と、前記位相検出手段の出力に基づいて前記入力手段により入力された基準信号の周波数と前記クロックの周波数との誤差を検出し、前記検出した誤差に基づいて前記基準信号の周波数変化の状態を示す情報を表示装置に表示する制御手段とを備える。

(もっと読む)

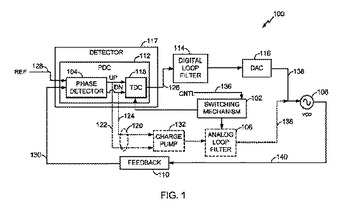

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

41 - 60 / 330

[ Back to top ]