PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL(Phase Locked Loop)回路に係り、特に、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路に関する。

【背景技術】

【0002】

[従来のPLL回路:図9]

従来のPLL回路について図9を参照しながら説明する。図9は、従来のPLL回路の構成図である。

従来のPLL回路は、図9に示すように、VCO(Voltage Controlled Oscillator:電圧制御発振器)1と、PLL IC(PLL Integrated Circuit:位相比較手段)2と、アナログフィルタ3と、基準発振器4と、DDS(Direct Digital Synthesizer)回路5と、制御回路6とから構成されている。

【0003】

VCO1は、アナログフィルタ3から出力される制御電圧によって所望の発振周波数Foutを出力する。

PLL IC2は、発振周波数Foutを入力し、制御回路6から供給される分周比の設定値で、DDS回路5からの出力周波数Fddsを基準信号(クロック)として分周を行い、分周周波数をアナログフィルタ3に出力する。

【0004】

アナログフィルタ3は、PLL IC2からの分周周波数を平滑化してVCO1の制御電圧として出力する。

基準発振器4は、VCXO(Voltage Controlled Crystal Oscillator)、TCXO(Temperature Compensated Crystal Oscillator)、OCXO(Oven Controlled Crystal Oscillator)等で構成され、制御回路6からの基準周波数選択信号に従って基準周波数FrefをDDS回路5に出力する。

【0005】

DDS回路5は、制御回路6からのFdds選択信号に従い、基準発振器4からの基準周波数Frefを基に生成された出力周波数FddsをPLL IC2に出力する。

制御回路6は、基準発振器4に基準周波数選択信号を出力し、DDS回路5にFdds選択信号を出力し、PLL IC2に分周比の設定データを出力する。

【0006】

[従来のPLL回路の動作]

従来のPLL回路において、制御回路6は、PLL IC2とDDS回路5に対して、PLL回路が発振器として使用されるシステムにおける規定のチャンネル(周波数)となるようなデータ(分周比の設定データ、Fdds選択信号)を出力し、設定を行う。

PLL IC2は、設定データに基づいて分周比、カウンタ値を決定し、DDS回路5は、PLL IC2の基準信号として使用される任意の出力周波数Fddsを決定する。これにより、VCO出力は規定周波数Foutとなるものである。

【0007】

[関連技術]

尚、関連する先行技術として、特開平07−131343号公報「周波数シンセサイザ」(出願人:アイコム株式会社)[特許文献1]、特開2007−208367号公報「同期信号生成装置、送信機及び制御方法」(出願人:株式会社ケンウッド)[特許文献2]、特開2002−141797号公報「周波数シンセサイザ」(出願人:三菱電機株式会社)[特許文献3]がある。

【0008】

特許文献1には、周波数シンセサイザにおいて、メモリに出力周波数毎に基準周波数切換信号とDDS出力周波数切換信号との組が記憶され、PLL回路がロックした時に不要波成分が通過帯域外に追いやられることが示されている。

【0009】

特許文献2には、同期信号生成装置において、送信波が指示周波数となり、DDSにおける入力周波数と出力周波数との組み合わせがDDSの出力におけるスプリアスを所定レベル以下にするよう、分周器(1/N)の分周比N、DDSの出力周波数/入力周波数、分周器(1/Ma)の分周比Ma、逓倍器(×Mb)の逓倍数Mbを調整することが示されている。

【0010】

特許文献3には、周波数シンセサイザにおいて、DDSの出力を位相同期ループに入力する前に、狭帯域の周波数可変型フィルタを通過させるようにし、当該フィルタにおける中心周波数を変化させてスプリアスを除去することが示されている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開平07−131343号公報

【特許文献2】特開2007−208367号公報

【特許文献3】特開2002−141797号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

従来のPLL回路では、シンセサイザとして使用される場合、DDS回路出力周波数Fdds、PLL ICの設定を変えることで、複数のチャンネル出力が可能となるが、DDSとして出力可能な周波数Fddsには上限があり、発振周波数Foutを上げるためには、PLL IC内での分周比を上げる必要がある。

【0013】

しかしながら、PLL IC内での分周比を上げることで、Fddsで得られたノイズ特性を劣化させてしまうという問題点があった。

例えば、分周比を100とした場合、20log100=40dBの劣化を伴うことになる。

【0014】

また、dds回路出力周波数自体を上げることは、回路としての消費電力を増大させることにもなり、PLL回路の信頼性が低下するという問題点がある。

【0015】

尚、特許文献1,2,3では、基準周波数とその逓倍周波数に対するFddsの折り返し周波数を利用してFdds(desired)を生成して所望の周波数を選択する構成とはなっていない。

【0016】

本発明は上記実状に鑑みて為されたもので、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記従来例の問題点を解決するための本発明は、電圧制御発振器と、電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させる可変フィルタと、可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力する第2の増幅器と、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、位相比較手段に分周比を出力する制御回路とを有することを特徴とする。

【0018】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする。

【0019】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、可変フィルタで希望する周波数を選択するよう可変周波数設定値を出力することを特徴とする。

【0020】

本発明は、上記PLL回路において、制御回路が、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、指示信号に対応して第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を記憶する設定値対応テーブルと、指示信号の入力に対して周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を出力する制御部とを有することを特徴とする。

【0021】

本発明は、電圧制御発振器と、電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、各々異なる周波数通過帯域特性を備える複数のフィルタと、外部から入力される選択信号により複数のフィルタを選択し、第1の増幅器からの出力信号を当該選択したフィルタに出力する第1のスイッチと、外部から入力される選択信号により選択したフィルタを選択し、当該フィルタからの出力信号を出力する第2のスイッチと、第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力する第2の増幅器と、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、第1のスイッチと第2のスイッチに当該指示信号に対応した選択信号を出力し、位相比較手段に分周比を出力する制御回路とを有することを特徴とする。

【0022】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする。

【0023】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、第1のスイッチ及び第2のスイッチで希望する周波数を選択するよう選択信号を出力することを特徴とする。

【0024】

本発明は、上記PLL回路において、制御回路が、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、指示信号に対応して第1の増幅設定値、第2の増幅設定値、選択信号、分周比を記憶する設定値対応テーブルと、指示信号の入力に対して周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、選択信号、分周比を出力する制御部とを有することを特徴とする。

【発明の効果】

【0025】

本発明によれば、基準発振器が、基準周波数選択信号によって基準周波数を可変として出力し、DDS回路が、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力し、第1の増幅器が、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅し、可変フィルタが、第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させ、第2の増幅器が、可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力し、制御回路が、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、位相比較手段に分周比を出力するPLL回路としているので、希望する基準信号を微細かつ広範囲に渡って生成して選択でき、ノイズ特性を劣化させることなく、消費電力を抑えて回路の信頼性を向上させることができる効果がある。

【0026】

本発明によれば、基準発振器が、基準周波数選択信号によって基準周波数を可変として出力し、DDS回路が、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力し、第1の増幅器が、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅し、複数のフィルタが、各々異なる周波数通過帯域特性を備え、第1のスイッチが、外部から入力される選択信号により複数のフィルタを選択し、第1の増幅器からの出力信号を当該選択したフィルタに出力し、第2のスイッチが、外部から入力される選択信号により選択したフィルタを選択し、当該フィルタからの出力信号を出力し、第2の増幅器が、第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力し、制御回路が、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、第1のスイッチと第2のスイッチに当該指示信号に対応した選択信号を出力し、位相比較手段に分周比を出力するPLL回路としているので、希望する基準信号を微細かつ広範囲に渡って生成して選択でき、ノイズ特性を劣化させることなく、消費電力を抑えて回路の信頼性を向上させることができる効果がある。

【図面の簡単な説明】

【0027】

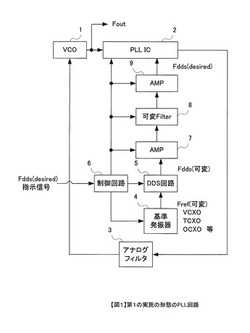

【図1】第1のPLL回路の構成図である。

【図2】DDS回路の構成例を示す図である。

【図3】可変フィルタの例1を示す図である。

【図4】可変フィルタの例2を示す図である。

【図5】得られるFdds(desired)の例を示す図である。

【図6】制御回路の構成図である。

【図7】制御部のフローチャートである。

【図8】第2の実施の形態に係るPLL回路の構成図である。

【図9】従来のPLL回路の構成図である。

【発明を実施するための形態】

【0028】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係るPLL回路は、基準周波数Frefに対してDDS回路の出力周波数Fddsを設定すると、Fref±Fdds、Fref×2±Fdds、Fref×3±Fdds、・・・、といった折り返しの周波数成分が発生する。本PLL回路では、これら折り返しの周波数成分を利用して、FrefとFddsを可変にしてその組み合わせによって所望のFdds(desired)を得ることができるものである。

【0029】

[第1のPLL回路:図1]

本発明の第1の実施の形態に係るPLL回路(第1のPLL回路)について図1を参照しながら説明する。図1は、第1のPLL回路の構成図である。

第1のPLL回路は、図1に示すように、VCO1と、PLL IC2と、アナログフィルタ3と、基準発振器4と、DDS回路5と、制御回路6と、第1のアンプ(AMP)7と、可変フィルタ(Filter)8と、第2のアンプ(AMP)9とを有している。

【0030】

[各部]

第1のPLL回路の各部を説明する。

VCO1は、アナログフィルタ3から出力される制御電圧によって所望の発振周波数Foutを出力する。

PLL IC2は、発振周波数Foutを入力し、制御回路6から供給される分周比の設定値で、DDS回路5から第2のアンプ9を介して出力される出力周波数Fdds(desired)を基準信号(クロック)として分周を行い、分周周波数をアナログフィルタ3に出力する位相比較器又は位相比較手段である。

【0031】

アナログフィルタ3は、PLL IC2からの分周周波数を平滑化してVCO1の制御電圧として出力する。

基準発振器4は、VCXO、TCXO、OCXO等で構成され、制御回路6からの基準周波数選択信号に従って基準周波数FrefをDDS回路5に出力する。

【0032】

DDS回路5は、制御回路6からのFdds選択信号に従い、基準発振器4からの基準周波数Frefを基にFddsを生成して第1のAMP7に出力する。

ここで、DDS回路5では、Fddsだけでなく、基準周波数Frefとその逓倍周波数Fref×nに±Fddsの折り返し周波数が発生するが、それらの周波数信号もDDS回路5から第1のAMP7に出力されることになる。

【0033】

制御回路6は、基準発振器4に基準周波数Fref選択信号を出力し、DDS回路5にFdds選択信号を出力し、第1のAMP7及び第2のAMP9に増幅設定値1,2を出力し、可変フィルタ8に可変周波数設定値を出力し、PLL IC2に分周比の設定データを出力する。

制御回路6の内部構成、処理内容については後述する。

【0034】

第1のアンプ(AMP)7は、制御回路6からの増幅設定値1によりDDS回路5からの出力信号を選択する信号に対応して増幅する。

可変フィルタ8は、制御回路6からの可変周波数設定値により通過帯域を可変として、第1のAMP7からの信号(選択する信号)を通過させ、第2のAMP9に出力する。

第2のアンプ(AMP)9は、制御回路6からの増幅設定値2により可変フィルタ8からの出力信号を選択する信号に対応して増幅する。

【0035】

[DSS回路:図2]

次に、DDS回路5について図2を参照しながら説明する。図2は、DDS回路の構成例を示す図である。

DDS回路5は、図2に示すように、加算器51と、フリップフロップ52と、サインウェーブテーブル53と、デジタル/アナログコンバータ(ADC)54と、フィルタ55とから構成されている。

フリップフフロップ52とADC54には、基準発振器4からの基準周波数Frefに基づいたサンプリングクロックが入力される。

【0036】

加算器51は、制御回路6から入力される周波数設定値とフリップフフロップ52からの出力値を加算してフリップフフロップ52に出力する。

フリップフロップ52は、加算器51からの値をサンプリングクロックでサンプリングしてサンプル値を加算器51とサインウェーブテーブル53に出力する。

【0037】

サインウェーブテーブル53は、入力値に対するサインウェーブの出力値を記憶するテーブルであり、フリップフフロップ52からの入力値をテーブルアドレスとして対応するサインウェーブのデータを読み取り、テーブルデータとしてADC54に出力する。

【0038】

ADC54は、サインウェーブテーブル53からのテーブルデータをサンプリングクロックを用いてアナログ変換してフィルタ55に出力する。

フィルタ55は、ADC54からの出力をフィルタリングしてアナログ・サインウェーブとして第1のAMP7に出力する。

【0039】

[可変フィルタ:図3,4]

次に、可変フィルタ8について図3,4を参照しながら説明する。図3は、可変フィルタの例1を示す図であり、図4は、可変フィルタの例2を示す図である。

可変フィルタ1は、図3に示すように、入力端子と出力端子との間に、可変容量ダイオードD、コンデンサC、コイルLを直列に接続し、可変容量ダイオードDとコンデンサCとの間に抵抗R1を介して電源Vcが印加され、入力段には抵抗R2の一端が接続され、他端は接地されている。

【0040】

また、可変フィルタ2は、図4に示すように、可変フィルタ1を基本に、入力段に、コイルL2の一端が接続されて他端が接続され、また、コンデンサC2の一端が接続されて他端がダイオードD2のカソード側に接続され、ダイオードD2のアノード側が接地され、コンデンサC2とダイオードD2との間には、抵抗R2を介して電圧Vc1が接続されている。また、出力段にも入力段と同様の構成を備えている。

【0041】

[Fdds(desired)の例:図5]

次に、FrefとFddsの組み合わせによって得られるFdds(desired)の例について図5を用いて説明する。図5は、得られるFdds(desired)の例を示す図である。

図5では、Frefを40MHz固定とし、Fddsを10MHzから20MHzまで1MHzステップに変化させた時に発生する折り返し周波数の例を示している。

【0042】

従来では、Fddsのみを変化させた場合、10〜20MHzのみが得られていた。これに対して、図5の例では、40MHzと40MHzの逓倍の周波数に対する±Fddsの折り返し周波数を利用した場合、20MHz〜30MHz、50MHz〜70MHz等を1MHzステップにFdds(desired)の周波数を得ることができる。

【0043】

更に、用途に応じて、Fddsの変化幅を100kHz、10kHz等変え、Frefを変えることにより微細かつ広範囲に渡るFdds(desired)を得ることが可能となる。

尚、Fdds(desired)の選択精度を上げるために可変フィルタ8が設けられ、PLL IC2の入力レベルを上げるために第1のAMP7、第2のAMP9が設けられている。

【0044】

[制御回路:図6]

次に、制御回路6について図6を参照しながら説明する。図6は、制御回路の構成図である。

制御回路6は、図6に示すように、制御部61と、周波数テーブル62と、設定値等対応テーブル63とを基本的に有している。

制御部61は、外部からのFdds(desired)指示信号を入力し、当該指示信号に対応して周波数テーブル62と設定値等対応テーブル63を参照して以下の信号、値を出力する。

【0045】

尚、Fdds(desired)指示信号とは、PLL回路の設定者がFdds(desired)を得るための指示信号である。

Fref選択信号は、基準発振器4において発振される基準周波数Frefを特定するための信号である。

Fdds指示信号は、DDS回路5におけるFddsを指定する信号である。

増幅設定値1は、Fdds(desired)に対応した第1のAMP7における増幅設定値を示し、増幅設定値2は、第2のAMP9における増幅設定値を示している。

可変周波数設定値は、Fdds(desired)に対応した可変フィルタ8における可変周波数設定値である。

分周比Nは、Fdds(desired)に対応したPLL IC2における分周比を示している。

【0046】

周波数テーブル62は、Fdds(desired)指示信号に対応するFref選択信号の値、Fdds指示信号の値を記憶しており、具体的には、図5に示した対応関係が、Fdds(desired)からFrefとFddsが得られるテーブルとなっている。上述したとおり、FrefもFddsも、値を細かく設定可能となっている。

設定値等対応テーブル63は、Fdds(desired)指示信号に対して予め増幅設定値1,2、可変周波数設定値、分周比Nを記憶している。

【0047】

[制御部フロー:図7]

次に、制御部61における処理フローについて図7を参照しながら説明する。図7は、制御部のフローチャートである。

制御部61は、外部(操作者又は設定者)からFdds(desired)指示信号が入力されると(S1)、周波数テーブル62を参照し、Fref、Fref×n、Fddsを特定し(S2)、Fref選択信号を基準発振器4に出し(S3)、Fdds指示信号をDDS回路5に出力する(S4)。

【0048】

また、制御部61は、設定値等設定テーブル63を参照し、Fdds(desired)に対応するAMP7,9への増幅設定値をAMP7,9に出力する(S5)。

更に、制御部6は、設定値等設定対応テーブル63を参照し、Fdds(desired)に対応する可変周波数設定値を可変フィルタ8に出力し(S6)、Fdds(desired)に対応する分周比NをPLL IC2に出力する(S7)。

【0049】

[第2のPLL回路:図8]

次に、第2の実施の形態に係るPLL回路(第2のPLL回路)について図8を参照しながら説明する。図8は、第2の実施の形態に係るPLL回路の構成図である。

第2のPLL回路は、図8に示すように、図1に示す第1のPLL回路と相違する部分として、可変フィルタ8の代わりに複数のフィルタ8a,8b,8cと、それらのフィルタを選択するための第1のスイッチ(SW(1))10aと、第2のスイッチ(SW(2))10bが設けられている点である。

【0050】

また、図1では、制御回路6が可変フィルタ8に対して可変周波数設定値を出力したが、図8では、制御回路6がSW(1)10aとSW(2)10bに対してフィルタ選択の指示信号を出力している。

図8では、3つのフィルタ8a〜8cを示しているが、2つであってもよいし、4つ以上であってもよい。

【0051】

[相違する各部]

第2のPLL回路において、第1のPLL回路と相違する各部について説明する。

第1のAMP7は、増幅出力をSW(1)10aに出力する。

SW(1)10aは、制御回路6からのフィルタ選択信号に従って選択したフィルタに第1のAMP7からの増幅信号を出力する。

【0052】

SW(2)10bは、制御回路6からのフィルタ選択信号に従って選択したフィルタからの出力を選択し、第2のAMP9に出力する。

第2のAMP9は、SW(2)10bからの出力を増幅してPLL IC2にFdds(desired)として出力する。

【0053】

そして、制御回路6は、SW(1)10aとSW(2)10bに対して使用するフィルタを選択するフィルタ選択指示信号を出力する。

従って、制御部内の構成において、設定値等対応テーブル63には可変周波数設定値の代わりに2つのスイッチを選択するためのフィルタ選択指示信号が記憶され、制御部61は、Fdds(desired)指示信号に対して設定値等対応テーブル63を参照し、2つのSWにフィルタ選択指示信号を出力する。

【0054】

[実施の形態の効果]

本発明の実施の形態に係るPLL回路は、FrefとFddsの双方の値を細かく設定可能としたことにより、両者の組み合わせによって、微細かつ広範囲に渡るFdds(desired)を生成し、可変フィルタ8又は複数のフィルタ8a〜8cによって所望のFdds(desired)を選択し、PLL IC2に供給するようにしているので、ノイズ特性を劣化させることなく、DDS回路5の消費電力を抑えることで、PLL回路の消費電力も抑えて回路の信頼性を向上させることができる効果がある。

【産業上の利用可能性】

【0055】

本発明は、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路に好適である。

【符号の説明】

【0056】

1…VCO、 2…PLL IC、 3…アナログフィルタ、 4…基準発振器、 5…DDS回路、 6…制御回路、 7…第1のアンプ(AMP)、 8…可変フィルタ、 8a…フィルタ、 8b…フィルタ、 8c…フィルタ、 9…第2のアンプ(AMP)、 10a…第1のスイッチ(SW(1))、 10b…第2のスイッチ(SW(2))、 51…加算器、 52…フリップフロップ、 53…サインウェーブテーブル、 54…デジタル/アナログコンバータ(ADC)、 55…フィルタ、 61…制御部、 62…周波数テーブル、 63…設定値等対応テーブル

【技術分野】

【0001】

本発明は、PLL(Phase Locked Loop)回路に係り、特に、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路に関する。

【背景技術】

【0002】

[従来のPLL回路:図9]

従来のPLL回路について図9を参照しながら説明する。図9は、従来のPLL回路の構成図である。

従来のPLL回路は、図9に示すように、VCO(Voltage Controlled Oscillator:電圧制御発振器)1と、PLL IC(PLL Integrated Circuit:位相比較手段)2と、アナログフィルタ3と、基準発振器4と、DDS(Direct Digital Synthesizer)回路5と、制御回路6とから構成されている。

【0003】

VCO1は、アナログフィルタ3から出力される制御電圧によって所望の発振周波数Foutを出力する。

PLL IC2は、発振周波数Foutを入力し、制御回路6から供給される分周比の設定値で、DDS回路5からの出力周波数Fddsを基準信号(クロック)として分周を行い、分周周波数をアナログフィルタ3に出力する。

【0004】

アナログフィルタ3は、PLL IC2からの分周周波数を平滑化してVCO1の制御電圧として出力する。

基準発振器4は、VCXO(Voltage Controlled Crystal Oscillator)、TCXO(Temperature Compensated Crystal Oscillator)、OCXO(Oven Controlled Crystal Oscillator)等で構成され、制御回路6からの基準周波数選択信号に従って基準周波数FrefをDDS回路5に出力する。

【0005】

DDS回路5は、制御回路6からのFdds選択信号に従い、基準発振器4からの基準周波数Frefを基に生成された出力周波数FddsをPLL IC2に出力する。

制御回路6は、基準発振器4に基準周波数選択信号を出力し、DDS回路5にFdds選択信号を出力し、PLL IC2に分周比の設定データを出力する。

【0006】

[従来のPLL回路の動作]

従来のPLL回路において、制御回路6は、PLL IC2とDDS回路5に対して、PLL回路が発振器として使用されるシステムにおける規定のチャンネル(周波数)となるようなデータ(分周比の設定データ、Fdds選択信号)を出力し、設定を行う。

PLL IC2は、設定データに基づいて分周比、カウンタ値を決定し、DDS回路5は、PLL IC2の基準信号として使用される任意の出力周波数Fddsを決定する。これにより、VCO出力は規定周波数Foutとなるものである。

【0007】

[関連技術]

尚、関連する先行技術として、特開平07−131343号公報「周波数シンセサイザ」(出願人:アイコム株式会社)[特許文献1]、特開2007−208367号公報「同期信号生成装置、送信機及び制御方法」(出願人:株式会社ケンウッド)[特許文献2]、特開2002−141797号公報「周波数シンセサイザ」(出願人:三菱電機株式会社)[特許文献3]がある。

【0008】

特許文献1には、周波数シンセサイザにおいて、メモリに出力周波数毎に基準周波数切換信号とDDS出力周波数切換信号との組が記憶され、PLL回路がロックした時に不要波成分が通過帯域外に追いやられることが示されている。

【0009】

特許文献2には、同期信号生成装置において、送信波が指示周波数となり、DDSにおける入力周波数と出力周波数との組み合わせがDDSの出力におけるスプリアスを所定レベル以下にするよう、分周器(1/N)の分周比N、DDSの出力周波数/入力周波数、分周器(1/Ma)の分周比Ma、逓倍器(×Mb)の逓倍数Mbを調整することが示されている。

【0010】

特許文献3には、周波数シンセサイザにおいて、DDSの出力を位相同期ループに入力する前に、狭帯域の周波数可変型フィルタを通過させるようにし、当該フィルタにおける中心周波数を変化させてスプリアスを除去することが示されている。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開平07−131343号公報

【特許文献2】特開2007−208367号公報

【特許文献3】特開2002−141797号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

従来のPLL回路では、シンセサイザとして使用される場合、DDS回路出力周波数Fdds、PLL ICの設定を変えることで、複数のチャンネル出力が可能となるが、DDSとして出力可能な周波数Fddsには上限があり、発振周波数Foutを上げるためには、PLL IC内での分周比を上げる必要がある。

【0013】

しかしながら、PLL IC内での分周比を上げることで、Fddsで得られたノイズ特性を劣化させてしまうという問題点があった。

例えば、分周比を100とした場合、20log100=40dBの劣化を伴うことになる。

【0014】

また、dds回路出力周波数自体を上げることは、回路としての消費電力を増大させることにもなり、PLL回路の信頼性が低下するという問題点がある。

【0015】

尚、特許文献1,2,3では、基準周波数とその逓倍周波数に対するFddsの折り返し周波数を利用してFdds(desired)を生成して所望の周波数を選択する構成とはなっていない。

【0016】

本発明は上記実状に鑑みて為されたもので、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供することを目的とする。

【課題を解決するための手段】

【0017】

上記従来例の問題点を解決するための本発明は、電圧制御発振器と、電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させる可変フィルタと、可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力する第2の増幅器と、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、位相比較手段に分周比を出力する制御回路とを有することを特徴とする。

【0018】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする。

【0019】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、可変フィルタで希望する周波数を選択するよう可変周波数設定値を出力することを特徴とする。

【0020】

本発明は、上記PLL回路において、制御回路が、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、指示信号に対応して第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を記憶する設定値対応テーブルと、指示信号の入力に対して周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を出力する制御部とを有することを特徴とする。

【0021】

本発明は、電圧制御発振器と、電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、各々異なる周波数通過帯域特性を備える複数のフィルタと、外部から入力される選択信号により複数のフィルタを選択し、第1の増幅器からの出力信号を当該選択したフィルタに出力する第1のスイッチと、外部から入力される選択信号により選択したフィルタを選択し、当該フィルタからの出力信号を出力する第2のスイッチと、第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力する第2の増幅器と、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、第1のスイッチと第2のスイッチに当該指示信号に対応した選択信号を出力し、位相比較手段に分周比を出力する制御回路とを有することを特徴とする。

【0022】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする。

【0023】

本発明は、上記PLL回路において、制御回路が、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、第1のスイッチ及び第2のスイッチで希望する周波数を選択するよう選択信号を出力することを特徴とする。

【0024】

本発明は、上記PLL回路において、制御回路が、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、指示信号に対応して第1の増幅設定値、第2の増幅設定値、選択信号、分周比を記憶する設定値対応テーブルと、指示信号の入力に対して周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、選択信号、分周比を出力する制御部とを有することを特徴とする。

【発明の効果】

【0025】

本発明によれば、基準発振器が、基準周波数選択信号によって基準周波数を可変として出力し、DDS回路が、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力し、第1の増幅器が、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅し、可変フィルタが、第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させ、第2の増幅器が、可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力し、制御回路が、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、位相比較手段に分周比を出力するPLL回路としているので、希望する基準信号を微細かつ広範囲に渡って生成して選択でき、ノイズ特性を劣化させることなく、消費電力を抑えて回路の信頼性を向上させることができる効果がある。

【0026】

本発明によれば、基準発振器が、基準周波数選択信号によって基準周波数を可変として出力し、DDS回路が、入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力し、第1の増幅器が、DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅し、複数のフィルタが、各々異なる周波数通過帯域特性を備え、第1のスイッチが、外部から入力される選択信号により複数のフィルタを選択し、第1の増幅器からの出力信号を当該選択したフィルタに出力し、第2のスイッチが、外部から入力される選択信号により選択したフィルタを選択し、当該フィルタからの出力信号を出力し、第2の増幅器が、第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、位相比較手段に基準信号として出力し、制御回路が、基準信号を希望する周波数にする指示信号が入力されると、基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、DDS回路に当該指示信号に対応した出力指示信号を出力し、第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、第1のスイッチと第2のスイッチに当該指示信号に対応した選択信号を出力し、位相比較手段に分周比を出力するPLL回路としているので、希望する基準信号を微細かつ広範囲に渡って生成して選択でき、ノイズ特性を劣化させることなく、消費電力を抑えて回路の信頼性を向上させることができる効果がある。

【図面の簡単な説明】

【0027】

【図1】第1のPLL回路の構成図である。

【図2】DDS回路の構成例を示す図である。

【図3】可変フィルタの例1を示す図である。

【図4】可変フィルタの例2を示す図である。

【図5】得られるFdds(desired)の例を示す図である。

【図6】制御回路の構成図である。

【図7】制御部のフローチャートである。

【図8】第2の実施の形態に係るPLL回路の構成図である。

【図9】従来のPLL回路の構成図である。

【発明を実施するための形態】

【0028】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係るPLL回路は、基準周波数Frefに対してDDS回路の出力周波数Fddsを設定すると、Fref±Fdds、Fref×2±Fdds、Fref×3±Fdds、・・・、といった折り返しの周波数成分が発生する。本PLL回路では、これら折り返しの周波数成分を利用して、FrefとFddsを可変にしてその組み合わせによって所望のFdds(desired)を得ることができるものである。

【0029】

[第1のPLL回路:図1]

本発明の第1の実施の形態に係るPLL回路(第1のPLL回路)について図1を参照しながら説明する。図1は、第1のPLL回路の構成図である。

第1のPLL回路は、図1に示すように、VCO1と、PLL IC2と、アナログフィルタ3と、基準発振器4と、DDS回路5と、制御回路6と、第1のアンプ(AMP)7と、可変フィルタ(Filter)8と、第2のアンプ(AMP)9とを有している。

【0030】

[各部]

第1のPLL回路の各部を説明する。

VCO1は、アナログフィルタ3から出力される制御電圧によって所望の発振周波数Foutを出力する。

PLL IC2は、発振周波数Foutを入力し、制御回路6から供給される分周比の設定値で、DDS回路5から第2のアンプ9を介して出力される出力周波数Fdds(desired)を基準信号(クロック)として分周を行い、分周周波数をアナログフィルタ3に出力する位相比較器又は位相比較手段である。

【0031】

アナログフィルタ3は、PLL IC2からの分周周波数を平滑化してVCO1の制御電圧として出力する。

基準発振器4は、VCXO、TCXO、OCXO等で構成され、制御回路6からの基準周波数選択信号に従って基準周波数FrefをDDS回路5に出力する。

【0032】

DDS回路5は、制御回路6からのFdds選択信号に従い、基準発振器4からの基準周波数Frefを基にFddsを生成して第1のAMP7に出力する。

ここで、DDS回路5では、Fddsだけでなく、基準周波数Frefとその逓倍周波数Fref×nに±Fddsの折り返し周波数が発生するが、それらの周波数信号もDDS回路5から第1のAMP7に出力されることになる。

【0033】

制御回路6は、基準発振器4に基準周波数Fref選択信号を出力し、DDS回路5にFdds選択信号を出力し、第1のAMP7及び第2のAMP9に増幅設定値1,2を出力し、可変フィルタ8に可変周波数設定値を出力し、PLL IC2に分周比の設定データを出力する。

制御回路6の内部構成、処理内容については後述する。

【0034】

第1のアンプ(AMP)7は、制御回路6からの増幅設定値1によりDDS回路5からの出力信号を選択する信号に対応して増幅する。

可変フィルタ8は、制御回路6からの可変周波数設定値により通過帯域を可変として、第1のAMP7からの信号(選択する信号)を通過させ、第2のAMP9に出力する。

第2のアンプ(AMP)9は、制御回路6からの増幅設定値2により可変フィルタ8からの出力信号を選択する信号に対応して増幅する。

【0035】

[DSS回路:図2]

次に、DDS回路5について図2を参照しながら説明する。図2は、DDS回路の構成例を示す図である。

DDS回路5は、図2に示すように、加算器51と、フリップフロップ52と、サインウェーブテーブル53と、デジタル/アナログコンバータ(ADC)54と、フィルタ55とから構成されている。

フリップフフロップ52とADC54には、基準発振器4からの基準周波数Frefに基づいたサンプリングクロックが入力される。

【0036】

加算器51は、制御回路6から入力される周波数設定値とフリップフフロップ52からの出力値を加算してフリップフフロップ52に出力する。

フリップフロップ52は、加算器51からの値をサンプリングクロックでサンプリングしてサンプル値を加算器51とサインウェーブテーブル53に出力する。

【0037】

サインウェーブテーブル53は、入力値に対するサインウェーブの出力値を記憶するテーブルであり、フリップフフロップ52からの入力値をテーブルアドレスとして対応するサインウェーブのデータを読み取り、テーブルデータとしてADC54に出力する。

【0038】

ADC54は、サインウェーブテーブル53からのテーブルデータをサンプリングクロックを用いてアナログ変換してフィルタ55に出力する。

フィルタ55は、ADC54からの出力をフィルタリングしてアナログ・サインウェーブとして第1のAMP7に出力する。

【0039】

[可変フィルタ:図3,4]

次に、可変フィルタ8について図3,4を参照しながら説明する。図3は、可変フィルタの例1を示す図であり、図4は、可変フィルタの例2を示す図である。

可変フィルタ1は、図3に示すように、入力端子と出力端子との間に、可変容量ダイオードD、コンデンサC、コイルLを直列に接続し、可変容量ダイオードDとコンデンサCとの間に抵抗R1を介して電源Vcが印加され、入力段には抵抗R2の一端が接続され、他端は接地されている。

【0040】

また、可変フィルタ2は、図4に示すように、可変フィルタ1を基本に、入力段に、コイルL2の一端が接続されて他端が接続され、また、コンデンサC2の一端が接続されて他端がダイオードD2のカソード側に接続され、ダイオードD2のアノード側が接地され、コンデンサC2とダイオードD2との間には、抵抗R2を介して電圧Vc1が接続されている。また、出力段にも入力段と同様の構成を備えている。

【0041】

[Fdds(desired)の例:図5]

次に、FrefとFddsの組み合わせによって得られるFdds(desired)の例について図5を用いて説明する。図5は、得られるFdds(desired)の例を示す図である。

図5では、Frefを40MHz固定とし、Fddsを10MHzから20MHzまで1MHzステップに変化させた時に発生する折り返し周波数の例を示している。

【0042】

従来では、Fddsのみを変化させた場合、10〜20MHzのみが得られていた。これに対して、図5の例では、40MHzと40MHzの逓倍の周波数に対する±Fddsの折り返し周波数を利用した場合、20MHz〜30MHz、50MHz〜70MHz等を1MHzステップにFdds(desired)の周波数を得ることができる。

【0043】

更に、用途に応じて、Fddsの変化幅を100kHz、10kHz等変え、Frefを変えることにより微細かつ広範囲に渡るFdds(desired)を得ることが可能となる。

尚、Fdds(desired)の選択精度を上げるために可変フィルタ8が設けられ、PLL IC2の入力レベルを上げるために第1のAMP7、第2のAMP9が設けられている。

【0044】

[制御回路:図6]

次に、制御回路6について図6を参照しながら説明する。図6は、制御回路の構成図である。

制御回路6は、図6に示すように、制御部61と、周波数テーブル62と、設定値等対応テーブル63とを基本的に有している。

制御部61は、外部からのFdds(desired)指示信号を入力し、当該指示信号に対応して周波数テーブル62と設定値等対応テーブル63を参照して以下の信号、値を出力する。

【0045】

尚、Fdds(desired)指示信号とは、PLL回路の設定者がFdds(desired)を得るための指示信号である。

Fref選択信号は、基準発振器4において発振される基準周波数Frefを特定するための信号である。

Fdds指示信号は、DDS回路5におけるFddsを指定する信号である。

増幅設定値1は、Fdds(desired)に対応した第1のAMP7における増幅設定値を示し、増幅設定値2は、第2のAMP9における増幅設定値を示している。

可変周波数設定値は、Fdds(desired)に対応した可変フィルタ8における可変周波数設定値である。

分周比Nは、Fdds(desired)に対応したPLL IC2における分周比を示している。

【0046】

周波数テーブル62は、Fdds(desired)指示信号に対応するFref選択信号の値、Fdds指示信号の値を記憶しており、具体的には、図5に示した対応関係が、Fdds(desired)からFrefとFddsが得られるテーブルとなっている。上述したとおり、FrefもFddsも、値を細かく設定可能となっている。

設定値等対応テーブル63は、Fdds(desired)指示信号に対して予め増幅設定値1,2、可変周波数設定値、分周比Nを記憶している。

【0047】

[制御部フロー:図7]

次に、制御部61における処理フローについて図7を参照しながら説明する。図7は、制御部のフローチャートである。

制御部61は、外部(操作者又は設定者)からFdds(desired)指示信号が入力されると(S1)、周波数テーブル62を参照し、Fref、Fref×n、Fddsを特定し(S2)、Fref選択信号を基準発振器4に出し(S3)、Fdds指示信号をDDS回路5に出力する(S4)。

【0048】

また、制御部61は、設定値等設定テーブル63を参照し、Fdds(desired)に対応するAMP7,9への増幅設定値をAMP7,9に出力する(S5)。

更に、制御部6は、設定値等設定対応テーブル63を参照し、Fdds(desired)に対応する可変周波数設定値を可変フィルタ8に出力し(S6)、Fdds(desired)に対応する分周比NをPLL IC2に出力する(S7)。

【0049】

[第2のPLL回路:図8]

次に、第2の実施の形態に係るPLL回路(第2のPLL回路)について図8を参照しながら説明する。図8は、第2の実施の形態に係るPLL回路の構成図である。

第2のPLL回路は、図8に示すように、図1に示す第1のPLL回路と相違する部分として、可変フィルタ8の代わりに複数のフィルタ8a,8b,8cと、それらのフィルタを選択するための第1のスイッチ(SW(1))10aと、第2のスイッチ(SW(2))10bが設けられている点である。

【0050】

また、図1では、制御回路6が可変フィルタ8に対して可変周波数設定値を出力したが、図8では、制御回路6がSW(1)10aとSW(2)10bに対してフィルタ選択の指示信号を出力している。

図8では、3つのフィルタ8a〜8cを示しているが、2つであってもよいし、4つ以上であってもよい。

【0051】

[相違する各部]

第2のPLL回路において、第1のPLL回路と相違する各部について説明する。

第1のAMP7は、増幅出力をSW(1)10aに出力する。

SW(1)10aは、制御回路6からのフィルタ選択信号に従って選択したフィルタに第1のAMP7からの増幅信号を出力する。

【0052】

SW(2)10bは、制御回路6からのフィルタ選択信号に従って選択したフィルタからの出力を選択し、第2のAMP9に出力する。

第2のAMP9は、SW(2)10bからの出力を増幅してPLL IC2にFdds(desired)として出力する。

【0053】

そして、制御回路6は、SW(1)10aとSW(2)10bに対して使用するフィルタを選択するフィルタ選択指示信号を出力する。

従って、制御部内の構成において、設定値等対応テーブル63には可変周波数設定値の代わりに2つのスイッチを選択するためのフィルタ選択指示信号が記憶され、制御部61は、Fdds(desired)指示信号に対して設定値等対応テーブル63を参照し、2つのSWにフィルタ選択指示信号を出力する。

【0054】

[実施の形態の効果]

本発明の実施の形態に係るPLL回路は、FrefとFddsの双方の値を細かく設定可能としたことにより、両者の組み合わせによって、微細かつ広範囲に渡るFdds(desired)を生成し、可変フィルタ8又は複数のフィルタ8a〜8cによって所望のFdds(desired)を選択し、PLL IC2に供給するようにしているので、ノイズ特性を劣化させることなく、DDS回路5の消費電力を抑えることで、PLL回路の消費電力も抑えて回路の信頼性を向上させることができる効果がある。

【産業上の利用可能性】

【0055】

本発明は、ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路に好適である。

【符号の説明】

【0056】

1…VCO、 2…PLL IC、 3…アナログフィルタ、 4…基準発振器、 5…DDS回路、 6…制御回路、 7…第1のアンプ(AMP)、 8…可変フィルタ、 8a…フィルタ、 8b…フィルタ、 8c…フィルタ、 9…第2のアンプ(AMP)、 10a…第1のスイッチ(SW(1))、 10b…第2のスイッチ(SW(2))、 51…加算器、 52…フリップフロップ、 53…サインウェーブテーブル、 54…デジタル/アナログコンバータ(ADC)、 55…フィルタ、 61…制御部、 62…周波数テーブル、 63…設定値等対応テーブル

【特許請求の範囲】

【請求項1】

電圧制御発振器と、前記電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、

基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、

入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、前記基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、

前記DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、

前記第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させる可変フィルタと、

前記可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、前記位相比較手段に基準信号として出力する第2の増幅器と、

前記基準信号を希望する周波数にする指示信号が入力されると、前記基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、前記DDS回路に当該指示信号に対応した出力指示信号を出力し、前記第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、前記可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、前記第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、前記位相比較手段に分周比を出力する制御回路とを有することを特徴とするPLL回路。

【請求項2】

制御回路は、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする請求項1記載のPLL回路。

【請求項3】

制御回路は、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、可変フィルタで希望する周波数を選択するよう可変周波数設定値を出力することを特徴とする請求項1又は2記載のPLL回路。

【請求項4】

制御回路は、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、前記指示信号に対応して第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を記憶する設定値対応テーブルと、前記指示信号の入力に対して前記周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、前記設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を出力する制御部とを有することを特徴とする請求項1乃至3のいずれか記載のPLL回路。

【請求項5】

電圧制御発振器と、前記電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、

基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、

入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、前記基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、

前記DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、

各々異なる周波数通過帯域特性を備える複数のフィルタと、

外部から入力される選択信号により前記複数のフィルタを選択し、前記第1の増幅器からの出力信号を当該選択したフィルタに出力する第1のスイッチと、

外部から入力される選択信号により前記選択したフィルタを選択し、当該フィルタからの出力信号を出力する第2のスイッチと、

前記第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、前記位相比較手段に基準信号として出力する第2の増幅器と、

前記基準信号を希望する周波数にする指示信号が入力されると、前記基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、前記DDS回路に当該指示信号に対応した出力指示信号を出力し、前記第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、前記第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、前記第1のスイッチと前記第2のスイッチに当該指示信号に対応した選択信号を出力し、前記位相比較手段に分周比を出力する制御回路とを有することを特徴とするPLL回路。

【請求項6】

制御回路は、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする請求項5記載のPLL回路。

【請求項7】

制御回路は、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、第1のスイッチ及び第2のスイッチで希望する周波数を選択するよう選択信号を出力することを特徴とする請求項5又は6記載のPLL回路。

【請求項8】

制御回路は、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、前記指示信号に対応して第1の増幅設定値、第2の増幅設定値、選択信号、分周比を記憶する設定値対応テーブルと、前記指示信号の入力に対して前記周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、前記設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、選択信号、分周比を出力する制御部とを有することを特徴とする請求項5乃至7のいずれか記載のPLL回路。

【請求項1】

電圧制御発振器と、前記電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、

基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、

入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、前記基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、

前記DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、

前記第1の増幅器からの出力信号を外部から入力される可変周波数設定値に応じて周波数通過帯域を可変にして通過させる可変フィルタと、

前記可変フィルタからの出力信号を外部から入力される第2の増幅設定値で増幅し、前記位相比較手段に基準信号として出力する第2の増幅器と、

前記基準信号を希望する周波数にする指示信号が入力されると、前記基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、前記DDS回路に当該指示信号に対応した出力指示信号を出力し、前記第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、前記可変フィルタに当該指示信号に対応した可変周波数設定値を出力し、前記第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、前記位相比較手段に分周比を出力する制御回路とを有することを特徴とするPLL回路。

【請求項2】

制御回路は、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする請求項1記載のPLL回路。

【請求項3】

制御回路は、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、可変フィルタで希望する周波数を選択するよう可変周波数設定値を出力することを特徴とする請求項1又は2記載のPLL回路。

【請求項4】

制御回路は、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、前記指示信号に対応して第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を記憶する設定値対応テーブルと、前記指示信号の入力に対して前記周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、前記設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、可変周波数設定値、分周比を出力する制御部とを有することを特徴とする請求項1乃至3のいずれか記載のPLL回路。

【請求項5】

電圧制御発振器と、前記電圧制御発振器の出力を分周して基準信号との位相を比較し、位相差に基づく信号を前記電圧制御発振器の制御電圧として出力する位相比較手段とを有するPLL回路であって、

基準周波数選択信号によって基準周波数を可変として出力する基準発振器と、

入力される基準周波数に基づいて外部からの出力指示信号に応じて出力信号を出力すると共に、前記基準周波数及び当該周波数の逓倍の周波数に対する出力信号の折り返し信号も出力するDDS回路と、

前記DDS回路からの出力信号を外部から入力される第1の増幅設定値で増幅する第1の増幅器と、

各々異なる周波数通過帯域特性を備える複数のフィルタと、

外部から入力される選択信号により前記複数のフィルタを選択し、前記第1の増幅器からの出力信号を当該選択したフィルタに出力する第1のスイッチと、

外部から入力される選択信号により前記選択したフィルタを選択し、当該フィルタからの出力信号を出力する第2のスイッチと、

前記第2のスイッチからの出力信号を外部から入力される第2の増幅設定値で増幅し、前記位相比較手段に基準信号として出力する第2の増幅器と、

前記基準信号を希望する周波数にする指示信号が入力されると、前記基準発振器に当該指示信号に対応した基準周波数選択信号を出力し、前記DDS回路に当該指示信号に対応した出力指示信号を出力し、前記第1の増幅器に当該指示信号に対応した第1の増幅設定値を出力し、前記第2の増幅器に当該指示信号に対応した第2の増幅設定値を出力し、前記第1のスイッチと前記第2のスイッチに当該指示信号に対応した選択信号を出力し、前記位相比較手段に分周比を出力する制御回路とを有することを特徴とするPLL回路。

【請求項6】

制御回路は、基準信号を希望する周波数にするために、基準発振器における基準周波数とDDS回路における出力信号の双方を可変とする基準周波数選択信号と出力指示信号を出力することを特徴とする請求項5記載のPLL回路。

【請求項7】

制御回路は、基準信号を希望する周波数にするために、基準周波数及び当該周波数の逓倍の周波数に対して出力信号の折り返しの周波数をDDS回路で生成させ、第1のスイッチ及び第2のスイッチで希望する周波数を選択するよう選択信号を出力することを特徴とする請求項5又は6記載のPLL回路。

【請求項8】

制御回路は、入力される指示信号に対応して基準周波数選択信号と出力指示信号を記憶する周波数テーブルと、前記指示信号に対応して第1の増幅設定値、第2の増幅設定値、選択信号、分周比を記憶する設定値対応テーブルと、前記指示信号の入力に対して前記周波数テーブルを参照して対応する基準周波数選択信号と出力指示信号を出力し、前記設定値対応テーブルを参照して対応する第1の増幅設定値、第2の増幅設定値、選択信号、分周比を出力する制御部とを有することを特徴とする請求項5乃至7のいずれか記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−172071(P2011−172071A)

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願番号】特願2010−34758(P2010−34758)

【出願日】平成22年2月19日(2010.2.19)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願日】平成22年2月19日(2010.2.19)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]