Fターム[5J106KK11]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507)

Fターム[5J106KK11]の下位に属するFターム

Fターム[5J106KK11]に分類される特許

1 - 20 / 47

圧電薄膜共振子、発振器及び時間標準器

発振回路およびそれを用いた電子機器

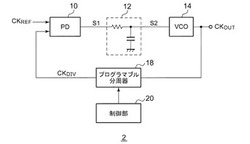

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

位相同期回路及び位相同期方法

【課題】低品質の入力光信号に対しても、安定して同期信号を発生するとともに、入力光信号が有するクロック信号に対する位相誤差検出感度を高くし、同期信号のタイミングジッタを低減し、製造コストを削減することである。

【解決手段】位相同期回路10は、基準信号を発生する基準信号発生部22と、入力光信号と電気信号とを位相比較して第1の位相誤差信号を生成する光位相比較部1と、第1の位相誤差信号と、基準信号と、を位相比較して第2の位相誤差信号を生成し、第2の位相誤差信号における入力光信号のクロック信号周波数に対応する周波数成分のみに応じて入力光信号の位相に同期した出力信号を発生して出力する位相同期部2と、基準信号の分周信号を用いて、位相同期部2から出力された同期信号をSSB変調して電気信号として光位相比較部1に出力する変調部3と、を備える。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ比較的低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40と、信号出力回路50とを含む構成とし、切替制御回路40は、遅延段回路10における各インバーター回路に対応する接続切替回路を1つずつ且つ周回して選択し、選択した接続切替回路SWからのみ遅延信号を出力するように制御すると共に、偶数番目に選択された接続切替回路SWからの遅延信号を反転して後段の回路に供給するように信号出力回路50を制御する。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、制御電圧によって遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40とを含む構成とし、切替制御回路40は、遅延段回路10における1つおきに且つ周回して順に並ぶ各インバーター回路に対応する接続切替回路を1つずつ選択し、選択した接続切替回路が、遅延信号を後段の回路に供給するように、その他の接続切替回路が遅延信号を後段の回路に供給しないようにする切替制御信号を生成し、これを各接続切替回路に供給する。

(もっと読む)

PLL回路及びチャージポンプ回路

【課題】簡単な構成でPLL回路がロック時にオフリーク電流が生じるのを低減することが可能なチャージポンプ回路及びそのチャージポンプ回路を用いたPLL回路を提供することを課題とする。

【解決手段】P型トランジスタMP1及びN型トランジスタMN1と並列に常にオフにしたP型トランジスタMP2及びN型トランジスタMN2を設ける。P型トランジスタMP1とN型トランジスタMN2が共にOFFのときオフリーク電流はP型トランジスタMP2及びN型トランジスタMN2を介して逃げる。また常にオフにしたP型トランジスタMP2及びN型トランジスタMN2の代りに動的にオン/オフを切替えるP型トランジスタやN型トランジスタを設けたり、P型トランジスタMP1及びN型トランジスタMN1のオフ抵抗と同じ抵抗値の抵抗器を設けても良い。

(もっと読む)

測定装置、再生装置、測定方法

【課題】PLL回路をより的確に評価できるPLL性能測定装置を提供する。

【解決手段】フェーズロックドループ回路にて検出される位相誤差についての移動平均を求める。この移動平均と閾値との比較に基づいて、フェーズロックドループ回路がロック状態に収束したか否かの判定を行う。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

ループ設定調整回路

【課題】ループ回路において、フィードバック遅延やPVT変動を自動的に検出して、ループ設定を調整し最適化することができるループ設定調整回路を提供する。

【解決手段】ループ設定調整回路は、クロックツリーシンセシスがフィードバック経路に挿入されたループ回路のループ特性を決定するループ設定を調整する。ループ設定調整回路は、クロックツリーシンセシスによる遅延時間を検出する検出回路と、検出回路によって検出される遅延時間に相当する時間、遅延時間よりも短い周期の発振クロックを出力する発振回路と、発振回路から出力される発振クロックのクロック数をカウントし、カウント値に対応する制御信号を出力する制御回路とを有し、制御回路から出力される制御信号により、クロックツリーシンセシスによる遅延時間に応じて、ループ設定を調整する。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部とを有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記分周信号の周波数と前記基準信号の周波数とを比較し、前記分周信号の周波数が前記基準信号の周波数に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

無信号検出回路およびそれを用いたPLL回路

【課題】簡易な構成で迅速に水平同期信号の有無を検出する。

【解決手段】無信号検出回路は、水平同期信号の無信号状態を検出する。無信号検出回路は、期間設定部と、検出部とを備える。期間設定部は、水平同期信号がオン期間であると予測される期間を少なくとも含む検出期間を、水晶クロック信号を用いて水平同期信号の1周期毎に設定する。検出部は、検出期間において水平同期信号がオンとなっていない場合、水平同期信号が無信号状態であると検出する。

(もっと読む)

受信回路

【課題】入力データに位相を合わせたクロック信号を安定的かつ低消費電力で得る受信回路を提供する。

【解決手段】受信回路において、制御回路30、発振回路40、分周回路50、フリップフロップ回路、第1および第2の位相比較回路などを備え、発振回路40の発振周波数は、入力データに信号情報が有る時にはクロック信号と入力データの位相比較結果に基づいて制御し、入力データに信号情報が無い時にはクロック信号を分周して得たフィードバック信号と一定の周期で変化するリファレンス信号の位相比較結果に基づいて制御する。発振回路40は、2系統の制御信号によって発振周波数を制御でき、一方の系統の制御信号の変化に対しては徐々にかつ大きく発振周波数が変化し、他方の系統の制御信号の変化に対しては直ちにかつ小さく(少しだけ)発振周波数が変化するように構成する。

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

CDR回路

【課題】製造のばらつきや環境変化あるいは入力データのパルス幅歪に対して強い耐性を持つCDR回路を提供する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、周波数制御信号に応じて発振周波数が制御されかつゲーティング回路2の出力パルスにより発振位相が制御される再生クロックを生成するゲーテッドVCO3と、入力データを遅延させる遅延回路4と、遅延回路4を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。遅延回路4は、ゲーティング回路2と同じ構成の遅延回路であるレプリカ回路40と、ゲーテッドVCO3と同じ構成の遅延回路であるレプリカ回路41とから構成される。

(もっと読む)

1 - 20 / 47

[ Back to top ]