Fターム[5J106KK22]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | ノイズ除去 (517)

Fターム[5J106KK22]の下位に属するFターム

Fターム[5J106KK22]に分類される特許

1 - 20 / 111

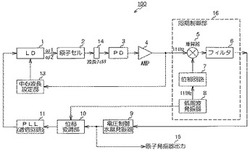

原子発振器

【課題】キャリア光を帯域通過フィルタによって減衰させて、信号検出のS/Nを改善して周波数安定度を高めた原子発振器を提供する。

【解決手段】の原子発振器100は、半導体レーザーにより構成されるLD(光源)1と、LD1に直流電流を与え、LD1の波長を所定の値に設定する中心波長設定部13と、アルカリ金属が封止された原子セル2と、アルカリ金属原子を透過したキャリア光(ωc)と共に第1の共鳴光(ω1)、及び第2の共鳴光(ω2)のうちいずれか一方の光を減衰させる波長フィルタ14と、波長フィルタ14を通過した原子セル2の透過光を検出するPD(光検出器)3と、を備えて構成される。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

電流−モード利得分割デュアル−パスVCO

【課題】大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術の提供。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

(もっと読む)

小数点分周PLL回路および集積回路

【課題】ループフィルタのカットオフ周波数を低く設定することなく、スプリアスを抑制する。

【解決手段】基準発振器で生成された基準周波数を所定の基準クロックに分周する第1の分周器103と、電圧制御発振器で生成された発振周波数を所定の帰還クロックに小数点分周する第2の分周器105と、基準クロックと帰還クロックとの位相を比較する位相比較器106と、位相比較器106による比較結果に基づいて電圧制御発振器の発振周波数を制御するチャージポンプ107と、を備えた小数点分周PLL回路1において、第1の分周器103側の電源パッド1−2と、第2の分周器105側の電源パッド1−1と、位相比較器106側の電源パッド1−3と、チャージポンプ107側の電源パッド1−4とを、それぞれ別個に備える。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

全デジタル位相ロックループ

【課題】周波数差の変化を正しくDCOに伝達し、且つグリッチノイズを低減する。

【解決手段】一つの実施形態の全デジタル位相ロックループ90には、デジタル周波数比較器1、グリッチ発生期間検出回路2、グリッチ補正回路3、累積器4、ループフィルタ5、及びDCO6が設けられる。デジタル周波数比較器1には、整数部周波数差生成回路11、小数部周波数差生成回路12、及び加算器13が設けられる。グリッチ発生期間検出回路2は、小数部周波数差生成回路12から出力されるTDC出力信号Stdcoが入力され、グリッチ発生期間信号Sgctimを生成する。グリッチ補正回路3は、加算器13から出力される周波数差信号Sfdif及びグリッチ発生期間信号Sgctimが入力され、グリッチ発生期間信号Sgctimがイネーブル状態のときに周波数差信号Sfdifに含まれるグリッチノイズを低減処理する。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

原子発振器

【課題】光検出器で吸収される光のレベルを高めてS/Nを改善した原子発振器を提供す

る。

【解決手段】この原子発振器50は大きく分けると、アルカリ金属原子と該アルカリ金属

原子の同位体とを混合した気体を封入したセル2と、可干渉性(コヒーレント性)を有し

、1つの中心周波数に対して2つの異なる周波数成分を有する第1の共鳴光対と第2の共

鳴光対を含む複数の光を気体に照射する光源(LD)1と、気体を透過した光の強度に応

じた検出信号を生成する光検出部(PD)3と、検出信号の強度に基づいて、アルカリ金

属原子に電磁誘起透過現象(以下、EIT現象と呼ぶ)を生起させるように第1の共鳴光

対の周波数を制御すると共に、アルカリ金属原子の同位体にEIT現象を生起させるよう

に、第2の共鳴光対の周波数を制御する周波数制御部12と、を備えて構成されている。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

PLL周波数シンセサイザ

【課題】デジタル制御発振器の周波数を安定して制御する。

【解決手段】PLL周波数シンセサイザ(101)は、基準クロック信号とPLL周波数シンセサイザの出力信号との位相差を検出する位相比較器(2)と、位相差に応じた整数値および小数値の和からなる制御値を出力するループフィルタ(4)と、第1のクロック信号に同期して、整数値に相当する第1のデジタル制御信号を出力する周波数制御部(6)と、第1のクロック信号よりも高い周波数の第2のクロック信号に同期して、平均値として小数値を表す第2のデジタル制御信号を出力する周波数制御部(7)であって、当該PLL周波数シンセサイザがロック状態にあるとき、第2のデジタル制御信号の取り得る値の範囲をロック時の範囲に制限する周波数制御部と、第1および第2のデジタル制御信号によるそれぞれの周波数制御の組み合わせに応じた周波数で発振するデジタル制御発振器(10)とを備えている。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

【課題】フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)の提供。

【解決手段】二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

1 - 20 / 111

[ Back to top ]