Fターム[5J106KK24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | ノイズ除去 (517) | 内部ノイズ (82)

Fターム[5J106KK24]に分類される特許

1 - 20 / 82

PLL回路

【課題】本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

(もっと読む)

画像処理装置

【課題】スペクトラム拡散クロックを画像データにより変調した信号を用いて画像を描画する場合に、スペクトラム拡散クロックの生成に用いる変調信号の周期性が画像に与える影響を小さくする。

【解決手段】画像形成装置は水平同期信号として機能するBD信号を生成するBD信号生成部と、スペクトラム拡散クロックCLK2を生成するクロック生成部301とを備える。クロック生成部301はPLL回路に変調信号生成部41を加えた構成を有する。変調信号生成部41は変調信号SG1の周期T1とBD信号の周期T2とが下記式を満たす変調信号SG1を生成する。

T2=T1×(n+0.5)

nは正の整数

(もっと読む)

高周波発振源

【課題】位相雑音の劣化を抑制することができる高周波発振源を得ることを目的とする。

【解決手段】所定の周波数で発振する基準発振器1と、その基準発振器の出力波が注入されていない場合の発振周波数が、その基準発振器の出力波の周波数の整数倍に設定されている(または設定される)注入同期発振器とを備え、その基準発振器から注入同期発振器に注入される電力を、注入同期発振器の低離調周波数の位相雑音が基準発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように、かつ高離調周波数の位相雑音が注入電力がない時の注入同期発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように適切な注入電力とする電力調整手段を設ける。

(もっと読む)

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

無線通信装置

【課題】無線通信装置の変調精度の低下を抑制しつつ、スプリアスによる受信特性の低下を抑制する。

【解決手段】デジタル部2は、アナログ部1にて周波数変換された受信信号の復調処理を行う。PLL回路25は、前記デジタル部のクロックを発生する。PLL設定変更部24は、現在の通信状態が受信状態であり、チャネル周波数内にスプリアスが存在し、受信電力が閾値に満たない場合、クロックCKのジッタを増加させ、それ以外の場合、クロックCKのジッタを通常設定にする。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

無線通信のエミッション抑制のための送信元、方法及び位相同期回路

【課題】送信機の出力スペクトルをフィルタリングするための効率的な方法及びシステムを提供する。

【解決手段】本明細書に開示する方法は、位相同期回路の出力を位相同期回路の入力で受け取った信号と同期させることを備える。方法は、更に、位相同期回路の第1利得及び第1抵抗の内の少なくとも1つを、潜在的に問題のあるチャネルにおける通信に適用することによって、潜在的に問題のあるチャネルにおけるエミッションを抑制することを備え、第1利得及び第1抵抗の内の少なくとも1つは、潜在的に問題のあるチャネル以外のチャネルにおける通信に適用される第2利得及び第2抵抗とは異なっている。

(もっと読む)

PLL回路

【課題】ロックアップタイムの高速化とリファレンスリークの低減化をとバランス良く達成する。

【解決手段】電圧制御発振器(104)の制御電圧VCONTをアナログ/デジタル変換して得られるデジタル信号(ADCO)を出力するアナログ/デジタル変換回路(106)と、基準クロック信号(FREF)と帰還クロック信号(FDIV)とがロックしたことを検出した時にロック検出信号(S201)を出力するロック検出部(201)と、ロック検出部からロック検出信号が入力された時にアナログ/デジタル変換回路から入力されたロック時デジタル信号を保持する保持部(107)と、保持部に保持されたロック時デジタル信号とアナログ/デジタル変換回路から出力されたデジタル信号との比較結果に基づいてチャージポンプ電流の電流量を段階的に減少させるチャージポンプ電流量制御信号(CPCONT)を生成するチャージポンプ制御部(108)と、を備えるPLL回路。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

イオントラップ型周波数標準器及び出力周波数安定化方法

【課題】PMTの暗電流を低減し、背景雑音を低減できるイオントラップ型周波数標準器を提供することを目的とする。

【解決手段】イオントラップ型周波数標準器303は、容器17内の水銀イオン102を光ポンピングして水銀イオン102を基底状態の下準位へ集める光ポンピング手段15と、電磁波を照射して、基底状態の下準位に集まった水銀イオン103を上準位へ遷移させる電磁波照射手段13と、水銀イオン103が励起状態を経由して再び基底状態へ戻る際に放射される蛍光23の光強度を測定する受光手段14と、蛍光23の光強度が最大となるように電磁波の周波数を調整する制御手段と、電磁波照射手段13が照射する電磁波の周波数を出力周波数として出力する出力手段と、受光手段14の光電面を冷却する冷却手段31と、を備える。

(もっと読む)

チャージポンプ回路、PLL回路及び電子回路装置

【課題】寄生容量(浮遊容量)の影響を抑制し、制御信号の電圧変動を抑えることで、リファレンスリークや妨害スプリアスを少なくすることが可能なチャージポンプ回路を提供する。

【解決手段】本実施形態のチャージポンプ回路は、セレクタ手段SEL1は、主定電流源I1_mainと主定電流源I2_mainまたは副電流源I2_subとを接続させ、かつ、主定電流源I2_mainと主定電流源I1_mainまたは副電流源I1_subとを接続させるよう接続状態を選択し、主定電流源I1_main及びI2_mainを常時他の電流源と接続させる。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有することが可能なPLL回路等を提供すること。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

位相調整装置及び方法

【課題】CCDを駆動するクロック信号を自動的に最適な位相に調整し、CCDからクロック信号成分が出力されない位相調整装置及び方法を提供する。

【解決手段】本発明の位相調整装置は、2相駆動型の電荷結合素子を用いたフィルタ回路に入力する第1の信号及び第2の信号の位相関係を調整する位相調整装置において、第1の信号に対して遅延を与える遅延付与手段と、遅延付与手段により遅延が与えられた第1の信号と、第2の信号とを加算又は減算する合成手段と、合成手段から出力する参照信号の電力値に基づいて、第1の信号と第2の信号とが逆位相となるように遅延付与手段の遅延設定量を制御する位相調整制御手段とを備えることを特徴とする。

(もっと読む)

無線周波数集積回路

【課題】無線周波数集積回路において位相エラーを十分に低減する。

【解決手段】無線周波数集積回路は、与えられた電圧に応じた発振周波数の発振周波数信号を生成する電圧制御発振器を有し、発振周波数信号を分周して得られる搬送波に信号波を乗せた無線周波数信号を生成する送信部と、無線周波数回路からの前記無線周波数信号を増幅する電力増幅器と電力増幅器から送信部に回り込む、少なくとも前記発振周波数の同じ周波数の高調波成分を低減する低減手段と、

を有する。

(もっと読む)

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

PLL回路

【課題】本発明の課題は、PLL回路のリファレンスリークと位相雑音を低減することである。

【解決手段】チャージポンプ回路14は、ロック状態監視回路19から出力される、PLL回路11がロック状態か否かを示す信号に基づいてチャージポンプ電流を切り換える。PLL回路11がアンロック状態のときには、第1及び第2の電流供給回路からチャージポンプ電流を供給し、ロック状態となると、第2の電流供給回路からのみチャージポンプ電流を供給する。

(もっと読む)

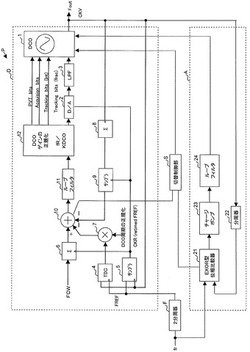

調整された対称的な負荷を有する電流制御発振器

改善された電源除去比(PSRR)を有する電流制御発振器(ICO)のためのバイアス回路を組み入れた集積回路が説明される。ICOのためのバイアス回路は、2つのエラー増幅器を含んでいる。第1のエラー増幅器は、グラウンド電源(GND)に関連するバイアス電圧VBNを調整する。第2のエラー増幅器は、ポジティブ電源(VDD)に関連するバイアス電圧VBPを調整する。VBP及びVBNバイアス電圧は、VDD及びGNDに注入されるノイズに対して、コンベンショナルなICOバイアス回路よりも改善されたPSRRを有する。  (もっと読む)

(もっと読む)

1 - 20 / 82

[ Back to top ]