Fターム[5J106KK27]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 耐ノイズ性向上 (37)

Fターム[5J106KK27]に分類される特許

1 - 20 / 37

集積回路

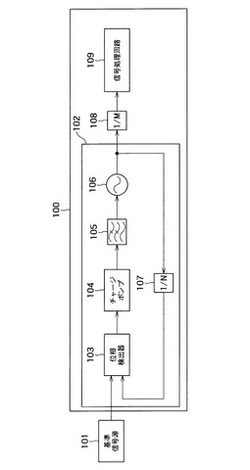

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

小数点分周PLL回路および集積回路

【課題】ループフィルタのカットオフ周波数を低く設定することなく、スプリアスを抑制する。

【解決手段】基準発振器で生成された基準周波数を所定の基準クロックに分周する第1の分周器103と、電圧制御発振器で生成された発振周波数を所定の帰還クロックに小数点分周する第2の分周器105と、基準クロックと帰還クロックとの位相を比較する位相比較器106と、位相比較器106による比較結果に基づいて電圧制御発振器の発振周波数を制御するチャージポンプ107と、を備えた小数点分周PLL回路1において、第1の分周器103側の電源パッド1−2と、第2の分周器105側の電源パッド1−1と、位相比較器106側の電源パッド1−3と、チャージポンプ107側の電源パッド1−4とを、それぞれ別個に備える。

(もっと読む)

原子発振器

【課題】光検出器で吸収される光のレベルを高めてS/Nを改善した原子発振器を提供す

る。

【解決手段】この原子発振器50は大きく分けると、アルカリ金属原子と該アルカリ金属

原子の同位体とを混合した気体を封入したセル2と、可干渉性(コヒーレント性)を有し

、1つの中心周波数に対して2つの異なる周波数成分を有する第1の共鳴光対と第2の共

鳴光対を含む複数の光を気体に照射する光源(LD)1と、気体を透過した光の強度に応

じた検出信号を生成する光検出部(PD)3と、検出信号の強度に基づいて、アルカリ金

属原子に電磁誘起透過現象(以下、EIT現象と呼ぶ)を生起させるように第1の共鳴光

対の周波数を制御すると共に、アルカリ金属原子の同位体にEIT現象を生起させるよう

に、第2の共鳴光対の周波数を制御する周波数制御部12と、を備えて構成されている。

(もっと読む)

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

クロック信号を生成できる、または各トランシーバに関連付けられたデジタル・システムのデータのバイパスを可能にする、電力管理されたトランシーバのネットワークを使用する通信システム

【課題】感知回路の雑音感受性を最小にするとともに、回路の少なくとも一部に対する電力を管理して、消費電力を少なくした通信システムを提供する。

【解決手段】通信システムはノードのセットを含む。各ノードはトランシーバ・インターフェイスとデジタル・システムを含む。トランシーバは、通信回線とデジタル・システムとの間に結合されており、伝送フォーマットおよび/または伝送プロトコルを対応するノード内の1つまたは複数のデジタル・システムにより認識されるビットのシーケンスに修正する。トランシーバは、デジタル・システムを支持する回路基板から分離された1つまたは複数のモノリシック回路基板に配置される。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

原子発振器

【課題】ノイズに強く誤検出の可能性が極めて低い原子発振器を提供する。

【解決手段】各共鳴光を出射するコヒーレント光源1と、コヒーレント光源1の中心波長

を制御する中心波長可変手段4と、コヒーレント光源1の中心波長に変調を加えるサイド

バンド発生手段5と、コヒーレント光源1からの光の波長により光の吸収量を変化させる

ガスセル2と、ガスセル2から透過する光を検出する光検出手段3と、コヒーレント光源

1に変調がかかっていない状態で光検出手段3の出力を監視する吸収検出手段6と、光検

出手段3の出力を同期検波してEIT状態を検出するEIT検出手段7と、吸収検出手段

6により検出された光検出手段3の出力レベルに基づいて、中心波長可変手段4の中心波

長を設定し、EIT検出手段7により検出した周波数成分のレベルに基づいてサイドバン

ド発生手段5の出力周波数を制御する信号処理手段8と、を備えて構成されている。

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】PLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づき基準信号の位相及び/又は発振周波数を制御するVCXOと、タイミング位相ベクトル信号の位相及び位相差に基づき制御係数を出力する2次PLL回路とを備える。この2次PLL回路は、タイミング位相ベクトル信号に基づき制御係数を発生する制御係数発生回路と、制御計数発生回路からの制御係数につき6dB単位での対数軸上におけるレベル調整を行う第1のレベル調整回路と、第1のレベル調整回路からの制御係数について±6dBレベルの微調整を行う第2のレベル調整回路とを有する。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】各種大振幅雑音、伝送路ロスの増大、雑音レベルの増大が発生するような大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】このPLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づいて基準信号の位相及び/又は発振周波数を制御するVCXOと、抽出されたタイミング位相ベクトル信号の位相又は位相差に基づいて基準信号の位相及び/又は発振周波数を制御するための制御係数を出力する2次PLL回路102とを備えている。この2次PLL回路102は、抽出されたタイミング位相ベクトル信号について対数軸上で位相検出を行うとともに、対数軸上で制御係数を発生する制御係数発生回路111を有している。

(もっと読む)

位相同期回路

【課題】 中心周波数を変更することなく、外部クロック信号の周波数特性のバラツキにより広く対応でき、周波数特性の安定性向上を図ることができる位相同期回路を提供する。

【解決手段】 外部クロック信号Siを第1入力信号S1、出力クロック信号Soまたはその分周信号を第2入力信号S2とし、これらの位相差に応じた電圧の位相差検出信号Sdを出力する位相比較回路11と、位相差検出信号Sdの所定帯域の信号成分から位相差に応じた電圧値の発振制御信号Sfを出力するループフィルタ12と、発振制御信号Sfの電圧値に応じた周波数で発振する出力クロック信号Soを出力する電圧制御発振回路13と、電圧制御発振回路13の第2入力信号S2がロック状態であるかアンロック状態であるかを検出するロック状態検出回路14を備え、ループフィルタ12が、ロック状態検出回路14におけるロック状態の検出結果に応じて、引き込み範囲を調整する。

(もっと読む)

マルチチャネル・データ検出システム用に構成された周波数エラー組み合わせ論理および周波数エラーを生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの周波数エラー組み合わせ論理を提供することにある。

【解決手段】 この周波数エラー組み合わせ論理は、各チャネルに関する周波数エラー情報を受信することと、受信周波数エラー情報を結合し、結合された位相エラーを生成し、各チャネルからの受信周波数エラー情報に重みを付けるように構成された組み合わせ論理と、結合された周波数エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された周波数エラー出力とを含む。

(もっと読む)

データ駆動回路及び遅延固定ループ

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず、正常に動作可能なデータ駆動回路及び遅延固定ループの提供。

【解決手段】第1のクロック信号の入力を受けて第2のクロック信号を出力する遅延固定ループにおいて、前記第1のクロック信号、前記第2のクロック信号及び少なくとも一つの遅延信号によって位相差信号-前記第1のクロック信号又は前記第2のクロック信号によって前記第1のクロック信号と前記第2のクロック信号の間の位相差に該当する値を有し、前記少なくとも一つの遅延信号によって位相差無しに該当する値を有する-を出力する位相検出器21と、前記第1のクロック信号を遅延させることにより前記第2のクロック信号及び前記少なくとも一つの遅延信号を求める遅延線23-前記第1のクロック信号に対する前記第2のクロック信号の遅延は前記位相差信号により変更される-と、を備える。

(もっと読む)

半導体装置

【課題】測定に係わるノイズの影響を軽減し、制御電圧の測定精度向上させることが出来る。

【解決手段】PLL回路15と、ボルテージフォロワ19と、出力端子23と、を備え、PLL回路15中の電圧制御発振回路の制御電圧V1をボルテージフォロワ19を介して出力端子23に出力する。

(もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

信号処理システム、記録情報再生システムおよび信号受信システム

【課題】製造コスト上昇を抑える。

【解決手段】信号処理システムであって、制御端子に与えられた制御信号に応じた遅延を、入力端子に入力された信号に与えて出力端子から出力する第1の遅延回路と、前記第1の遅延回路と同様に構成され、入力端子と出力端子とが接続された第2の遅延回路を有し、発振信号を出力する発振器と、前記発振器の発振信号に応じた信号と基準となる信号との間の位相を比較し、比較結果を示す信号を出力する位相比較回路と、前記位相比較回路の出力信号の低周波成分を、前記第1及び第2の遅延回路の制御信号として用いられるように出力するフィルタ回路とを有する。前記第1の遅延回路の入力端子に与えられ、その出力端子から出力された遅延した信号が、前記基準となる信号として前記位相比較回路に与えられている。

(もっと読む)

デジタル制御発振器、このデジタル制御発振器を備えた位相同期ループ及び通信機

【課題】スプリアスが生じにくい。

【解決手段】ADCから入力されたnビットのデジタル信号は、mビットが整数部41、且つ、n−mビットがデジタル制御値時間変化部43に入力される。そして、デジタル制御値時間変化部43から時間的に変化するデジタル制御値が小数部42に入力される。デジタル制御発振器4は、整数部41によってステップ周波数刻みで発振周波数を変化させる。また、小数部42によってステップ周波数よりも小さな周波数刻みで発振周波数を変化させる。このとき、小数部42によって変化させることができる周波数は、ステップ周波数よりも大きい。

(もっと読む)

1 - 20 / 37

[ Back to top ]