Fターム[5J106KK12]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 動作、特性の安定化 (735)

Fターム[5J106KK12]の下位に属するFターム

Fターム[5J106KK12]に分類される特許

1 - 20 / 326

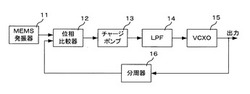

高安定発振器

【課題】小型化が容易であり、低コストで製造可能であって、発振出力周波数における短期安定度と長期安定度とを両立させた高安定発振器を提供する。

【解決手段】一定の周波数の信号を出力する高安定発振器は、出力発振器として電圧制御型水晶発振器15を備えるPLL回路と、MEMS振動子を有するMEMS発振器11と、を備える。MEMS発振器11の出力を基準信号としてPLL回路の位相比較器12に供給する。MEMS発振器11によって出力周波数の長期安定度が維持され、電圧制御型水晶発振器15によって出力周波数の短期安定度が維持されるようにする。

(もっと読む)

バーストクロック発生回路

【課題】バーストクロック信号を安定に生成できるバーストクロック発生回路を提供する。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

(もっと読む)

半導体装置及びこれを搭載する無線通信端末

【課題】回路規模の増大を抑止しつつ、ループ帯域の切替に際して生じるオフセットを補償する。

【解決手段】半導体装置(110)を構成する位相検出器(111)は、発振器(114)の出力信号を帰還した帰還信号と参照信号との間の位相差を検出し、位相差に応じた値を示す位相差値を生成する。増幅器(112)は、外部からの制御信号に応じて決定される増幅率で、位相差値を増幅する。フィルタ(113)は、増幅器(112)の出力値を平滑化する。発振器(114)は、フィルタ(113)の出力値に応じて、出力信号の周波数を制御する。

(もっと読む)

半導体装置、受信機、送信機、送受信機及び通信システム

【課題】周波数誤差に基づく送信クロックを生成し、送信データに対して任意にSSCの適用が選択可能な半導体装置が、望まれる。

【解決手段】半導体装置は、受信信号を入力し、動作クロック信号に基づいて受信信号からクロック信号とデータ信号を取り出すクロックアンドデータリカバリ部と、受信信号から取り出したクロック信号と動作クロック信号との周波数誤差信号を求める周波数誤差調整部と、周波数誤差信号を記憶する周波数誤差信号記憶部と、周波数誤差信号に基づいて動作クロック信号の周波数を制御する動作クロック生成部と、周波数誤差信号記憶部が記憶する周波数誤差信号の値に基づいて、動作クロック生成部が生成する動作クロック信号をスペクトラム拡散させて変動させるSSCG部と、を備えている。

(もっと読む)

同期ネットワークデバイス

【課題】物理層デバイスおよび同期デバイスの複数のポート間でクロックを同期させる方法を提供する。

【解決手段】制御方法は、グランドマスタークロックのソースとなるポートを選択するステップを含む(302)。選択されたポートは、リンク先からの送信に基づいてグランドマスタークロックを再生する。マルチポートPHY ICは、グランドマスターソースポートのRX_CLKを出力する(304)。グランドマスターソースポートのTX_CLKは、ローカルオシレータから取得される(306)。そして、ほかの全てのポートのTX_CLKは、クロック同期部の出力から取得される(308)。クロック同期部は、グランドマスターソースポートを有するマルチポートPHY ICからの再生クロックに基づいて同期させる(310)。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

集積回路

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

遅延回路、DLL回路、および半導体装置

【課題】 段数切替型の遅延回路において、段数切替時に発生するハザードを抑制する。

【解決手段】 本発明の段数切替型の遅延回路は、段数切替前後で遅延回路の内部ノードの論理状態が変化しないように、遅延のための経路として選択されていない段に遅延回路の入力が接続されている。これにより、遅延回路のハザードの発生を抑制することができ、ひいては遅延回路を備えるDLL回路や半導体装置の論理規模を低減でき、低消費電力化に寄与し、また、半導体装置の処理速度を向上させることができる。

(もっと読む)

原子発振器及び原子発振器の製造方法

【課題】安定度の高い原子発振器を提供する。

【解決手段】アルカリ金属が封入されたアルカリ金属セルと、前記アルカリ金属セルにレーザ光を照射する光源と、前記アルカリ金属セルを透過した光を検出する光検出器と、を有する原子発振器において、前記アルカリ金属セルは、一方の面から他方の面に貫通する開口部が形成された基板の他方の面にガラス基板が接合された一方の部材と、一方の面から他方の面に貫通する開口部が形成された基板の他方の面にガラス基板が接合された他方の部材と、前記一方の部材における基板の一方の面と、前記他方の部材における基板の一方の面とを直接接合することにより、前記一方の部材の開口部及び前記他方の部材の開口部により形成されるセル内部と、前記セル内部に封入されるアルカリ金属原料と、を有するものであることを特徴とする原子発振器を提供することにより上記課題を解決する。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

制御装置、光受信装置および制御方法

【課題】特性の制御を安定させること。

【解決手段】制御装置120は、第1演算器122と、更新制御回路123と、取得部125と、第2演算器126と、を備えている。第1演算器122は、処理装置の第1特性の検出結果に基づいて、第1特性を変化させる処理装置のパラメータを操作する。更新制御回路123は、第1演算器122の機能を更新する場合に、第1演算器122によるパラメータの操作を停止させる。取得部125は、パラメータの操作量と、第1特性を変化させる処理装置の第2特性の変化量との関係を示す関係情報を取得する。第2演算器126は、更新制御回路123によって第1演算器122によるパラメータの操作が停止している場合に、取得部125によって取得された関係情報と、第2特性の検出結果の変化量と、に基づく操作量によってパラメータを操作する。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

【課題】デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作を提供する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

(もっと読む)

モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

周波数推定方法、広帯域周波数弁別器及び無線位置測定用受信機

【課題】 サンプリング周波数の2倍の周波数における回転因子の集合に対応する、DFT演算子と1/2DFT演算子の組み合わせにもとづく周波数弁別器である。

【解決手段】 周波数弁別器は、ゼロ又は不連続点を持たないように選定される。そのため、この発明の弁別器は、拡張された動作範囲において、より安定的かつ良好に動作する。この発明の弁別器は、GPS受信機に適用された場合、初めに大きな誤差が有っても、より確実にキャリヤ周波数にロックすることが可能であるとともに、誤ってロックする問題を防止するものである。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

1 - 20 / 326

[ Back to top ]