Fターム[5J106KK17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 動作、特性の安定化 (735) | 出力位相 (61)

Fターム[5J106KK17]に分類される特許

1 - 20 / 61

半導体装置

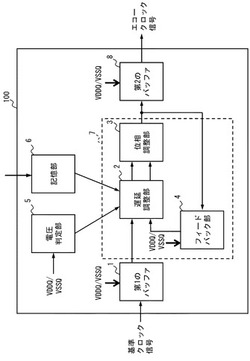

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

注入同期発振装置

【課題】位相雑音を改善する注入同期発振装置を得る。

【解決手段】基準発振器1の出力波を所定の電力に調整する電力調整手段2と、電力調整された電波を分配する同相分配手段3と、分配された電波が各々入力され、入力される周波数の自然数倍の周波数で発振する複数の注入同期発振器4と、複数の注入同期発振器4の各々の出力を合成して出力する同相合成手段5とを備えた。

低離調周波数では、注入同期発振器4の出力波が、低離調周波数で位相雑音特性が良い基準発振器1の出力波に同期するので、位相雑音が改善される。一方、高離調周波数では、各々の注入同期発振器4の出力波の位相雑音が無相関のため、同相合成手段5により各々の注入同期発振器4の出力波を合成することで、位相雑音が改善される。

したがって、低離調周波数および高離調周波数の全離調周波数において位相雑音を改善することができる。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

同期回路

【課題】基準信号に異常が発生した場合でも大きな位相ずれ量が発生しない同期信号(タイミング信号)を出力する同期回路を提供する。

【解決手段】同期回路1は、発振器クロック信号を発生する電圧制御発振器16と、第1の基準クロック信号及び第2の基準クロック信号を含む複数の基準クロック信号と前記発振器クロック信号との間のそれぞれの位相ずれ量を検出する位相ずれ量検出部12と、前記複数の基準クロック信号の状態に応じた制御信号に基づいて同期信号を出力する同期信号処理部13,14と、前記同期信号と前記発振器クロック信号との間の位相ずれ量に応じて電圧制御発振器16のコントロール電圧を生成するコントロール電圧生成部15とを備える。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】位相雑音が小さい発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、位相シフト部と、複数の位相一致検出回路と、出力部とを備える。位相シフト部は、入力発振信号を遅延させて、位相が互いに異なる複数の遅延信号を生成する。複数の位相一致検出回路は、前記複数の遅延信号のそれぞれに対応して設けられ、参照信号と、対応する前記遅延信号との位相差が所定範囲内であるか否かを判定する。出力部は、前記位相差が所定範囲内であると判定された遅延信号に基づいて、出力発振信号を生成する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

多相信号を生成する方法及び回路

【課題】2つの結合されたLCVCOにおいて生じる多相クロック信号の位相誤差を改善し、制御可能な位相オフセットでクロック信号を生成する方法を提供する。

【解決手段】方法は、LCVCOによって第1のLCタンクの共振周波数に基づく第1の位相を有する第1の周期信号を生成するステップと、第2のLCVCOによって第2のLCタンクの共振周波数に基づく第2の位相を有する第2の周期信号を生成するステップと、第1及び第2の周期信号に基づいて第1及び第2のLCタンクの間の位相オフセットを決定するステップと、決定された位相オフセットに基づいて第1及び第2の出力信号を生成するステップと、所定の位相オフセットと略等しくなるよう位相オフセットを調整するステップとを有する。調整ステップは、第1の出力信号に基づいて第1のLCタンクの第1のインピーダンスを変調するステップ、及び/又は、第2の出力信号に基づいて第2のLCタンクの第2のインピーダンスを変調するステップを有する。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

PLL周波数シンセサイザ

【課題】デジタル制御発振器の周波数を安定して制御する。

【解決手段】PLL周波数シンセサイザ(101)は、基準クロック信号とPLL周波数シンセサイザの出力信号との位相差を検出する位相比較器(2)と、位相差に応じた整数値および小数値の和からなる制御値を出力するループフィルタ(4)と、第1のクロック信号に同期して、整数値に相当する第1のデジタル制御信号を出力する周波数制御部(6)と、第1のクロック信号よりも高い周波数の第2のクロック信号に同期して、平均値として小数値を表す第2のデジタル制御信号を出力する周波数制御部(7)であって、当該PLL周波数シンセサイザがロック状態にあるとき、第2のデジタル制御信号の取り得る値の範囲をロック時の範囲に制限する周波数制御部と、第1および第2のデジタル制御信号によるそれぞれの周波数制御の組み合わせに応じた周波数で発振するデジタル制御発振器(10)とを備えている。

(もっと読む)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

PLL/DLL用の高出力インピーダンスチャージポンプ

【課題】チャージポンプにおけるスタティック位相誤差を最小限にする。

【解決手段】位相ロックループ/遅延ロックループで使用するためのチャージポンプは、プルアップ回路とプルダウン回路と演算増幅器とを含む。チャージポンプはプルアップおよびプルダウン回路の動作に関連したスタティック位相誤差を最小限にするように設計される。演算増幅器の使用はまた、低電源電圧の影響を軽減する。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

1 - 20 / 61

[ Back to top ]