Fターム[5J106KK14]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 動作、特性の安定化 (735) | 電源補償 (40)

Fターム[5J106KK14]に分類される特許

1 - 20 / 40

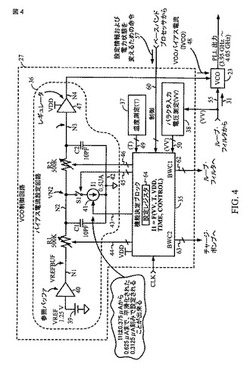

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

電圧電流変換回路及びこれを備えたPLL回路

【課題】電源電圧依存性が小さい電圧電流変換回路及びこれを備えたPLL回路を提供する。

【解決手段】電圧電流変換回路は、第1電圧が供給される第1導電型のトランジスタで構成され、第1電流に基づいて第2電流を生成するカレントミラー回路と、前記第1電流が流れる第2導電型の第1のトランジスタと、一端が前記第1のトランジスタのソースに接続され、他端に第2電圧が供給され、入力された制御電圧に応じて抵抗値が変化する可変抵抗と、前記第2電流が流れ、ドレインとゲートとが前記第1のトランジスタのゲートに接続され、ソースに前記第2電圧が供給され、ゲート幅Wとゲート長Lとの比W/Lが前記第1のトランジスタの比W/Lより小さい第2導電型の第2のトランジスタと、前記第1電流または前記第2電流に基づいて出力電流を出力する電流出力部と、を備える。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

PLL回路

【課題】低電圧動作が可能なPLL回路を提供する。

【解決手段】フィルタ用キャパシタの一端が入力される電圧制御発振器と、前記電圧制御発振器の出力が入力され、フィードバック信号を出力するn分周器と、基準信号と前記フィードバック信号との位相差に応じた電圧パルスを出力する位相周波数比較器と、前記電圧パルスに基づき、前記フィルタ用キャパシタを充放電するチャージポンプとを備え、前記チャージポンプは、前記フィルタ用キャパシタの一端に接続される充放電用容量を備える。

(もっと読む)

遅延固定ループ回路

【課題】外部電源電圧のレベル変動とは関係なく安定的に遅延固定動作を行う遅延固定ループ回路を提供する。

【解決手段】外部電源電圧のレベルを検出する電圧レベル検出部280と、ソースクロック及びフィードバッククロックの位相を比較する位相比較部200と、電圧レベル検出部280の出力信号に応じて、第1および第2遅延ユニット単位のうち何れか一方を開始遅延ユニット単位として、他方を連結遅延ユニット単位としてそれぞれ指定し、位相比較部200の出力信号に応答して、遅延量が、所定の遅延量までは前記開始遅延ユニット単位で、前記所定の遅延量以後には前記連結遅延ユニット単位で前記ソースクロックを遅延させ、遅延固定クロックDLLCLKとして出力するクロック遅延部220と、前記遅延固定クロックに前記ソースクロックの実際の遅延条件を反映して、前記フィードバッククロックとして出力する遅延複製モデル部240とを備える。

(もっと読む)

基準周波数発生装置

【課題】リファレンス信号が取得できなくなっても長時間にわたって高精度な基準周波数信号を出力可能で、使用温度範囲が広く、安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置11は、GPS受信機21と、PLL回路31と、検出器28と、記憶部29と、制御部22と、を備える。PLL回路31は、GPS受信機21からのリファレンス信号に基づいて得られた同期制御信号に基づき、デジタル制御発振器26を制御する。記憶部29には、同期制御信号の制御値と、そのときの電圧値及び温度と、の対応関係が記憶されている。リファレンス信号が得られない場合、制御部22は、前記対応関係と、検出器28が検出した電圧及び温度と、に基づいて自走制御信号を決定し、デジタル制御発振器26を制御する。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

信号分配装置

【課題】分周器の広帯域かつ低電圧動作を保障する。

【解決手段】信号分配装置は、第2制御信号に従って動作し、参照周波数に従って発振周波数を調整する調整部を有する位相同期ループ回路101と、電流源負荷を有し、前記調整部によって調整された発振周波数を分周してI/Q信号を生成する分周器102と、第1制御信号に従って自走発振周波数を生成する自走発振周波数生成器105と、前記参照周波数と前記自走発振周波数を比較する比較部103A及び前記比較部103Aの比較結果に従って前記第1制御信号又は前記第2制御信号を生成する制御部103Bを有する自走発振周波数制御回路103と、前記分周器102によって生成された前記I/Q信号を用いて送信又は受信を行う通信回路104と、を備えている。

(もっと読む)

位相補間器

【課題】プロセス条件、電源電圧、温度の変動によらず、微小な位相をプログラマブルに調整できる位相補間器を提供する。

【解決手段】PLL回路のフィードバック信号(FBCLK)に非等間隔なクロックを入力し、PLL回路が本来備える位相合せ機能により、基準信号REFCLKとフィードバック信号FBCLK間に微小な位相差を与え、かつ、アップ、ダウン電流が等しいチャージポンプ(CP)回路を用いてプロセス条件、電源電圧、温度依存性が無い位相差を実現する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

クロック位相シフト回路

【課題】プロセス条件、電源電圧、温度等の変動によらず、入力クロックの位相シフトの調整ができ、かつ、従来のDLL回路を用いた場合と比較して占有面積の小さいクロック位相シフト回路を提供する。

【解決手段】入力クロックを遅延させる遅延回路の遅延セルと同一の遅延セルで構成されたリングオシレータを用いて、入力クロックのm周期分の発振出力をカウントし、入力クロックの1周期分の遅延セル段数を計算して位相シフト量分の遅延セル段数を設定する。

(もっと読む)

シュミットトリガーを用いたオシレータ

【課題】温度および電圧などの周辺環境の変化に依存せずに常に一定の周波数を有する発振信号を出力する、シュミットトリガーを用いたオシレータを提供すること。

【解決手段】シュミットトリガーを用いたオシレータは、一定の大きさの電流を発生する定電流発生部310と、定電流発生部310が発生した電流をミラーリングする電流ミラーリング部330と、電流ミラーリング部330を介して印加される電流を供給および遮断するための制御部320と、制御部320から供給される電流を充電するキャパシタCと、キャパシタCに充電された電圧が印加されて、ハイまたはローレベルの電圧を出力するシュミットトリガー部340と、シュミットトリガー部340から出力された電圧を遅延して出力する電圧遅延部350と、を備える。

(もっと読む)

電圧生成回路及び発振装置

【課題】位相雑音特性が良好で、かつ低消費電力、小型化に適した発振装置を提供すること。

【解決手段】固定電圧Vrefが印加される第1の端子と、可変電圧Vcが印加される第2の端子と、前記第1の端子と前記第2の端子との間に直列接続された、抵抗値rのm個の抵抗器及び抵抗値RINの入力抵抗器と、前記m個の抵抗器のうちn個の抵抗器を選択するための複数のスイッチと、制御電圧を出力する第3の端子と、を有する抵抗切替部と、前記複数の抵抗器に流す定電流の電流値Ioffを設定し当該定電流を供給する電流供給部とから構成され、{Vref+n×r×[(VC−Vref)/(m×r+RIN)]}で与えられる第1の電圧と、{−(n×r×Ioff)}で与えられる第2の電圧との重ね合わせにより規定される第3の電圧を、前記第3の端子から制御電圧として出力する。

(もっと読む)

1 - 20 / 40

[ Back to top ]